アイメックにより出願された特許

31 - 40 / 302

抵抗メモリ素子および関連する制御方法

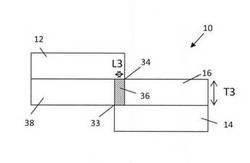

【課題】電圧制御されたプログラム可能な抵抗層を有する抵抗メモリ素子とプログラミング方法を提供する。

【解決手段】参照面に平行な面に横たわり、参照面上の垂直な投影で上部電極投影を有する上部電極素子12と、参照面に平行な面に横たわり、参照面上の垂直な投影で下部電極投影を有する下部電極素子14と、上部電極素子12と下部電極素子14との間に挿入された可変性の抵抗率を有する活性層16を含む抵抗メモリ素子10において、上部電極投影と下部電極投影との間にオーバーラップ領域L3があり、オーバーラップ領域L3は少なくとも上部電極投影のコーナーおよび/または少なくとも下部電極投影のコーナーを含み、オーバーラップ領域L3の面積は、参照面上の、上部電極素子12と下部電極素子14の全投影面積の10%以下を構成する。

(もっと読む)

フローティングゲート半導体メモリデバイスおよびそのようなデバイスの製造方法

【課題】NANDフラッシュメモリデバイスを電気的、物理的に小型化し、良好なデータ保持と電気的特性を備えたフローティングゲートデバイスを提供する。

【解決手段】フローティングゲートメモリデバイスの製造方法に関し、ベース基板100、埋め込み絶縁層、および単結晶半導体上部層から形成される、半導体−オン−絶縁体基板が提供される。トレンチが基板中に形成され、フローティングゲートとして働く単結晶上部部分を有する高層フィン型構造111−114を形成する。埋め込み絶縁層の一部は、フローティングゲートデバイスのトンネル酸化物層101’として働く。ゲート誘電体層160は、熱酸化により単結晶上部部分の側壁の上に形成され、薄い膜厚のゲート誘電体層を可能にする。

(もっと読む)

シリコン基板上にIII族窒化物材料を成長させるための方法及びそのための装置

【課題】シリコン基板上にIII族窒化物材料を成長させるための新規な方法を提供することを目的とする。

【解決手段】本発明は、ポーラス状の最上層を有するシリコン基板を含む基板と、

上記最上層上の、Ge材料からなる第2層と、

上記第2層上の、III族窒化物材料からなる別の層とを有する装置に関する。

さらに、本発明は、高品質のIII族窒化物層のエピタキシャル成長に非常に適した方法、中間層若しくはテンプレートデバイスに関する。

(もっと読む)

半導体材料の選択堆積方法

【課題】シリコンやゲルマニウムのようなIV族半導体材料を、半導体表面上に、絶縁表面上への堆積無しに選択的に堆積する方法を提供する。

【解決手段】半導体プロセスで半導体材料の選択成長を行う方法が、第1領域11と第2領域12とを含むパターニングされた基板10を提供する工程を含み、第1領域11は露出した第1半導体材料を含み、第2領域12は露出した絶縁材料を含む。この方法は、更に、第2半導体材料の前駆体、Cl化合物とは応性しないキャリアガス、および錫テトラクロライド(SnCl4)を供給することにより、第1領域の第1半導体材料の上に第2半導体材料の膜を選択的に形成する工程を含む。錫テトラクロライドは、第2領域の絶縁材料上への第2半導体材料の堆積を阻害する。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法を提供する。

【解決手段】第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。本発明の具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

部分的なバックコンタクト太陽電池の製造方法

【課題】プロセス工程の数が減らされて、これにより製造コストが低減され、良好な開回路電圧(open-circuit voltage)と良好な短絡回路電流(short-circuit current)を有し、この結果、良好なエネルギー変換効率を有する、部分的なバックコンタクトの製造方法を提供する。

【解決手段】シリコン基板2を提供する工程と、シリコン基板2の裏側に表面パッシベーション層3を堆積する工程と、表面パッシベーション層3とシリコン基板2との間の界面に薄い層に裂けた領域または泡1を形成する工程と、表面パッシベーション層3の上に金属層4を堆積する工程と、金属の焼成を行う工程とを含む。

(もっと読む)

ゲルマニウム層の直接成長方法

【課題】化学気相堆積により、基板上にGeの連続した層を堆積する方法を提供する。

【解決手段】非反応性キャリアガスと、高次のゲルマニウム前駆体ガス、即ちゲルマン(GeH4)より高次のゲルマニウム前駆体ガスとの混合物が適用される。好適には、約275℃と約500℃との間の堆積温度で堆積が行われ、混合物中の前駆体ガスの分圧は、約275℃と約285℃との間の温度で少なくとも20mTorrであり、約285℃と約500℃との間の温度で少なくとも10mTorrである。

(もっと読む)

n型ゲルマニウム上への低抵抗コンタクトの作製方法

【課題】n型Ge上に形成されるコンタクトの接触抵抗を低減する。

【解決手段】第1ドーパントレベルのn型ドーパントがドープされたゲルマニウム領域(10)を上部に有する半導体基板を得る工程と、n型ドープされたゲルマニウム領域(10)を覆う界面シリコン層(11)を形成する工程であって、界面シリコン層(11)は第2ドーピングレベルのn型ドーパントでドープされて臨界膜厚より大きな膜厚を有し、これにより界面シリコン層(11)は少なくとも部分的に緩和される工程と、界面シリコン層(11)を覆うように、1×10−2Ωcmより小さい電気抵抗率を有する材料の層(12、13)を形成する工程とを含む方法。本発明はまた、対応する半導体デバイスを提供する。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

正確に制御されたマスク陽極酸化のための方法

【課題】基板上の陽極酸化可能な層、例えば犠牲層上に存在するアルミニウム層であって、該犠牲層は、マイクロ電気機械システム又はナノ電気機械システム(MEMS/NEMS)を備えたキャビティから除去する必要があるような層のマスク陽極酸化の方法を提供する。

【解決手段】Al層の陽極酸化は、細長い孔の形成につながり、該孔を通じて犠牲層を除去可能である。本発明の方法に従って、Al層の陽極酸化は、陽極酸化される領域21を規定する第1マスク20、及び陽極酸化される第2領域を規定する第2マスク22であって、前記第2領域は第1領域を包囲するようなマスクの補助がある状態で行う。第1マスク及び第2マスクが規定する領域の陽極酸化は、第1領域周囲の閉環形態における陽極酸化構造の形成につながり、第1領域内では不要な横方向陽極酸化に対するバリアを形成する。

(もっと読む)

31 - 40 / 302

[ Back to top ]