アイメックにより出願された特許

81 - 90 / 302

ダブルゲートナノ構造FET

少なくとも1つのナノ構造を備えた電界効果トランジスタ(FET)半導体デバイスであって、少なくとも、2つの主面を有する、均一にドープされたビーム形状のナノ構造と、ナノ構造の各主面に設けられたゲート電極と、ダブルゲートナノ構造ピンチオフFETを形成するための、ナノ構造の各主面とゲート電極との間の絶縁層とを備えたデバイス。FETのピンチオフ電圧及び電流を独立して調整できることが、かかるFETの利点である。  (もっと読む)

(もっと読む)

表面洗浄方法及び装置

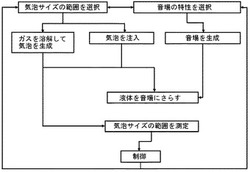

【課題】 巨大な音エネルギーだけでは気泡発生が効率的でない。

【解決手段】 この発明は過渡的なキャビテーションを生成するための方法に関し、液体中にさまざまな気泡サイズを持っている気泡を生成するステップと、音場を生成するステップと、および液体を音場にさらすステップとを備え、気泡サイズの範囲、および/または、音場の特性が互いにそれらを調整するように選択され、それにより、選択された範囲の気泡サイズにおいて過渡的なキャビテーションを制御することを特徴とする。この発明はこの方法を実行するのに適した装置にも関する。

(もっと読む)

マイクロエレクトロニクスデバイスの製造方法およびその方法によるデバイス

【課題】マイクロエレクトロニクスデバイス本体と封止層との静電容量結合が少なく、かつ短絡によるデバイスの故障がないマイクロエレクトロニクスデバイスの製造方法を提供する。

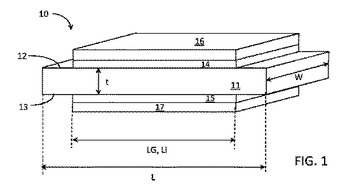

【解決手段】マイクロエレクトロニクスデバイスに含まれる封止されたキャビティ15を作製する方法であって、少なくともキャビティが形成される位置に犠牲層を形成する工程と、犠牲層の上に膜層12を堆積させる工程と、膜層12を少なくとも2つの分離された膜層ブロック121,122にパターニングする工程と、膜層12に設けた孔14を通して犠牲層を除去する工程と、膜層を酸化シリコン16,アルミニウム層17,ボンドパッド層19で封止することによりキャビティ15を封止する工程とを含み、膜層をパターニングする工程は、犠牲層の除去後に行われる。

(もっと読む)

太陽電池用ポリチオフェン系活性層

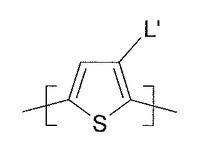

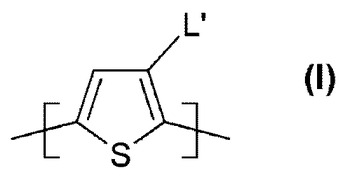

本発明は、新規モノマーおよびポリマーならびにそのようなポリマーと電子受容体を含むブレンドに関する。本発明は、(a)下記式:

〔式中、L’は、L−C(O)O−J、L−C(O)NR’−J、L−OCO−J’、L−NR’CO−J’、L−SCO−J’、L−O−J、L−S−J、L−Se−J、L−NR’−JおよびL−CN(式中、Lは、1〜10個の炭素原子を有する直鎖または分枝アルキレン基であり、Jは、水素原子または1〜4個の炭素原子を有する直鎖若しくは分枝アルキル基であり、J’は、フェニル構造を含む若しくはフェニル構造を含まない炭素数1〜10の飽和若しくは不飽和の、直鎖若しくは分枝の基であり、R’は、水素原子または1〜4個の炭素原子を有する直鎖または分枝アルキル基である〕

で示されるモノマー単位を含むポリマー、および、(b)フラーレン誘導体のような電子受容体を含む光起電装置において使用するためのブレンドに関する。  (もっと読む)

(もっと読む)

半導体素子の製造方法および半導体素子

【課題】MEMS、NEMSなどの半導体素子を封入する方法、および空隙を形成する方法、および関連した素子を提供する。

【解決手段】半導体素子を製造する方法は、非平坦な立体形状を有し、実質的な地形変動を含む主面を備えた基板を用意することと、上面および下面を有する第1キャップ層を主面の上に形成することとを含む。第1キャップ層の形成の際、第1キャップ層に局所欠陥が導入され、局所欠陥は、実質的な地形変動に対応した場所に位置決めされており、局所欠陥は、所定の流体が通過できるのに適している。

(もっと読む)

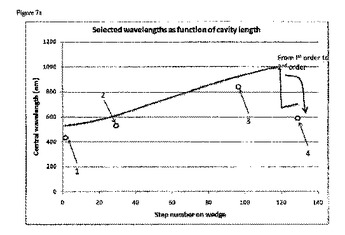

スペクトル・イメージングシステム用の集積回路

イメージングシステム用の集積回路が、光学センサアレイ(40)と、ある波長帯域を1つ又はそれ以上のセンサに向けて通過させるようにそれぞれ構成された光学フィルタアレイ(10)とを有する。光学フィルタアレイは、センサアレイと一体化されている。集積回路は、センサアレイから画素値を読み出して画像を表現する読み出し回路(30)を有する。光学フィルタの異なるものが異なる厚さを有するように構成され、干渉を用いて異なる波長帯域を通過させて、波長スペクトルの検出を可能にしている。読み出し回路は、1つの光学フィルタ下にある複数の画素が並列で読み出し可能である。厚さは、アレイ全体で非単調的に変化してもよい。読み出しまたは後の画像処理は、厚さ誤差を補償するために、スペクトルのサンプリングまたはシフト(shift)を実行する波長間の選択または補間(interpolation)を含んでもよい。  (もっと読む)

(もっと読む)

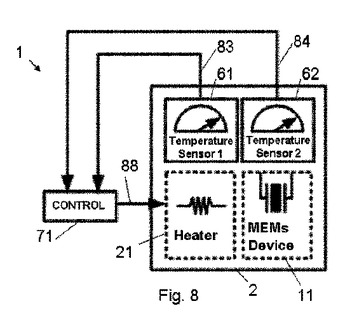

集積電気部品用2重センサ温度安定化

恒温槽に設けられ、予め規定した温度(Tset)で、集積電気部品の温度(Tcomp)を安定化する方法及びシステム(1)。集積電気部品の温度は、温度感知手段によって感知され、この温度感知手段は、第1及び第2の感知素子(61,62)と感知回路(72)とを備え、第1及び第2の感知素子は、集積電気部品と良好な熱接触にて配置され、第1及び第2の温度依存特性(63、64)を有し、第2の温度依存は、第1及び第2の特性(63,64)が予め規定した温度(Tset)にて交わるように第1の温度依存とは異なる。感知回路は、第1及び第2の感知素子(61,62)を感知するため、及び第1及び第2の温度依存特性(63,64)を示す第1及び第2の測定信号(83,84)を制御回路(71)に供給するために適合され、これはそこからの加熱手段用の制御信号を決定する。  (もっと読む)

(もっと読む)

集積半導体基板構造の製造方法

【課題】GaN素子およびCMOS素子の両方を備えた集積回路を製造するための改善した方法を提供する。

【解決手段】集積半導体基板構造100は、基板11と、GaNヘテロ構造20と、半導体基板層30とを備える。GaNヘテロ構造20は、第1素子エリアに存在し、少なくとも部分的に保護層8で覆われている。半導体基板層30は、CMOS素子の区画のための第2素子エリアに存在する。GaNヘテロ構造20および半導体基板層30の少なくとも1つが、基板11の少なくとも1つの溝内をエピタキシャル成長して形成され、GaNヘテロ構造20および半導体基板層30は横方向に並置される。

(もっと読む)

改良された閾値下の振れを有するトンネル電界効果トランジスタ

【課題】閾値下の振れが改良され、供給電圧が更に低減されたトンネル電界効果トランジスタを提供する。

【解決手段】高ドープドレイン領域3、低ドープチャネル領域2、高ドープソース領域1及び、高ドープソース領域1と接触する低ドープチャネル領域2の少なくとも一部を覆うゲート誘電体10およびゲート電極9を有し、ソース−チャネル界面12におけるゲート誘電体10の膜厚は、ソース−チャネル界面12から所定の距離離れたチャネル2上のゲート誘電体10の膜厚より小さい。

(もっと読む)

ウエハ検査方法およびシステム

【課題】多重パターニングリソグラフプロセスについての定性的及び/又は定量的な評価を得る。

【解決手段】第1設計および少なくとも第2設計から成る目標設計に従って多重パターニングリソグラフプロセスを用いて得られるリソグラフパターンを評価する方法であって、目標設計とリソグラフパターンとを整列させることと、リソグラフパターンと整列した目標設計における第1設計および第2設計のオーバーラップ領域に基づいて、リソグラフパターン内の縫合領域を識別することと、リソグラフパターン内の識別した縫合領域に関して、所定の基準を満足しているか否かを決定することとを含む。

(もっと読む)

81 - 90 / 302

[ Back to top ]