サンディスク コーポレイションにより出願された特許

1 - 10 / 173

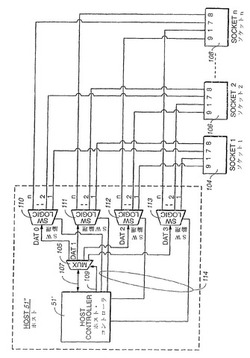

ホストと順次通信する複数の取り外し可能な不揮発性メモリ・カード

【課題】データが読み書きされる2つ以上の非常に小型のカプセル入り電子回路カードは、ホスト・システムの2つ以上のソケットに取り外し可能に挿入された場合に、それらの使用の柔軟性および効率性を最大にする。

【解決手段】コマンドおよび応答信号は、ホストとソケットの全てとの間に共通に接続されている単一の回路により該ホストとカードとの間で伝えられる。システムの初期化時には、該コマンドおよび状態回路を一つずつ順次各ソケットに接続することで相対カード・アドレスが各カードに書込まれていると確認され、初期化時にカード・アドレスをセットする速く簡単な方法である。ホストは、カードとの間でソケットの全てと共通に接続されている少なくとも2つの異なるデータ・ラインを介してデータを転送し、各カードは、使用することのできる並列データ・ラインの数についてのホスト読出し可能な指示を蓄積することでデータ転送速度を高める。

(もっと読む)

集積回路製品

【課題】 集積回路製品の製造のための改良技術を開示する。本改良技術により、より小さく、かつより安価な集積回路製品の製造を可能にする。

【解決手段】本発明の一態様は、集積回路製品が一度に1バッチを製造し、さらにこのバッチを個別の集積回路製品に単体化する工程に、非直線(例えば非長方形つまり曲線)上にソーイングまたは切断する操作を用いる。それにより得られる個別集積回路パッケージは、もはや完全に長方形である必要はない。本発明の他の態様は、集積回路製品は半導体アセンブリ工程により製造され得ることであり、それにより外部パッケージまたは容器を付与する必要が任意となる。

(もっと読む)

デュアルメディアストレージデバイス

【課題】データストレージデバイスを提供する。

【解決手段】第1不揮発性マスストレージデバイスは、利用可能な状態および利用不可能な状態に置かれえる。第1マスストレージデバイスがその利用不可能な状態にあるとき、ストレージコントローラは、第2マスストレージデバイスだけにアクセスする。利用不可能な状態は、そのデバイスが物理的に利用不可能である(例えば取り外されている)か、または単にストレージコントローラが、利用可能な状態にそれが戻るまで、それにアクセスしないかを意味する。第1マスストレージデバイスが利用可能な状態にあるとき、ストレージコントローラは、第1マスストレージデバイスまたは第2マスストレージデバイスのいずれかにアクセスするよう動作可能である。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

マスストレージアクセラレータ

【課題】 データストレージデバイスを提供する。

【解決手段】 ディスクデバイスは、不揮発性メモリデバイスと結合されて、ディスクデバイス単体で達成されるよりもより短いライトアクセスタイムおよびより高いデータライトスピードを提供する。2つのストレージデバイス間でセクタライトのバーストをインターリーブすることは、実効的にはディスクデバイスのシークタイムの効果をなくしえる。ホストシステムからの不連続な論理アドレス遷移に続いて、ストレージコントローラは、現在のデータを不揮発性メモリデバイスにライトしながら、ルックアヘッド動作をディスクデバイス上で実行できる。このようなシステムは、不揮発性メモリデバイスの本質的により速いライトアクセスを利用して、ディスクシークタイムによってふつう生じるデッドタイムをなくしえる。

(もっと読む)

不揮発性メモリ消去オペレーションにおけるワード・ライン補正

【課題】NANDストリング内のメモリ・セル毎に消去速度を一様とする消去技術を提供する。

【解決手段】複数のメモリ・セルの消去オペレーションを等化するために、消去オペレーション中に補正電圧を不揮発性メモリ・システムに印加する。補正電圧は、他のメモリ・セル及び/又は選択ゲートからNANDストリングのメモリ・セルに静電容量カップルされた電圧を補正する。補正電圧を1又は複数のメモリ・セルに印加して、メモリ・セルの消去オペレーションを実質的に好適化できる。補正電圧をNANDストリングの端部メモリ・セルに印加することで、その消去オペレーションをNANDストリングの内部メモリ・セルと等しくすることができる。

(もっと読む)

不揮発性メモリのプログラミング禁止スキームの選択的な使用

【課題】不揮発性メモリシステムを、プログラム妨害を低減又は防止するようにプログラムする。

【解決手段】1つの不揮発性メモリシステムに、複数のプログラム禁止スキームを採用している。プログラム禁止スキームは、プログラミング中のワードラインに基づいて選択される。特定のプログラム禁止スキームは、選択ワードラインにおいてプログラム妨害を好適に最小化又は排除する。プログラミング動作の前と最中に、メモリシステムの温度を検出する。プログラム禁止スキームは、システムの温度に基づいて選択できる。

(もっと読む)

メモリコントローラを備える様々な異なる規格のカードとともに用いられる汎用不揮発性メモリカード

【課題】汎用ドーターメモリカードを、異なるタイプのマザーカードに取り外し可能に接続可能とする。

【解決手段】マザー/ドーターカード不揮発性メモリシステムは、メモリを含むドーターメモリカード11と、メモリコントローラおよびホストインタフェース回路を備えるマザーコントローラカード13、14、15とを備える。ドーターメモリカード11は、可能な限り少ないメモリセルアレイを備え、多くの異なる発行されたメモリカード規格または知的所有権下にあるメモリカード規格に従う物理的属性およびホストインタフェースを有するいろいろなマザーコントローラカード13、14、15と接続するためのインタフェースを有する。種々のタイプのドターメモリカード11内の保護された位置にメモリの動作パラメータが蓄積されるときに、マザーコントローラカード13、14、15はこれらのパラメータを読み出し、かつそれに応じてその動作を適応させる。

(もっと読む)

不揮発性記憶装置のための可変書き込み

【課題】書き込み速度を向上するために書き込みパルス間の検証動作の量を制限する。

【解決手段】複数の不揮発性記憶素子を消去した後、ソフト書き込みが実行され、その不揮発性記憶素子の消去閾値区分が狭められる。ソフト書き込みの間、システムは、不揮発性記憶素子の第1セットに対してソフト書き込みを終了するための書き込みパルスの数と、不揮発性記憶素子の最後のセット以外の全てのセットに対してソフト書き込みを終了するための書き込みパルスの数を特定する。それら2つの数は、不揮発性記憶素子の閾値区分の特徴付けるのに用いられる。閾値区分のこの特徴と書き込みパルスのステップサイズが、後続の書き込みにおいて用いられる検証パルスの数を制限するのに用いられる。

(もっと読む)

共通論理ブロックに関連付けられている物理ブロックを解決するための方法および装置

【課題】論理ブロックに関連付けられている複数の物理ブロックのうちどれが、より最近に論理ブロックに関連付けられた物理ブロックであるかを判定する。

【解決手段】判定する方法は、第1の物理ブロックに関連付けられている第1の識別子を取得するステップおよび第2の物理ブロックに関連付けられている第2の識別子を取得するステップを含む。これらの識別子を比較して、前記第1の物理ブロックがより最近に論理ブロックに関連付けられたことを第1の識別子が示すかどうかを確認する。この方法は、さらに、第1の識別子が、その第1の物理ブロックがより新しく論理ブロックに関連付けられたことを示すと判定されたときに論理ブロックに関連付けられている内容を第1の物理ブロックに供給するように構成されたオペレーションを完了するステップを含む。

(もっと読む)

1 - 10 / 173

[ Back to top ]