エイアールエム リミテッドにより出願された特許

1 - 10 / 85

発信元デバイスから受信デバイスに対して発行されるトランザクション要求のための動的リソース割り当て

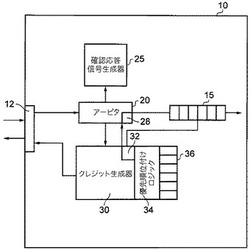

【課題】発信元デバイスによって受信デバイスへ発行されるトランザクション要求のための動的リソース割り当てを実現する。

【解決手段】受信デバイスは、トランザクション要求のために利用可能なバッファ記憶がある場合にトランザクション要求を受諾する。利用可能な記憶空間がない場合、確認応答信号生成器が、要求が受信デバイスによって受信されたが受諾されていないことを示す拒絶確認応答信号を生成し、出力する。クレジット生成器は、バッファ内に少なくとも1つの利用可能な記憶位置を予約することができ、受信デバイスによって受諾されなかったトランザクション要求のうちの1つを送信した発信元デバイスに対してクレジット許諾を生成することができる。クレジット許諾は、発信元デバイスからのその後のトランザクション要求が受信デバイスによって受諾されるように、発信元デバイスに、少なくとも1つの予約済み記憶位置があることを示す。

(もっと読む)

データ処理装置用トレース・ストリームの生成技術

【課題】有限な帯域幅、トレース要素がバッファされる全てのトレース・バッファの有限サイズの更に効率的な使用を可能とするデータ処理装置の特定ロジックの活動を示すトレース要素を含むデータ処理装置用トレース・ストリーム生成技術を提供する。

【解決手段】データ要素を産出するロジックと、少なくともいくつかのデータ要素を表すトレース要素のストリームを産出するためのトレース・ロジックとを含み、トレース・ロジックはトレース・タイミング標識をストリーム内に含めるように構成されていて、各々のトレース・タイミング標識が予め定められた複数のクロック・サイクルである1つまたは複数の処理タイミング間隔を表示することで、単一サイクル精度レベルの分析をより少ない数のトレース要素で実現する。

(もっと読む)

同時保留中データアクセスリクエストのためのデータハザード処理

【課題】イニシエータデバイスではなく、コヒーレンシコントローラでデータハザードを管理する、データ処理システムを提供する。

【解決手段】2つの部分形式で書き込みリクエストを処理する。同じアドレスに対し同時保留の読み出しおよび書き込みが存在する時、書き込みの第1の部分に応答しないことでコヒーレンシコントローラにより延期され、イニシエータデバイス10は、書き込みが保留中に関係なく、書き込みのアドレスに受信されたいずれのスヌープリクエストも処理するように進行する。保留中の読み出しが完了すると、コヒーレンシコントローラは、書き込みの第1の部分に応答し、イニシエータデバイスは、データおよびスヌープ後のデータの状態のインジケータを送信することによって、書き込みを完了する。コヒーレンシコントローラは、必要に応じてメモリを更新するためにこの情報を使用して潜在的なデータハザードも回避することができる。

(もっと読む)

データ処理システムの同期化

【課題】大規模な分散システムの同期化を可能とする。

【解決手段】データ処理システムであって、トランザクション要求を生成する複数のトランザクション要求生成装置、トランザクション要求を受信する受信装置を含む複数の装置、同期化装置、上記装置を相互接続する少なくとも1つの相互接続装置とを有する。同期化装置は、トランザクション装置の1つによって生成されたシステム同期化要求の受信に応答して、トランザクション要求の少なくとも一部の進捗を判定するために複数の同期化要求を生成し、この複数の同期化要求をマルチキャストするため、データ処理システムの装置の少なくとも1部に同期化要求を出力するマルチキャスト回路と、複数の同期化要求に対する応答を収集し、全ての応答が受信されたという判定に応答して、システム同期化要求の1つに対する応答を出力するする収集回路を含む。

(もっと読む)

状態保持回路における状態保全性の検証

【課題】 本発明は、データ処理動作を行うよう構成されたデータ処理回路を備えたデータ処理装置を提供する。

【解決手段】 複数の状態保持回路がデータ処理回路の一部を形成し、これらの回路は、低電力モードに入ったデータ処理回路のそれぞれのノードにてそれぞれの状態値を保持するよう構成される。1以上のスキャンパスは、状態値がそれぞれのノードにスキャンインまたはアウトされてもよいよう、複数の状態保持回路を直列に接続する。複数のパリティ情報生成要素はスキャンパスに結合され、状態保持回路によってそれらそれぞれのノードにて保持されたそれぞれの状態値を示すパリティ情報を生成するよう構成される。複数のパリティ情報生成要素は、それぞれの状態値の一つが変化した場合にパリティパスの出力にて生成された出力パリティ値を反転するよう、1以上のパリティパスを提供し、状態保持回路によって保持された状態値の保全性の外部指示を提供するよう配置される。

(もっと読む)

非同期のデバイスによって実行されるタスクのスケジューリングの向上

【課題】複数の非同期の処理デバイスのうちの1つによって処理されるタスクをスケジューリングするための方法を、非同期のデバイスとタスクスケジューラとを備えるデータ処理装置と共に提供する。

【解決手段】非同期の処理デバイスは、ローカルストレージおよび複数の非同期の処理デバイスのうちの少なくともいくつかによってアクセス可能なメモリに記憶されるデータを処理する。本方法は、非同期の処理デバイスによって処理される複数の非依存タスクのそれぞれについて、非依存タスクの処理の前に実行することが必要な一貫性動作を判定するステップと、非依存タスクのうちの1つについて一貫性動作を実行し、完了時に、処理のために処理デバイスへタスクを発行するステップと、一貫性動作の完了時に、非同期の処理デバイスがさらなるタスクを処理できるように、さらなる非依存タスクについての一貫性動作を実行するステップとを備える。

(もっと読む)

機密データの暗号化および記憶

【課題】機密データをセキュアに記憶するためのデータ記憶回路、およびデータを処理および記憶するためのデータ処理装置、ならびに方法を開示する。

【解決手段】データ記憶回路は、データを記憶するための複数のデータ記憶場所を備える、データ記憶と、データ記憶にアクセスするための要求を受信するための入力と、データ記憶内の物理データ記憶場所へのアクセス要求に指定されたアーキテクチャデータ記憶場所をマッピングするためのリネーミング回路と、データ記憶内へのデータの記憶に先立って、データを暗号化するための暗号化回路であって、その中にデータが記憶される物理データ記憶場所に応じて、暗号化キーを生成するように構成される、暗号化回路と、データ記憶から読み取られたデータを復号するための復号回路であって、そこからデータが読み取られる物理データ記憶場所に応じて、復号キーを生成するように構成される、復号回路と、を備える。

(もっと読む)

シングルイベントアップセットに対する耐性を増加させた記憶回路および方法

【課題】シングルイベントアップセットへの増加した耐性のある記憶回路が、回路の動作方法と共に提供される。

【解決手段】記憶回路は、第1記憶機能を実行する少なくとも1の動作モードのある第1記憶ブロックと、前記第1記憶機能と異なる第2記憶機能を実行する少なくとも1の動作モードのある第2記憶ブロックとを有する。構成回路は、第2記憶機能が未使用である所定の動作モードに応答し、第1記憶ブロックと並列動作するよう第2記憶ブロックを構成する。記憶ブロックの1つが有用でない機能を実行している場合、2つの記憶ブロックを並列に配列し、有用な記憶機能をなおも実行している記憶ブロックの大きさを増加させ、シングルイベントアップセットへの耐性を増加させる。この手法は、最小面積および電力消費オーバーヘッドのある、多くの逐次セル設計で使用可能な小型記憶回路を提供する。

(もっと読む)

乱数を発生させるための装置および方法

【課題】乱数を発生させるための特に単純かつ効率的な小領域装置を提供する。

【解決手段】乱数を発生させるための装置および方法を提供し、該装置は、少なくとも1つの発生器回路を有し、各発生器回路は、第1の動作モードおよび第2の動作モードを提供するように構成され、第1の動作モードにおいて、各発生器回路は発振器として動作し、第2の動作モードでは、各発生器回路は状態保持要素として動作する。次いで、制御信号発生器は、各発生器回路に入力するための制御信号を発生させる。各発生器回路は、第1の動作モードにおいて動作するように設定レベルの入力制御信号に応答し、第2の動作モードにおいて動作するように解除レベルの入力制御信号に応答する。入力制御信号が設定レベルから解除レベルに遷移する際に、各発生器回路は、状態保持要素内で発振器の電流値を取得し、乱数の少なくとも一部を形成するようにその電流値を出力するように構成される。

(もっと読む)

浮動小数点加算を実行するための装置および方法

【課題】結果Rを得るためにオペランドA、Bに加算演算を実行する装置および方法を提供する。

【解決手段】オペランドAおよびオペランドBに異符号加算を実行することにより生成される出力において存在するであろう先行ゼロの個数の予測に基づいて、シフト表示を生成する予測回路を備える。結果前正規化回路は、仮数部を加算する前に、オペランドA、Bの両方の仮数部にシフト演算を実行する。これは、オペランドA、Bに対する修正された仮数部を生成するために、シフト表示の決定に応じて、両方のオペランドの仮数部のいくつかの最上位ビットを廃棄するように作用する。オペランド解析回路は、オペランドA、Bの指数を参照して、先行ビット相殺状態の存在を検出し、加算回路は、先行ビット相殺状態が存在する場合において、結果Rの仮数部を生成するために、オペランドA、Bに対する修正された仮数部を加算する。

(もっと読む)

1 - 10 / 85

[ Back to top ]