アクセラリックス・リミテッドにより出願された特許

1 - 2 / 2

IC(集積回路)

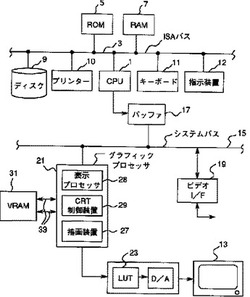

【課題】本発明は、計算機のグラフィックおよびビデオ表示システムにおいて、表示プロセッサとメモリ間に大規模なバスを設けることにより、インターフェース処理速度の高速化を実現し、またチップ内の消費電力を制御、抑制することにより、グラフィックおよびビデオ表示において高速化を実現する。

【解決手段】グラフィック画素データとビデオ画素データの少なくとも1つを記憶するダイナミックランダムアクセスメモリ(DRAM)と、画素データを処理するための画素データユニット(PDU)とから構成され、DRAMと同じ集積回路(IC)チップに集積される。また更に、該ICチップは、DRAMからPDUに同時に画素データのブロックを転送するパラレルバスを含み、PDUは処理された画素データを表示するために画素データブロックを処理する。

(もっと読む)

シングルチップ表示プロセッサ

【課題】本発明は、計算機のグラフィックおよびビデオ表示システムにおいて、表示プロセッサとメモリ間に大規模なバスを設けることにより、インターフェース処理速度の高速化を実現し、またチップ内の消費電力を制御、抑制することにより、グラフィックおよびビデオ表示において高速化を実現する。

【解決手段】グラフィック画素データとビデオ画素データの少なくとも1つを記憶するダイナミックランダムアクセスメモリ(DRAM)と、画素データを処理するための画素データユニット(PDU)とから構成され、DRAMと同じ集積回路(IC)チップに集積される。また更に、該ICチップは、DRAMからPDUに同時に画素データのブロックを転送するパラレルバスを含み、PDUは処理された画素データを表示するために画素データブロックを処理する。

(もっと読む)

1 - 2 / 2

[ Back to top ]