エルジイ・セミコン・カンパニイ・リミテッドにより出願された特許

1 - 4 / 4

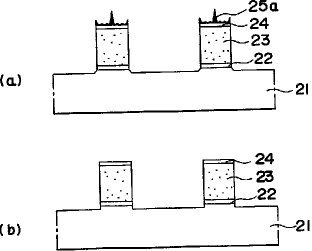

半導体素子の配線形成方法

【課題】 残留物除去時に別途の設備、追加処理が不要で、配線のパターン形状も良好に維持でき、工程時間も短縮できる半導体素子の配線形成方法を提供すること。

【解決手段】 絶縁層21上に形成された障壁層22、アルミニウム又はアルミニウム合金層23および反射防止膜24をパターニングし、さらにクリーニングした後、クリーニング時に発生した残留物25aをフッ素を含有するガスと酸素とが混合されたプラズマを用いて除去する。

(もっと読む)

半導体素子のキャパシタ製造方法

半導体素子のキャパシタ製造方法

【課題】 表面段差の軽減、容量増大を図り、漏洩電流も少なく、かつ精度の向上、工程の簡素化を図れる半導体素子のキャパシタ製造方法を提供すること。

【解決手段】 基板201上に第1、第2絶縁膜203,204を形成し、コンタクト領域の第2絶縁膜204を除去し、全面に第3絶縁膜205を形成し、キャパシタ領域の第3絶縁膜205を除去し、露出した第2絶縁膜204をマスクとして第1絶縁膜203にコンタクトホール206を形成し、全内壁および第3絶縁膜205の表面に導電層207を形成し、さらに平坦化層212を形成し、平坦化層212を第3絶縁膜205の表面まで削り出し、同時に導電層207を第3絶縁膜205の表面から除去して、第3絶縁膜205の除去部内壁およびコンタクトホーツ206に段付き2重シリンダ形状に貯蔵電極208を形成する。その後、残存平坦化層212と残存第3絶縁膜205を湿式食刻で除去する。

(もっと読む)

半導体パッケージ及び電子回路盤

1 - 4 / 4

[ Back to top ]