マイクロン テクノロジー, インク.により出願された特許

1 - 10 / 444

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

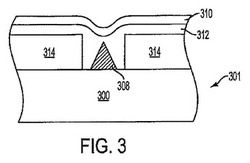

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

構成可能な入出力ポートを伴うメモリモジュール

【課題】メモリモジュールの入出力ポートの入力/出力の構成を変更可能とする。

【解決手段】メモリモジュール320は、1つ以上のメモリデバイスと、1つ以上のメモリデバイスと通信するコントローラ330と、複数の入出力ポート350とを有する。複数のコントローラ310の一つは入出力ポートのそれぞれを構成するようにコントローラ330に指示する。コントローラ330は、各入出力ポート350を、入力、出力、または双方向入出力として構成する。

(もっと読む)

相変化メモリのプログラミングのためのセットパルス

【課題】相変化メモリをプログラムするための単一パルスアルゴリズムを提供する。

【解決手段】相変化メモリ(PCM)セルを融解させるために第1の特定の信号値レベルで電子信号を印加させることと、前記PCMセルが融解した後、0ではない第2の特定の信号値レベルに到達するまで、印加されている前記電子信号の前記信号値レベルを低下させることと、を含み、前記信号値レベルは、前記第1の特定の信号値レベルと前記第2の特定の信号値レベルとの間で、信号値レベルの実質的に垂直な降下が起きないように低下する。

(もっと読む)

多重プリフェッチI/O構成を備えるデータパスを有するメモリデバイスおよび方法

【課題】高速で狭いデータバス幅を持つメモリと低速で広いデータバス幅を持つメモリのどちらにも対応可能なメモリを提供する。

【解決手段】高速または低速のいずれのモードにおいても、2つのメモリアレイ各々からの32ビットのデータは各組の32個のフリップフロップ120中にプリフェッチされる。高速モードにおいて、上記プリフェッチされたデータビットは4つのパラレル−シリアルコンバータ150aに並列伝送される。上記コンバータは上記パラレルデータビットを8つのシリアルデータビットのバーストに変換し、上記バーストを4つのデータバス端子160それぞれに付与する。低速モードにおいて、2組のプリフェッチされたデータビットは8つのパラレル−シリアルコンバータに並列で伝送される。上記コンバータは上記パラレルデータビットを8つのシリアルデータビットのバーストに変換し、上記バーストを8つのデータバス端子それぞれに付与する。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

【課題】公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法を提供する。

【解決手段】第1の表面214及び対向する第2の表面216を有する基板212を設け、基板の第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビア218を形成する。酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションし、少なくとも一つのブラインドビアの酸化材料の表面に銅を含むシード材料228を、シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、基板の前記第1の表面を露出させるように形成する。シード材料の上に導電性材料230を前記少なくとも一つのブラインドビアを充填するように無電解めっきし、少なくとも一つのブラインドビアの導電性材料を露出させるために基板の前記第2の表面に研磨平坦化を実施する。

(もっと読む)

トランザクションメモリ

【課題】トランザクション処理におけるソフトウェアオーバヘッド及び複雑さを低減する。

【解決手段】トランザクションリクエスト又は複数のトランザクション演算子を含むトランザクションコマンドを受信することに応答して、メモリアレイのオリジナルコンテンツを他の部分にコピーすることと、トランザクション演算子を受信することに応答して、コピーしたオリジナルコンテンツを修正する。トランザクションコミットを受信することに応答して、トランザクションが成功した場合のみ、オリジナルコンテンツを修正したコンテンツで置換する。

(もっと読む)

コンデンサ装置の形成方法

【課題】DRAMコンデンサとして高アスペクト比容器の外面も容量面として利用可能とする方法を提供する。

【解決手段】絶縁材28中の開口部内に導電性蓄積ノード部材60が形成されて導電性容器が形成される。保持構造体30が容器の少なくとも一部(例えば容器の断面の周囲の50%)と物理的接触状態となるように形成され、次いで絶縁材28が除去されることにより容器の外側表面が露出される。保持構造体30によって容器構造体のぐらつきあるいは他の構造上の欠陥が減じられる。導電性容器は第一コンデンサ電極60に相当する。容器の外側側壁が露出された後、絶縁材100が容器内に露出された外側側壁に沿って形成される。その後に第二コンデンサ電極103が絶縁材上へ形成される。これら第一及び第二コンデンサ電極と絶縁材とによって複数のコンデンサ装置が形成される。

(もっと読む)

SOI型トランジスタ

【課題】DRAMメモリアレイに用いられるセミコンダクタ・オン・インシュレータ型トランジスタを提供する。

【解決手段】SOI型のトランジスタは、半導体物質層60(SOI層)と、この半導体物質層60の内部を通って走るゲート線65a,65b,66cと、このゲート線65a,65b,66cに沿ってソース拡散領域70a、70b、70cよりも遠くまで延びるドレイン拡散領域64と、このドレイン拡散領域64よりも上方にあるソース拡散領域70a、70b、70cと、ドレイン拡散領域64まで延びるドレインコンタクト79と、ソース拡散領域まで延びるソースコンタクトと、を備え、これらドレインコンタクト79及びソースコンタクトは、ゲート線65a,65b,66cと平行に走る平面内にある。

(もっと読む)

組込み型チャネル選択を備えるマルチチャネルメモリ

【課題】マルチチャネルメモリデバイス、及び、マルチチャネルデバイスの1つ又は複数のチャネルを選択する方法を提供する。

【解決手段】メモリデバイスに組み込まれたスイッチインターフェース(SI)レジスタ147は、複数のインターフェースの特権レベルを管理する。SIレジスタ147は、インターフェースに帰する特権レベルに関係なく、複数のインターフェースを介してアクセス可能であってもよい。ステータスレジスタ149はステートマシーンビジービットを含み、デュアルチャネルメモリにおいて、どちらかのインターフェースは、ステータスレジスタ149をいつでも読み出してもよく、一方では、メモリアレイ143にアクセスする比較的高い特権レベルを有するインターフェースのみが、ステータスレジスタ149に書き込んでもよい。

(もっと読む)

1 - 10 / 444

[ Back to top ]