マイクロン・テクノロジー・インコーポレーテッドにより出願された特許

1 - 10 / 55

外部クロック信号に同期する内部クロック信号を発生する方法および装置

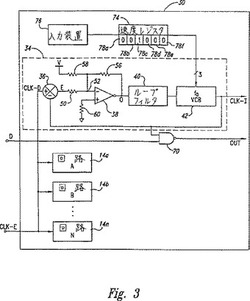

【課題】外部クロック信号に同期した内部クロック信号を生成するクロック回路を提供すること。

【解決手段】位相ロックループ(PLL)からなる集積回路のためのクロック発生回路は、遅延した外部クロック信号の位相を内部クロック信号の位相と比較する位相検波器を含む。2つのクロック信号間の位相差分に一致するエラー信号が、差動増幅器に与えられる。エラー信号は位相検波器に結合される時、外部クロック信号の遅延に一致する値だけオフセットされる。オフセットエラー信号は、内部クロック信号を発生する電圧制御発振器の制御入力に与えられる。内部クロック信号の位相は、外部クロック信号の位相と実質的に同じになるように調整される。電圧制御発振器は、オフセットエラー信号が比較的狭い範囲の内部クロック信号の周波数を制御するだけで済むように複数の別個の周波数帯域内で動作するように構成される。

(もっと読む)

温度補償された読み出し・検証動作をフラッシュ・メモリにおいて生成するための方法及び装置

【課題】半導体メモリの動作期間に生じ得る温度変動を補償する。

【解決手段】ワード線電圧を生成する方法及び装置を開示する。ワード線電圧発生器は、第1の電流源、調整可能な電流源、調整可能な電流シンク及び電圧変換器を備え、これらは電流加算ノードに接続される。第1の電流源は少なくとも1つのビット・セルの温度係数に等しい温度係数を持つ第1の電流を生成する。調整可能な電流源は温度変化から独立した第2の電流を生成する。調整可能な電流シンクは温度変化から独立した第3の電流を生成する。電圧変換器は基準電流に比例するワード線電圧を有するワード宣伝流を生成する。基準電流は(第1の電流+第2の電流)−第3の電流を含む。

(もっと読む)

温度係数が小さいパワー・オン・リセットを生成する方法及び装置

【課題】実質的に温度変化に無関係なパワー・オン・リセット信号を生成する方法及び装置を提供すること。

【解決手段】リセット回路は、電圧生成器、第1の抵抗素子、電流生成器及びコンパレータを備える。電圧生成器は負の温度係数を有する第1の電圧信号を生成する。第1の抵抗素子は供給電圧と第2の電圧信号との間に結合される。電流生成器は第2の電圧信号に結合され、且つ、オフセット電流と正の温度係数を有する基準電流とをシンクするように構成される。コンパレータは、第1の電圧信号と第2の電圧信号とを比較してリセット信号を生成するように構成される。本発明は更に、パワー・オン・リセット信号を生成する方法又は装置を含む半導体デバイス、半導体ウェーハ及び電子システムを含む。

(もっと読む)

バンド・ギャップ基準から可変出力電圧を生成する方法及び装置

【課題】電圧基準回路から可変出力電圧を生成する方法及び装置を提供すること。

【解決手段】電圧基準回路は、負の温度係数を有する第1の電圧信号を生成する第1の電圧発生器と、正の温度係数を有する第2の電圧信号を生成する第2の電圧発生器とを備える。電圧基準回路は、基準電流を第1の電圧発生器及び第2の電圧発生器に供給する電流発生器を更に備える。第1の電圧信号を第2の電圧信号と比較する比較器が比較結果を生成し、比較結果に関係付けられた電流変化で基準電流を修正する。電圧基準回路は、電流発生器に結合された出力端末を備え、出力端末はバンド・ギャップ電圧より高い電圧差であって温度変化に実質的に依存しない電圧を含む。

(もっと読む)

サブLSBを用いた拡張デジタルデータ路構造

【課題】画像処理データ路における誤差の低減及び列固定パターン雑音を補正したイメージセンサ装置を提供する。

【解決手段】画像処理データ路に可変バスビット幅を採用し、デジタル利得値にかかわらず高精度の出力を発生させることができ、さらにデータ路中に列固定パターン雑音補正ブロック及びデジタル利得処理ブロックを有する。

(もっと読む)

並列入力演算平均モジュールを用いてイメージャ雑音低減化を行う方法及び装置

【課題】メモリ容量を少なくし、雑音補正値を有効に発生させてCMOSイメージャのピクセル出力に与える方法と装置の提供。

【解決手段】校正処理に際し、ピクセルオフセット値及び平均ピクセル出力値を計算することにより雑音補正値を発生させる。校正用の行を読む度に、複数のピクセル出力値に対する平均ピクセル出力値を決定する。複数のピクセル出力の各々と、計算した平均ピクセル出力値との差をとることで、複数のピクセル出力の各々に対するオフセット値を発生させる。イメージャの行における複数の光学的に黒のピクセルに対する平均ピクセル出力値を求めることにより、ピクセル出力の行全体に対するオフセット値を計算することもできる。光学的に黒のピクセル値に対する平均ピクセル出力値は、しきい値窓の外にあるピクセル値を排除し、これに代えて平均ピクセル出力値を用い、新たな平均ピクセル値を計算することにより真値に近づけることができる。

(もっと読む)

アンチエクリプス回路及びその動作方法

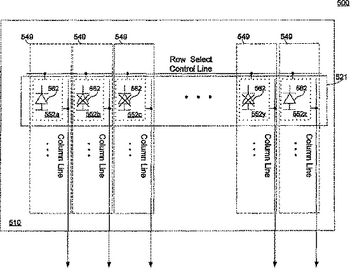

【課題】半導体イメージャで発生するエクリプスの発生を抑圧するアンチエクリプス回路及びその形成方法を提供する。

【解決手段】イメージピクセルのアンチエクリプス回路は、ピクセル出力ラインに結合されたピクセルと、ピクセル出力ラインに得られるピクセルからのピクセルリセット電圧を受けて記憶するとともに、この記憶したピクセルリセット電圧をパラメータとして用いて、ピクセル出力ライン上のピクセルリセット電圧を予め決定した最小電圧よりも高く維持するようにピクセル出力ライン上のリセット電圧を制御する回路とを具える。

(もっと読む)

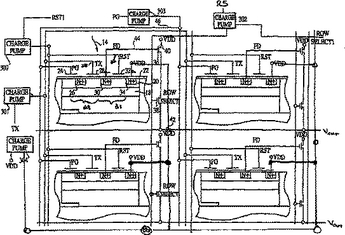

CMOSイメージャのためのチャージポンプ

イメージング素子のための画素を説明する。本発明の画素は、光発生電荷を生じるように基板に設けられた感光素子と、光発生電荷の代表的な、少なくとも1つの画素出力信号を生じる前記感光素子との結合回路であり、前記結合回路の動作中に第1の制御信号に応答する少なくとも1つの動作素子を備える前記結合回路と、ポンプ回路とを備える。そのポンプ回路は、基板ポンプ、チャージポンプ、及び/又は、電圧ポンプを備えることができる。本発明の画素を、イメージングシステムに備えることもできる。  (もっと読む)

(もっと読む)

CMOSイメージャ用ホトダイオードヒューズID

チップ上に形成されるCMOSイメージピクセルアレイは、プログラミングした情報をこのピクセルアレイ内に記憶するのに用いられる。製造ロット及びその他のデータは、製造中や検査中に、レーザをピクセルに加えてホトダイオードを欠陥のあるものとすることにより、ピクセルアレイに書込まれる。プログラミングされたデータは、現存の回路を用いてピクセルアレイから読出される。  (もっと読む)

(もっと読む)

高速カウントを生成するための方法および回路

【課題】メモリデバイスでの動作タイミングを制御するための複数のビットを伴うデジタルカウントを生成する、高速計数回路

【解決手段】計数回路は、2つの位相シフトクロックによって駆動される一連のレジスタを含む。計数回路中のクロックジェネレータは、各レジスタを駆動するための4つの非対称クロック信号を生成する。レジスタは、入力および出力ステージから形成され、各ステージは、2組のスイッチを備える。各ステージ中の第1の組のスイッチは、非対称クロックに応答して、ステージ出力に供給電圧を与える。第2の組のスイッチは、非対称クロックに応答して、グラウンドをステージ出力に与える。スイッチング回路の応答を速めるために、第2の組のスイッチの切換え中に、分離スイッチが、各対における第1の組のスイッチをステージ出力から減結合し、その結果、第2の組のスイッチによるステージ出力の負荷を除去する。

(もっと読む)

1 - 10 / 55

[ Back to top ]