チンギス・テクノロジー・コーポレイションにより出願された特許

1 - 1 / 1

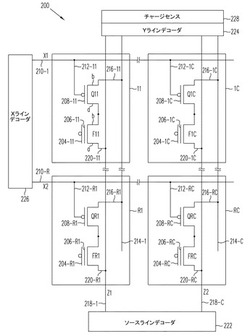

低電圧、低キャパシタンスのフラッシュメモリアレイ

【課題】メモリセルを読み出すときは低キャパシタンスで、比較的低電圧で使用可能な構造のフラッシュメモリアレイを提供する。

【解決手段】p型フラッシュメモリアレイで、プログラミングビットライン及び読み出しビットラインが別個に提供される。プログラミングビットラインは、そのビットラインに接続したメモリセル内のフローティングゲートトランジスタをプログラムするときにのみ使用され、読み出しビットラインは、メモリ回路動作中に、そのビットラインに接続した選択メモリセル内のフローティングゲートトランジスタの状態を読み出すときにのみ使用される。プログラミング中及びメモリアレイ動作中に低電圧で使用可能な構造であり、従来の比較的低電圧のp型フラッシュメモリ構造で、メモリセルの読み出し中に各ビットラインに関連して可変し予測不可能であったキャパシタンスを排除するような構造である。

(もっと読む)

1 - 1 / 1

[ Back to top ]