アルテラ コーポレイションにより出願された特許

1 - 10 / 163

リレーデバイスを有するメモリ要素

【課題】メモリ要素有する集積回路を提供すること。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

(もっと読む)

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

時間分割多重化された多重ポートメモリ

【課題】第1のポートと第2のポートとを有するデュアルポートメモリを動作させる方法を提供すること。

【解決手段】上記方法は、第1のポートにおいて、第1のメモリアクセス要求と、関連付けられた第1のクロック信号とを受信することと、第2のポートにおいて、第2のメモリアクセス要求と、関連付けられた第2のクロック信号とを受信することと、制御回路を用いて第2のクロック信号の立ち上りクロックエッジを検出することに応答して、第3のクロック信号を生成し、かつ第2のメモリアクセス要求にサービスを提供することと、第2のメモリアクセス要求がサービスを提供されている間に、第3のクロック信号を用いて第1のメモリアクセス要求をサンプリングすることとを含む。デュアルポートメモリは、単一ポートメモリ要素のアレイを含む。

(もっと読む)

フレキシブルな受信器アーキテクチャ

【課題】高速データインクのための回路網を提供すること。

【解決手段】データリンクのための受信器回路であって、該受信器回路は、第1の等化回路網を含む第1の信号経路と、第2の等化回路網を含む第2の信号経路と、該第1の信号経路および該第2の信号経路のうちの1つの信号経路を選択するように構成された経路選択器回路とを含む、受信器回路。一実施形態において、前記第1の信号経路は、決定フィードバック等化器回路を含む。

(もっと読む)

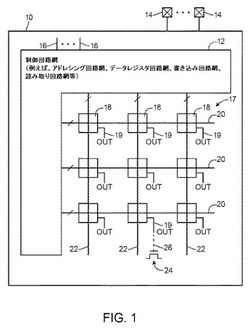

メモリ仲裁回路網

【課題】第1および第2のポートを有するデュアルポートメモリを提供する。

【解決手段】デュアルポートメモリは、単一ポートメモリ要素のアレイ22と、アレイに連結されており、かつアレイからデータを読み取り、アレイにデータを書き込むように動作可能である制御回路30と、第1のポートから第1のメモリアクセス要求を受信するように動作可能な第1の要求生成器60−Aと、第2のポートから第2のメモリアクセス要求を受信するように動作可能な第2の要求生成器60−Bと、制御回路、並びに第1および第2の要求生成器に連結されている仲裁回路64とを含み、仲裁回路は、同期モードで動作可能であり、同期モードにおいて、第1および第2の要求生成器は、等しい周波数を有する少なくとも2つのクロック信号を用いて制御される。

(もっと読む)

推測的技術を用いるメッセージベースのネットワークインターフェースのためのプロセッサ

【課題】メッセージネットワークインターフェースユニットを提供すること。

【解決手段】メッセージネットワークインターフェースユニットは、プロセッサに連結されており、プロセッサがプロセッサによって生成された複数のメッセージをハードウェアユニットに送信することを可能にし、メッセージネットワークインターフェースユニットは、プロセッサによって生成された複数のメッセージのうちの少なくもと1つのメッセージの引数を格納するように動作可能な伝送レジスタであって、少なくとも1つのメッセージが推測的に生成される、伝送レジスタと、伝送レジスタに連結されており、複数のメッセージをキューに入れるように動作可能なキューであって、動作は、メッセージネットワークインターフェースユニットがトリガーメッセージを受信することに応じてキューにおいて実行される、キューとを含む。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

電子回路網の信頼性を向上させるための装置および関連する方法

【課題】電子回路網の信頼性を向上させるための装置および関連する方法を提供すること。

【解決手段】上記装置は、装置の第1の構成に使用される第1のセットの回路要素と、装置の第2の構成に使用される第2のセットの回路要素とを含み、装置の第1の構成は、装置の信頼性を向上させるために、装置の第2の構成に切り替えられる。上記方法は、第1の構成に割り当てられた第1のセットの回路要素を使用することによって、第1の構成で集積回路(IC)を動作させることと、第2の構成に割り当てられた第2のセットの回路要素を使用することによって、第2の構成でICを動作させることとを含み、第1の構成でICを動作させた後に第2の構成でICを動作させるのは、ICの信頼性を向上させる。

(もっと読む)

撚り合わされた導線を有する集積回路インダクター

【課題】集積回路インダクターを提供すること。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に連結された伝導性経路とを備え、伝導性経路は、集積回路上に複数の撚り合わされた伝導性線を含む、インダクター。撚り合わされた伝導性線は、集積回路上に少なくとも1つの金属層から形成された少なくとも第1の伝導性線と、集積回路上に少なくとも1つの金属層から形成された少なくとも第2の伝導性線とを含む、インダクター。

(もっと読む)

1 - 10 / 163

[ Back to top ]