旺宏電子股▲ふん▼有限公司により出願された特許

1 - 10 / 27

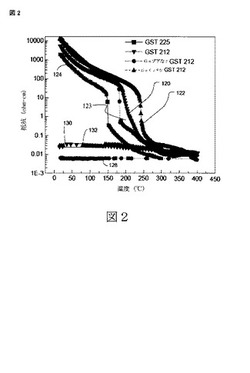

GeリッチなGST−212相変化材料

【課題】本発明の主な目的は、GeリッチなGST−212相変化材料を提供することにより、従来のGST−225の相変化メモリよりも高い結晶化温度、低いリセット電流要件及び優れた保持率を有することができる。

【解決手段】相変化材料は、Ge原子濃度xは、30%〜65%の範囲内にあり、Sb原子濃度yは、13%〜27%の範囲内にあり、Te原子濃度zは、20%〜45%の範囲内にある。このような材料のGeリッチな族も記載されている。そのような材料を含む集積回路に適したメモリデバイスは記載されている。

(もっと読む)

ドープされた相変化材料を形成するための複合ターゲットのスパッタリング

【課題】本発明の主な目的は、相変化材料層を形成する方法を提供することにより、従来の技術でのウエハの表面の汚染、歩留まりの減少という問題を克服することができる。

【解決手段】ケイ素又は他の半導体、或いは、ケイ素系や他の半導体系の添加剤を有する相変化材料層が、ケイ素や他の半導体及び相変化材料を含む複合スパッタターゲットを使用することによって形成される。その複合スパッタターゲットのケイ素または他の半導体の濃度は、形成される前記層におけるケイ素または他の半導体の特定された濃度よりも5倍以上大きい。GST型の相変化材料のケイ素系添加剤に対し、スパッタターゲットは40原子%以上のケイ素を含むことができる。ケイ素系又は他の半導体系の添加剤は、成膜時のスパッタチャンバー内に、酸素や窒素のような反応ガスの流れを伴なう複合スパッタターゲットを用いて形成され得る。

(もっと読む)

3次元メモリアレイ用のアーキテクチャ

【課題】アレイ内のセル特性におけるばらつきを補償する技術を提供するとともに、レベルの違いによって起こる複雑性を少なくする3次元集積回路メモリを提供する。

【解決手段】異なるバイアス条件を選択されたビット線に適用することによりアレイ内のメモリセルの閾値電圧のばらつき補償する技術を開示する。また、グローバルビット線を3次元アレイ内の様々なレベルのメモリセルに接続してグローバルビット線間の静電容量差を最小化させる技術を開示する。

(もっと読む)

NANDメモリ用デコーダ

【課題】NANDフラッシュメモリで使用する広い正負電圧範囲を有する高電圧スイッチを提供する。

【解決手段】高電圧スイッチはデコーダ信号を受信し、負第1バイアス電圧と正第2バイアス電圧により設定される第1電圧範囲のレベルシフター電圧出力を有するレベルシフターと、レベルシフターの出力に結合され、第1電圧範囲より広い正第3バイアス電圧と負第1バイアス電圧により設定される第2電圧範囲のプルアップ回路電圧出力を有するプルアップ回路とを備える。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼できる非常に小型の記憶素子を含む、3次元集積回路メモリ用の構造を低い製造コストで提供すること。

【解決手段】3次元メモリデバイスは、絶縁材料によって分離され、復号化回路を介してセンスアンプに結合可能なストリングとして配置された複数の隆起した形状スタック含む。ダイオードは、ストリングのストリング選択端部又は共通ソース選択端部のどちらか一方においてビット線構造に接続される。導電材料の帯片は、隆起した形状のスタックのサイドに側面を有する。ワード線として配列された複数の導電線は、行デコーダに結合することができ、複数の隆起した形状のスタックの上で直交して延びる。記憶素子は、スタック上の電導性帯片の側面と導電線との間の交点における界面領域の多層アレイに設けられる。

(もっと読む)

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

相変化メモリコーディング

【課題】取り付け工程に係る半田付け及び高温環境での熱事象を通じても、データを保持することができる相変化メモリデバイスの提供。

【解決手段】一部のセルとメモリに第一抵抗状態、及び他部のセルとメモリに第二抵抗状態を誘導することにより、データセットを表わすために、プレコーディング(pre−coded)することができる。前記データセットがコーディングされ、基板に取り付けられた後に、前記第一及び前記第二抵抗状態を感知することにより、前記データセットを読み取り、前記第一抵抗状態を第三抵抗状態に変化させ、前記第二抵抗状態を第四抵抗状態に変化させる。半田接合と他の熱サイクルプロセスの後、前記第一及び前記第二抵抗状態は、感知マージン(sensing margin)を維持する。より高速とより低い電力を使用すると、前記第三及び前記第四抵抗状態は、転移(transition)を引き起こす能力がある。

(もっと読む)

連続する電荷蓄積誘電体スタックを有する不揮発性メモリアレイ

【課題】連続する電荷蓄積誘電体スタックを有する不揮発性メモリアレイを提供する。

【解決手段】不揮発性メモリセルアレイの集積回路は、基板を覆う誘電体スタック層と、該誘電体スタック層下の該基板内のイオン注入領域とを有する。該誘電体スタック層は、ワード線とビット線とを介してアクセスされ不揮発性データを記憶する該誘電体スタック層の複数の箇所を含む平坦な領域に亘って連続している。

(もっと読む)

不揮発性フラッシュメモリ

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

集積回路デバイス、集積回路デバイスの製造方法およびデータとコードの保存方法

【課題】電気的に書き込み可能かつ消去可能な不揮発性メモリを有する集積回路デバイスの製造方法およびデータとコードの保存方法を提供する。

【解決手段】第1の動作アルゴリズムに従って第1のデータ用途のためのデータを保存する第1のメモリアレイと、第2の動作アルゴリズムに従って第2のデータ用途のためのデータを保存する前記半導体基板上の第2のメモリアレイと、を備え、前記第1のメモリアレイと前記第2のメモリアレイにおける電荷蓄積不揮発性メモリセルは、窒化物電荷トラッピング構造を備えた互いに略同一構造を有する複数のフラッシュメモリセルを含み、前記第1の動作アルゴリズムは、ホール注入によって書き込みすることと、電界アシストエレクトロン注入によって消去することを含み、前記第2の動作アルゴリズムは、エレクトロン注入によって書き込みすることと、ホール注入によって消去することを含むことを特徴とする集積回路デバイス。

(もっと読む)

1 - 10 / 27

[ Back to top ]