サーノフ コーポレーションにより出願された特許

1 - 10 / 59

発光装置及びその発光装置の蛍光体組成物の製造方法

【課題】xが0.0001〜0.2であり、微量のユーロピウム成分が効率を改善する量のプラセオジムで置換され、蛍光体組成物の平均粒子サイズが2〜12ミクロンである組成式(I)SrGa2S4:Eu:xGa2S3である蛍光体を形成する方法を提供する。

【解決手段】生成物中に所望の平均粒子サイズを実現するため適切な条件下で、SrSO4及びEu(OH)3とともにGa(OH)3を析出させることと、生成物又はその後に繰り返されるこのステップの生成物を粉砕し、粉砕された生成物を硫化水素中で焼成する2つのサブステップを、少なくとも1回実行することと、少なくとも1回、焼成された生成物をそれが溶けない溶媒中に懸濁させ、焼成された生成物の一部分を第2の部分を懸濁させたまま沈殿させるための時間を設けることと、懸濁させた部分又は沈殿させた部分の1つ以上の部分中の蛍光体を収集することとを含む方法。

(もっと読む)

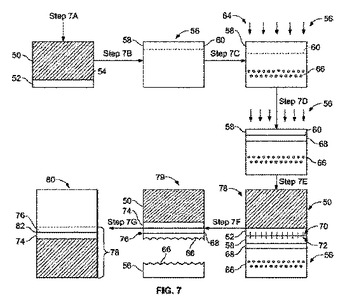

極薄シリコン・オン・インシュレータ基板を使用した背面照射型撮像装置

極薄セミコンダクタ・オン・インシュレータ基板(UTSOI)上に背面照射型半導体撮像デバイスを製作する方法が開示される。UTSOI基板は、機械的基板および実質的に機械的基板の上に重なる絶縁体層を備えるハンドル・ウェーハを設けることにより形成される。ドナー・ウェーハが設けられる。このドナー・ウェーハに水素が注入されて気泡層を形成する。気泡層の近位にドープ層を形成するために、ドナー・ウェーハが少なくとも1つのドーパントでドープされる。ハンドル・ウェーハの絶縁体層とドープ層の近位のドナー・ウェーハの表面との間でハンドル・ウェーハとドナー・ウェーハとを結合して、実質的に気泡層の下にある部分を有する結合されたウェーハを形成する。シード層を露出させるように、実質的に気泡層の下にある結合されたウェーハの一部分を除去する。エピタキシャル層が、実質的にシード層の上に重なって成長され、少なくとも1つのドーパントがエピタキシャル層の中へ拡散する。エピタキシャル層の成長が終了したとき、シード層と絶縁体層との間の境界面に、または同境界面の近くに最大値を有する正味のドーパント濃度が、シード層およびエピタキシャル層の中に存在する。  (もっと読む)

(もっと読む)

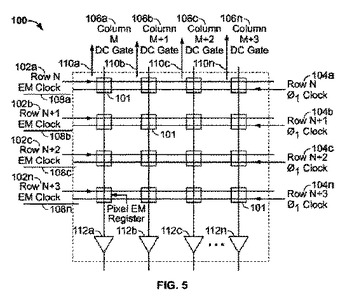

電子増倍撮像素子のためのゲイン整合

電子増倍(EM)ピクセルのアレイ内のゲインを等化する方法および装置が開示され、各ピクセルは電荷移動の方向性を得るための注入を用いる1つまたは複数の衝突電離ゲイン・ステージを有し、フェーズ1クロックド・ゲートと、EMクロックド・ゲートと、フェーズ1クロックド・ゲートとEMクロックド・ゲートの間に形成された2つのDCゲートとを備え、(a)複数のピクセルの少なくとも2つのピクセルのDCゲートおよびEMクロックド・ゲートのそれぞれに初期電圧を印加するステップと、(b)衝突電離ゲインの後に平均ピクセル強度値を得るために、複数のピクセルの少なくとも2つのピクセルに関連するフェーズ1クロック・ゲートおよびEMクロック・ゲートを所定の回数クロックするステップと、(c)DCゲートと、対応するEMクロックド・ゲートの電圧の差を選択的に調整するステップとを含む。  (もっと読む)

(もっと読む)

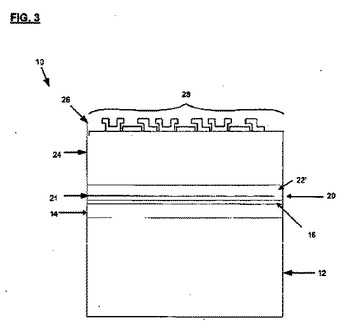

UTSOIウェーハ上に製作された背面照射型撮像装置の背面を電子的にピン止めする方法

ピン止めされた背面を有する背面照射型撮像装置を製作する方法が開示される。第1の絶縁体層が機械的基板の上に重なって形成される。導電層が第1の絶縁体層の上に重なって堆積される。第2の絶縁体層が導電層の上に重なって形成されて第1の構造体を形成し、導電層と第2の絶縁体層との間に境界面が形成され、導電層が、境界面を電気的にピン止めするように境界面の近位にバンド曲がりを引き起こす。個別のデバイス・ウェーハの中に水素が注入されて気泡層を形成する。デバイス・ウェーハの上に重なる最終絶縁体層が形成されて第2の構造体を形成する。第1の構造体と第2の構造体とが結合されて、結合されたウェーハを形成する。実質的に第2の絶縁体層の上に重なる半導体材料を含むシード層を露出するために、気泡層の下にある結合されたウェーハの一部分が除去される。  (もっと読む)

(もっと読む)

発光装置

【課題】電界発光装置と組み合わせることによって光の放射または色度を変更するのに適した赤色蛍光体を提供すること。

【解決手段】発光ダイオード及び蛍光体を備える発光装置であって、蛍光体は、SrXCa1−XS:Eu2+,Y(ここでXは0.3〜0.8の数、Yは1以上の原子状またはイオン状ハロゲンである)を含む硫化ストロンチウムカルシウム蛍光体である発光装置。

(もっと読む)

背面照射型イメージング・センサの暗電流の低減およびその製造法

セミコンダクタ・オン・インシュレータ型基板上の背面照射型半導体イメージング・デバイス。デバイスは、絶縁体層と、絶縁体層との界面を有する半導体基板と、半導体基板上にエピタキシャル成長によって成長させたエピタキシャル層と、面が半導体基板と絶縁体層との界面の反対側にありイメージング部品がエピタキシャル層内の接合を備える、エピタキシャル層の面に近接するエピタキシャル層中の1つまたは複数のイメージング部品とを備え、半導体基板およびエピタキシャル層は、絶縁体層と半導体基板との界面からの所定の距離において最大値を有しプロファイルの両側において最大値から単調減少する純ドーピング濃度を示す。ドーピング・プロファイルは、暗電流キャリアがデバイスの前面側に侵入することを妨げる「不感帯」として機能する。  (もっと読む)

(もっと読む)

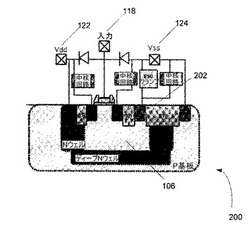

集積回路のためのCDMESD保護

【課題】改良された静電放電(ESD)保護回路、より詳細には、集積回路(IC)の保護回路におけるデバイス帯電モデル(CDM)ストレスの場合に対する改良を提供すること。

【解決手段】本発明は、集積回路(IC)のためのデバイス帯電モデル(CDM)静電放電(ESD)保護回路を提供する。ESD保護回路は、第1の導電タイプの基板と、基板上の第1のウェルに形成され、パッドに結合された第2の導電タイプのMOS構成部分と、第1のウェルと基板を隔離するための第1のウェルと基板との間に形成された第2の導電タイプを有する隔離ウェル/領域と、を含む。加えて、回路は、隔離されたウェル/領域に結合されたESDクランプを含む。通常電力の動作中、ESDクランプは開放されている。CDM ESD事象中、基板およびMOS構成部分内に蓄積されたCDM電荷は、ICへの損傷を防止するためにESDクランプにより取り除かれる。

(もっと読む)

改善された静電放電保護のための方法および装置

【課題】従来技術の短所を克服する異なった電力領域間のインターフェースのESD保護のための領域間保護技術を提供すること。

【解決手段】多数の電力領域を持つ集積回路(IC)の保護のための領域間静電放電(ESD)保護回路を有する装置。ESD事象に応じて、保護回路は異なった電力領域間のESD保護を提供する。特に、保護回路は1つの電力領域に結合された少なくとも1つのクランプを含み、同クランプはESD事象の発生中に電流を伝導して、2つの異なった電力領域間のインターフェース回線に余分な電流を提供する。また、この余分な電流は、インターフェース回線上のインピーダンス要素にかかる電圧を上昇させ、それにより、ESD保護のための設計の余裕を改善し、かつ、IC製品のためのより優れたESD保護能力を提供する。

(もっと読む)

ウェル電位トリガによるESD保護

【課題】ESD保護を可能にするための集積回路を提供すること。

【解決手段】集積回路は、基板領域、ソース、ドレイン、およびソース領域とドレイン領域の間に配設されたチャネル領域上に形成されたゲート領域を有する少なくとも1つのインターリーブされたフィンガーを有するトランジスタ・デバイスを含む。トランジスタ・デバイスはさらに、基板領域の電位を測定するためのソース領域に隣接して形成された少なくとも1つの高濃度ドープ接合を含む。集積回路はさらに、少なくとも1つの高濃度ドープ接合に結合されたスイッチング回路を含み、電位をスイッチング回路に転送して、全ESD電流を流すよう、または全ESD電流が流れるようにトリガするようになっている。

(もっと読む)

マルチフィンガ・ターンオンのための同時及び分散自己バイアス法を用いた静電放電(ESD)保護デバイス

【課題】保護されている回路を有する半導体集積回路(IC)のためのマルチフィンガ型NMOS利用のESD保護回路を提供する。

【解決手段】各フィンガが、それぞれICのI/Oパッド20とアース15との間に接続されているドレイン及びソースと、フィンガをバイアスするための各フィンガのゲートとを有する、マルチフィンガ型NMOSトランジスタ100と、ICのI/Oパッドに接続されているソースと、ICの第1の電源90に接続されているゲートとを備えるPMOSトランジスタ311を有するESD検出器310と、ICの電源ラインとアースとの間に形成されている寄生容量900と、第1のダイオード321を有する転送回路320であって、カソード及びアノードが、それぞれ、PMOSトランジスタのドレイン及びNMOSトランジスタの各フィンガのゲートに接続されている転送回路320と、を備える。

(もっと読む)

1 - 10 / 59

[ Back to top ]