Fターム[2C162FA15]の内容

電磁気プリンタ及び光プリンタ (19,948) | 光プリンタ (7,365) | ドットにより画像を形成するもの (7,364) | 記録素子 (4,222) | 発光素子の種類 (2,029)

Fターム[2C162FA15]の下位に属するFターム

Fターム[2C162FA15]に分類される特許

1 - 20 / 49

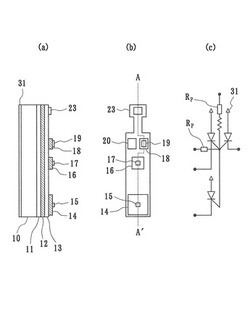

自己走査型発光素子アレイ

【課題】転送速度を改善しながら正常な転送を実現できる自己走査型発光素子アレイを提供する。

【解決手段】シフト部/発光部の島とゲート負荷抵抗の島とを分離せずに一体化する。ゲート負荷抵抗用の電極が無くなるので、ゲート負荷抵抗の電極23とp型ゲート層13との間に存在した接触抵抗が無くなる。その結果、ゲート抵抗が小さくなり、転送速度が増大する。

(もっと読む)

発光装置、プリントヘッドおよび画像形成装置

【課題】安定に動作し共通化が図れる発光装置等を提供する。

【解決手段】発光装置65は、発光チップ実装基板62上に、光源部63が主走査方向であるX方向に構成されている。光源部63は、それぞれ複数の発光素子を備える20個の発光チップC1〜C20を、二列に千鳥状に配置して構成されている。さらに、それぞれの発光チップC1〜C20の発光素子を順に点灯させるために指定する信号(転送信号)を供給する転送信号供給回路66を備えている。そして、発光チップCの発光素子の光量を補正するためのデータ(補正データ)を格納した光量補正データメモリ67を備えている。発光装置65と制御部の発光装置駆動回路33との間を信号の送受信を行うためのケーブル35で接続する。

(もっと読む)

発光装置、プリントヘッドおよび画像形成装置

【課題】配線数を抑制しつつ、同一チップ内で複数の発光素子を同時に点灯させる。

【解決手段】発光チップCは、発光サイリスタL1、L2、L3、…、転送サイリスタT1、T2、T3、…、設定サイリスタS1、S2、S3、…、設定許可サイリスタTE1、TE2、消灯サイリスタTR1、TR2を備え、番号nの転送サイリスタTnのゲート端子Gtnが、番号(2n−1)の設定サイリスタS2n−1のゲート端子Gs2n−1と番号2nの設定サイリスタS2nのゲート端子Gs2nとに、接続抵抗Rxを介して接続されている。設定サイリスタSのゲート端子Gsは、同じ番号の発光サイリスタLのゲート端子Glと接続抵抗Ryを介して接続されている。発光サイリスタLのゲート端子Glは、発光サイリスタLに対応して設けられた接続抵抗Rzを介して電源線71に接続されている。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】クロック駆動回路の出力端子数の削減により、回路規模を削減する。

【解決手段】発光サイリスタ210のカソードがLレベルにされると、アノード・カソード間には電圧が印加される。一方、走査回路部100における各走査サイリスタ111のゲートと、発光サイリスタ210の各ゲートとがそれぞれ接続されているため、走査サイリスタ111のゲート・カソード間にも電圧が印加される。この時、走査回路部100により発光指令されている発光サイリスタ210のゲートのみを選択的にHレベルとすることで、発光指令されている発光サイリスタ210がターンオンする。特に、クロック駆動回路69の3つの出力クロックパルスCK1R,CK2R,CKCを波形整形回路80で波形整形した2相のクロックCK1,CK2により、走査回路部100を駆動しているので、クロック駆動回路69の出力端子数を削減できる。

(もっと読む)

駆動回路、駆動装置、プリントヘッド及び画像形成装置

【課題】多数の発光サイリスタが並列接続されていることに起因して生じる駆動波形の遷移時間の増大を軽減する。

【解決手段】プリントヘッド13は、走査回路部100及び主発光部200を有し、これらがデータ駆動部60及びクロック駆動回路70に接続されている。主発光部200は、複数段の発光サイリスタ210により構成されている。走査回路部100は、クロック駆動回路70から供給される2相の第1、第2クロックC1,C2により駆動され、主発光部200にトリガ電流を流してオン/オフ動作させる。非発光時におけるデータ端子DAの電位を分圧抵抗64,65で分圧することにより、多数の発光サイリスタ210−1〜210−nが並列接続されていることに起因して生じる駆動波形の遷移時間の増大を軽減することが可能となる。

(もっと読む)

発光サイリスタ、光源ヘッド、及び画像形成装置

【課題】ゲート層全体が発光層として機能する場合に比べて、温度変動によって生じる出射光の光量変動が少ない発光サイリスタ、光源ヘッド、及び画像形成装置を提供する。

【解決手段】本実施の形態のRC構造を有する発光サイリスタ100では、アノード層として機能するp型AlGaAs系のDBR層106とカソード層として機能するn型AlGaAs系のDBR層112との間に積層されたゲート層108のうち、発光層をバンドギャップの小さいp型AlGaAs系の発光層108Bとし、一方、残りのゲート層108を発光層108Bよりもバンドギャップ(DBR各層のバンドギャップの平均値)が大きいn型AlGaAs系のDBRゲート層108Aとしている。

(もっと読む)

発光チップ、プリントヘッドおよび画像形成装置

【課題】高速化が図れる発光チップ等を提供する。

【解決手段】発光チップCa1(C)は、基板80上に列状に配列された発光サイリスタL1、L2、L3、…からなる発光サイリスタ列、転送サイリスタT1、T2、T3、…からなる転送サイリスタ列および設定サイリスタS1、S2、S3、…からなる設定サイリスタ列を備えている。そして、転送サイリスタT1、T2、T3、…をそれぞれ番号順に2つをペアにしてそれぞれの間に結合ダイオードD1、D2、D3、…、転送サイリスタT1、T2、T3、…と設定サイリスタS1、S2、S3、…との間に接続抵抗Rx1、Rx2、Rx3、…、設定サイリスタS1、S2、S3、…と発光サイリスタL1、L2、L3、…との間に接続抵抗Ry1、Ry2、Ry3、…を備えている。さらに、電源線抵抗Rz1、Rz2、Rz3、…を備えている。

(もっと読む)

発光サイリスタ、光源ヘッド、及び画像形成装置

【課題】本構成を有しない場合と比較して、キャリアの発光再結合の確率が向上された発光サイリスタ、光源ヘッド、及び画像形成装置を提供する。

【解決手段】本実施の形態の発光サイリスタ100では、p型AlGaAs系のアノード層106とn型AlGaAs系のカソード層112との間に積層されたゲート層108を、p型AlGaAs系のアノード層106側から順に、バンドギャップが小さいn型AlGaAs系のトラップ層108A2、バンドギャップが大きいp型AlGaAs系のDBRゲート層108B1、及びバンドギャップが小さいp型AlGaAs系の発光層108B0が積層されるように構成している。

(もっと読む)

発光素子アレイ、発光装置および画像形成装置

【課題】 少ない駆動用ICで時分割駆動することができる発光素子アレイおよびそれを用いた小形な発光装置ならびにその発光装置を備える画像形成装置を提供する。

【解決手段】 n(nは2以上の整数)個のスイッチ用サイリスタSと、前記スイッチ用サイリスタSのNゲート電極dに個別に接続されるn本の信号伝送路GHと、前記n本の信号伝送路GHのうちのいずれか1つとNゲート電極bが接続される複数の発光用サイリスタTとを含んで発光素子アレイチップ1を構成する。前記n個のスイッチ用サイリスタSのNゲート電極dには選択用サイリスタUのアノードeが接続され、選択用サイリスタUのNゲート電極fは共通のセレクト信号入力端子CSGに接続される。ローレベルのセレクト信号が入力されて選択状態になっている発光素子アレイのみを発光させることで、発光信号およびゲート信号を複数の発光素子アレイ間で共用する時分割駆動が実現できる。

(もっと読む)

光プリンタヘッドおよび画像形成装置

【課題】 画像形成装置における発光素子の位置、および、画像形成装置におけるレンズアレイの位置、の双方を比較的高い精度で設定することができる、簡素な構成の光プリンタヘッドを提供すること。

【解決手段】 本発明の光プリンタヘッド30は、基体33と、基体33上に搭載された発光素子アレイ34と、発光素子アレイ34の上方に配置されたレンズアレイ35と、支持部材31とを備えており、支持部材31は、基体33が接合された基体支持面31Afと、レンズアレイ35が接合された、基体支持面31Afに略垂直なレンズ支持面31Bfと、光プリンタヘッド30の取付位置を規定する位置決め孔312a、312bとを有しており、位置決め孔312a、312bは、発光素子アレイ34が搭載された基体33の一方の主面33Aaよりも上側に配置されている。

(もっと読む)

発光装置、発光装置の駆動方法、発光チップ、プリントヘッドおよび画像形成装置

【課題】消費電力を抑制した発光装置等を提供する。

【解決手段】発光装置は、それぞれが、基板80と、基板80上に列状に設けられた発光サイリスタL1、L2、L3、…を備える発光部102と、基板80上に、発光サイリスタL1、L2、L3、…に対応して設けられた転送サイリスタT1、T2、T3、…を備える転送部101とを備える、複数の発光チップCと、それぞれの発光チップCの転送サイリスタT1、T2、T3、…を順にオン状態が伝播するように第1転送信号φ1および第2転送信号φ2とを送信するとともに、いずれかの転送サイリスタTをオフ状態からオン状態に移行させる期間において転送部101に流れる電流に対して、この期間ののち次にオン状態にする転送サイリスタTをオフ状態からオン状態に移行させるまでの期間に流れる電流を絶対値において小さく設定する転送信号発生部120と、を備えている。

(もっと読む)

発光装置、プリントヘッドおよび画像形成装置

【課題】配線の数を抑制できる発光装置等を提供することを目的とする。

【解決手段】発光装置65の回路基板62には、発光チップ群#aに属する発光チップCa1〜Ca20および発光チップ群#bに属する発光チップCb1〜Cb20および信号発生回路110が搭載されている。信号発生回路110は、発光チップ群#aおよび#bに対して許可信号φEを送信する許可信号発生部130と、発光チップ群#aの発光チップCaと発光チップ群#bの発光チップCbとを組にして、組毎に書込信号φW1〜φW20を送信する書込信号発生部150とを備えている。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】クロック駆動回路の出力端子数の削減により、回路規模を削減する。

【解決手段】クロック駆動回路70内のオープンドレーン形インバータ80とスリーステート形出力バッファ90とにより、走査回路部100を駆動するための2相の第1及び第2クロックを生成している。発光サイリスタ210のカソードがLレベルにされると、アノード・カソード間には電圧が印加される。一方、抵抗130を介して供給される第2クロックによりシフト動作を開始する走査回路部100における各走査サイリスタ110のゲートと、発光サイリスタ210の各ゲートとがそれぞれ接続されているため、走査サイリスタ110のゲート・カソード間にも電圧が印加される。この時、走査回路部100により発光指令されている発光サイリスタ210のゲートのみを選択的にHレベルとすることで、発光指令されている発光サイリスタ210がターンオンする。

(もっと読む)

発光装置、プリントヘッドおよび画像形成装置

【課題】加熱と冷却との繰り返しによる基板の変形により光学素子が傾くことによる光軸のずれを抑制した発光装置等を提供する。

【解決手段】回路基板62は、一方の表面に発光チップS1〜S40(図5では発光チップS3とS4とを示す。)を備えるとともに、第1信号配線層301および第2信号配線層302を備え、第1信号配線層301の構成する信号配線301aの幅方向の中心位置C1と、第2信号配線層302の構成する信号配線302aの幅方向の中心位置C2とが、回路基板62の短手方向であるY方向において、ずれて設けられている。

(もっと読む)

画像形成装置および画像形成方法

【課題】複数の画像形成部で形成される像をそれぞれ像担持体に転写してカラー画像を形成する装置において、各画像の書き出し位置を高精度に調整して高品質なカラー画像を形成する。

【解決手段】色別垂直同期信号Vsyncを受信したタイミングT1での感光体ドラム21の回転位置に応じた待機時間だけタイミングT1から遅れて遅延垂直同期信号が出力され、同信号に基づき感光体ドラムの露光が開始される。このため、色別垂直同期信号Vsyncの受信タイミングT1から一次転写開始タイミングT3までの時間を、回転ムラの影響を受けることなく、一定になっており、各画像形成ステーションで形成される画像の先端位置が相互に一致して画像先端色ズレが抑制される。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】同時点灯する複数の発光サイリスタのゲート間に流れる回り込み電流を略ゼロにして、発光出力の変動を防止する。

【解決手段】多数の発光サイリスタが配列され、これらが複数の組(例えば、偶数と奇数の組)に分けられ、各組の発光サイリスタ列が、複数のドライバ181により、各組毎に時分割に駆動されるプリントヘッドにおいて、同一組に属する発光サイリスタ列における各発光サイリスタのゲートを、複数の発光サイリスタのゲート間を電気的に分離するための分離回路としての個別のバッファ(例えば、163)を介して、共通配線GLにそれぞれ接続して共通に駆動する構成になっている。そのため、同時点灯する発光サイリスタのゲート間に流れる回り込み電流を略ゼロにすることができる。これにより、回り込み電流が流れることで生じる発光出力の変動を防止できる。

(もっと読む)

発光装置、発光装置の駆動方法、プリントヘッドおよび画像形成装置

【課題】複数の発光素子を並行して点灯しうる発光チップを用いた発光装置の配線数の増加を抑制する。

【解決手段】発光装置65の発光部63は、回路基板62上に、発光チップ群#a(発光チップCa1〜Ca5)、発光チップ群#b(発光チップCb1〜Cb5)、…が主走査方向に二列に千鳥状に配置して構成されている。これらの発光チップCは、発光チップ組#1(発光チップCa1、Cb1、Cc1、Cd1)、発光チップ組#2(発光チップCa2、Cb2、Cc2、Cd2)、…に分けられている。そして、転送信号φ1、φ2、許可信号φEが、発光チップ群(#a〜#d)毎に共通に送信され、書込信号φWは、発光チップ組(#1〜#5)毎に共通に送信され、点灯信号φIは、発光チップC毎に個別に送信される。

(もっと読む)

駆動回路、駆動装置及び画像形成装置

【課題】サイリスタを確実にオフ状態に維持できるのに十分な電位を印加することができ、かつ、そのような電位の印加が長時間続かないようにすることで、サイリスタの劣化を防ぐ。

【解決手段】複数のゲート駆動部(401、402)の各々は、対応する組に属する複数のサイリスタのゲートを駆動する期間(S1N=Low)には第1の電位(2V)を出力し、対応する組に属する複数のサイリスタのゲートを駆動しない期間(S1N=High)のうち、アノード駆動の立ち上がり部分には、第1の電位よりも高い第2の電位(5V)を出力し、対応する組に属する複数のサイリスタのゲートを駆動しない期間(S1N=High)のうち、アノード駆動の立ち上がり部分以外の期間には、第2の電位よりも低い第3の電位(3V)を出力する。

(もっと読む)

面発光素子、面発光素子アレイ、書き込みヘッドおよびプリンタ

【課題】光量の減少を防止しつつ金属配線の断線を防止することができる面発光素子および面発光素子アレイを提供する。

【解決手段】発光素子アレイは、p型の半導体基板と、第1のp型の半導体層14と、第2のn型の半導体層16と、第3のp型の半導体層18と、第4のn型の半導体層20とを有する、サイリスタ構造の面発光素子である。第4の半導体層20は、ゲート電極24のためにメサ状にエッチングされ、第3の半導体層18との間に段差部Sを生じさせる端部(エッチング面)EDを有する。端部EDには、順方向のメサとなる第1の側部と、第1の側部に対向し順方向のメサとなる第2の側部と、逆方向のメサとなる第3の側部とからなる迫出し部40が形成されている。

(もっと読む)

発光素子およびその製造方法、ならびに、これを備える光プリントヘッド

【課題】 小型化が可能な発光素子およびその製造方法、ならびに、これを備える光プリントヘッドを提供する。

【解決手段】 本発明の実施形態の一例である発光素子アレイ11は、[110]方向および[1−10]方向に沿って切断されて、矩形状に形成された化合物半導体からなる素子基板20と、素子基板20の上に連続してエピタキシャル成長された化合物半導体層からなる発光素子40と、[110]方向および[1−10]方向の端部に、他方方向に沿って延び、素子基板20の上に連続してエピタキシャル成長された化合物半導体からなる化合物層50と、を含む。

(もっと読む)

1 - 20 / 49

[ Back to top ]