Fターム[2F002CB01]の内容

Fターム[2F002CB01]の下位に属するFターム

Fターム[2F002CB01]に分類される特許

1 - 10 / 10

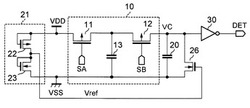

発振停止検出回路、半導体装置、時計および電子機器

【課題】 難しいプロセス条件のコントロールを必要とせず、所期の性能を持ったものを安価に製造することができる発振停止検出回路を提供する。

【解決手段】 Pチャネルトランジスター11および12は、発振回路の出力信号から生成される制御信号SA、SBに従ってスイッチング動作して電荷を転送し、キャパシター20を充電する。インバーター30は、キャパシター20の充電電圧VCを2値化し、発振状態判別信号を出力する。Nチャネルトランジスター26は、キャパシター20を放電させるトランジスターである。基準電圧発生回路21は、ゲートおよびソースが互いに接続されたデプレッション型Pチャネルトランジスター22と、ゲートおよびドレインが互いに接続されたNチャネルトランジスター23とを直列接続してなるものであり、Nチャネルトランジスター23とNチャネルトランジスター26はカレントミラーを構成する。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

車両用計器

【課題】スイッチのオフ時は第1の制御手段と電源との接続が絶たれるシステムであってもバッテリ接続状態に応じてリセット処理を行うことが可能な車両用計器を提供する。

【解決手段】

指針式計器1と、第1の電源供給ラインL1を通じて電源4と接続され指針式計器1を制御する第1の制御手段2とを備え、第1の電源供給ラインL1上に設けられた起動スイッチ(スイッチ)5のオンにより電源4と第1の制御手段2とが接続される車両用計器装置において、第2の電源供給ラインL2を通じて電源4と接続され、第2の電源供給ラインL2による電源供給が遮断された場合に電源遮断情報を記憶する第2の制御手段3を有し、第1の制御手段2は起動スイッチ5のオン時、前記電源遮断情報の有無に基づいて指針式計器1のリセット処理を実行する。

(もっと読む)

リアルタイムクロック、およびリアルタイムクロックのデータ記録方法

【課題】記憶されたイベントデータの信頼性を向上させることのできるリアルタイムクロックを提供する。

【解決手段】上記課題を解決するためのリアルタイムクロック10は、イベント検出信号が外部から入力されたことを検出するイベント検出回路20と、発振回路16から出力された信号に基づいて前記時刻データを生成する計時回路18と、メモリ40と、イベント検出回路20により前記イベント検出信号の入力を検出した場合、リアルタイムクロック10の動作状態を示す付加データと、計時回路18により生成された前記時刻データとを有するイベントデータをメモリ40に記録する制御回路42と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路

【課題】発振回路において発振動作が行われているか否かを判定する発振停止検出回路を内蔵した半導体集積回路において、電源電位が立ち上がる際の誤検出を防止する。

【解決手段】この半導体集積回路は、クロック信号又は反転クロック信号がゲートに印加されて交互にオン/オフする複数のトランジスタが直列に接続され、第1の電源電位から正の電荷を移送するトランジスタ列と、複数のトランジスタによって移送される電荷を蓄積する複数のコンデンサと、最終段のコンデンサの端子をプルダウンするプルダウン素子と、最終段のコンデンサの端子の電位がゲートに印加され、第2の電源電位がソースに供給されるNチャネルMOSトランジスタと、該NチャネルMOSトランジスタのドレインをプルアップするプルアップ素子と、該NチャネルMOSトランジスタのドレイン電位に基づいて出力信号を生成する論理回路とを具備する。

(もっと読む)

発振回路と定電圧電源回路とを含む処理装置

【課題】発振回路用の定電圧電源回路が間欠的に動作する場合に、発振回路に安定して発振させるための技術を提供する。

【解決手段】処理装置は、第1の電源電圧を発生させる第1の定電圧電源回路と、第1の電源電圧で動作して発振信号を生成する発振回路と、第1の定電圧電源回路から出力される第1の電源電圧を増大させるための電圧増大回路と、第1の定電圧電源回路の動作を制御する動作制御回路と、を備える。動作制御回路は、第1の期間に、第1の定電圧電源回路を間欠的に動作させ、電圧増大回路が第1の定電圧電源回路から出力される第1の電源電圧を増大させる第2の期間に、第1の定電圧電源回路を連続的に動作させる。

(もっと読む)

半導体装置

【課題】製造プロセスの追加やトランジスタ動作の不安定さを招くことなく、発振用インバータを用いて構成された発振回路を搭載する半導体装置を提供する。

【解決手段】本発明の半導体装置において、複数のMOSトランジスタはノーマリーオフ型のもので、製造プロセスが許容する最小寸法に等しいゲート長において所定の閾値を有し、最小寸法に比較してゲート長が大きくなるにつれて閾値の絶対値が小さくなる特性を有する。本発明の半導体装置は、最小寸法以上の範囲で、相対的に長いゲート長を有する第1のMOSトランジスタからなる第1の発振用インバータと、相対的に短いゲート長を有する第2のMOSトランジスタからなる第2の発振用インバータと、第1および第2の発振用インバータに電源電圧を供給する電源配線と、電源電圧に応じて、第1および第2の発振用インバータの一方を動作可能とする選択回路とを有する。

(もっと読む)

発振制御装置及び同期システム

【課題】標準機関が有する標準発振器の設置場所から遠隔地にある発振器の周波数を、標準発振器の周波数にリアルタイムで同期可能とする。

【解決手段】発振器3は、GPS受信アンテナ30によりGPS信号を受信し、信号処理部31は、GPSタイムに同期した周波数fgの信号を生成し、周波数比較部32は、GPS信号の周波数fgと、周波数発振部36から出力された発振信号の周波数fbを比較し、(fb−fg)を算出する。データ送受信部34は、国家標準発振器22から出力された発振信号の周波数faと、前記GPS信号の周波数fgとの比較結果(fa−fg)を国家標準機関2から取得し、偏差算出部33は、その取得された比較結果(fa−fg)と、周波数比較部32での比較結果(fb−fg)から、偏差(fb−fa)を算出し、周波数制御部35は、この偏差が0になるように周波数発振部36を制御する。

(もっと読む)

時刻同期装置

【課題】高速に時刻補正を行い標準時刻に一致させる時刻同期装置を提供する。

【解決手段】NTPサーバ2とのNTP制御を行うプロセッサ3と、NTPサーバ2から受け取った標準時刻とのずれを平準化する時刻補正値平準化部4と、現在時刻を表示する時刻レジスタ5と、オッシレータ6と時刻補正値平準化部4とから時刻レジスタ5の時刻を歩進させるためのクロックを生成するクロック生成部7とを設ける。

(もっと読む)

電波修正時計、及び標準電波受信方法

【課題】 受信した標準電波の変調部(又は非変調部)間の差が小さい場合であっても、正確に波形を判別することができる電波修正時計、及び標準電波受信方法を提供する。

【解決手段】 発振回路5からサンプリング用に出力される規定のクロック信号を基にして、当該規定のクロック信号とは発振タイミングの異なるクロック信号をサンプリング加算回路10により生成する。生成されたクロック信号は、サンプリング回路4に出力されて発振回路5より出力された規定のクロック信号に加算される。サンプリング回路4は、このようにして加算されたクロック信号に従って復調波形のサンプリングを行う。これにより、マイコンにより予め規定されているサンプリング回数が増加し、サンプリング回路4のサンプリング周期が実質的に短縮されて波形判別の信頼性が向上する。

(もっと読む)

1 - 10 / 10

[ Back to top ]