Fターム[2G003AF00]の内容

個々の半導体装置の試験 (15,871) | 試験結果の処理 (765)

Fターム[2G003AF00]の下位に属するFターム

数値表示、電圧計、電流計 (25)

メモリ記憶 (196)

CRT、XYレコーダ (89)

印字記録 (7)

選別器を駆動 (78)

良否の指示 (287)

音響による表示、警報 (35)

マーキング (33)

発光素子による表示 (8)

Fターム[2G003AF00]に分類される特許

1 - 7 / 7

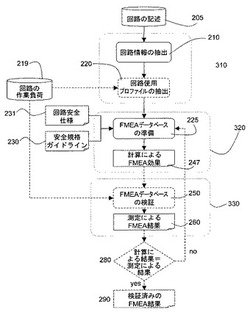

集積回路の故障モード・影響分析を実行するための方法、およびそのためのコンピュータプログラム製品

【課題】集積回路の故障モード・影響解析を実行する為の方法およびそのためのプログラムを提供する。

【解決手段】設計中の集積回路のFMEAデータベースを準備するステップ225と、FMEAデータベースからFMEA結果を計算するステップ247とを含む。さらに、集積回路の記述205から情報を自動的に抽出するステップ210を含んでおり、該情報抽出210が、集積回路の情報を読み出すこと、該回路を不変かつ基本的なセンシティブゾーンSZに区分けすること、前記FMEAデータベースの準備のステップ225において前記情報を使用すること、を含んでいる。更に、この方法は、随意によるFMEA検証段階250を含み、FMEA計算結果247がFMEA測定結果260と比較されるステップ280を含み、FMEA検証済み結果290が得られる。

(もっと読む)

半導体装置の検査方法および検査装置

【課題】Overkillそのものを防止する半導体装置の検査方法および検査装置を提供する。

【解決手段】検査用ソケットに複数の半導体装置を順に装着し、電気的特性を検査して各半導体装置毎に検査データを蓄積し、検査済み半導体装置を検査データに基づいて良否選別する半導体装置の検査方法において、前記電気的特性の検査には、接触テストが含まれ、該接触テストに合格した半導体装置の、接触テストにおける測定値を蓄積する工程と、該蓄積された接触テストの測定値から演算値を生成する工程と、予め定めた基準値と前記接触テストでの測定値から得られた演算値とを比較して、検査用ソケットの不良を予測する工程とを有する。

(もっと読む)

半導体レーザ素子の検査方法とその装置

【課題】高速短パルス駆動においても光出力値を正確に測定できる半導体レーザの電流−光出力特性の経時変化を検査する方法とその装置を提供する。

【解決手段】パルス電流により駆動される半導体レーザ素子1の電流−光出力特性の経時変化を検査する半導体レーザの検査装置10において、半導体レーザ素子1にパルス電流を出力する駆動回路20が、所定時刻からボトム時刻Tbまでパルス電流をボトムレベルに設定して、ボトム時刻Tb前の所定時間の間、前記半導体レーザ素子1よりボトムレベルのパルス光を放射させることを特徴とする。

(もっと読む)

半導体コンポーネント部品中の製造エラーの位置を検出する方法および装置

【課題】簡単な方法により、半導体コンポーネント部品に損傷を与えることなく、製造エラーの位置を突止める。

【解決手段】半導体コンポーネント部品10中に過剰な電荷キャリアを発生させ、半導体コンポーネント部品10中の電位を決定することによって半導体コンポーネント部品10中の製造エラーの位置を突止める。半導体コンポーネント部品10を損傷させずに簡単な方法により製造エラーの位置を突止めるために、半導体コンポーネント部品10が刺激されてルミネセンス状態になるようにされ、また、局地化された解像されたルミネセンス強度分布が決定されて半導体コンポーネント部品10中の電位の局地化された解像された分布が決定される。

(もっと読む)

固体撮像素子の検査方法および検査装置

【課題】 固体撮像素子の検査に要する処理時間を短縮して効率的に検査することができる固体撮像素子の検査方法および検査装置を提供する。

【解決手段】 固体撮像素子の検査装置100は、素子駆動手段23と、光学条件設定手段25と、撮像画像データに対して画像処理を施す演算手段29と、固体撮像素子21の良否判定を行う判定手段とを備える。演算手段29は、検査装置100内部に備わる内部演算部35と、検査装置100に通信手段11を介して接続された外部演算部43A,43Bとを有し、更に内部演算部35の負荷状況が所定の状況範囲を超える場合に、外部演算部43A,43Bに負荷を分散させる制御部31を備える。

(もっと読む)

MISFETの寿命予測方法

【課題】高誘電率半導体デバイスの寿命を正確に予測することを目的とする。

【解決手段】本発明は、集積回路寿命におけるホットキャリア注入の効果を決定するためのMISFETの試験方法を提供する。本方法は、ドレイン電圧を前記負荷電圧に等しい値に維持する間中、高誘電率誘電体を有するゲートへ正の負荷電圧を印加する。通常の動作電圧よりも大きい負荷電圧の使用が、集積回路の故障及び劣化を加速させる。スレッショルド電圧,トランスコンダクタンス,リニアドレイン電流,飽和ドレイン電流などの電気的パラメータを観測する。観測された電気的パラメータにおけるシフトがデバイス故障を示す。ゲート負荷電圧に対する被加速デバイス寿命の対数をプロットすることによるデータ解析が行われる。動作条件下でのデバイス寿命は、所定のデバイス動作電圧に関するプロットを基に推定することにより予測される。

(もっと読む)

ノイズ検知回路

【課題】 簡単な構成でプロセス変動の影響を受けにくく、ノイズによる回路特性の変化が小さく、ノイズの検知と評価の等時性を必要としないノイズ検知回路を提供する。

【解決手段】 ノイズ検知回路の電源端子VDDと接地端VSSの間に直列接続した2個のNMOSトランジスタMN1,MN2の内のトランジスタMN2を導通させてノードN1の電荷を放電した後に遮断させ、その後トランジスタMN1を導通させてノードN1を「VDD−Vthn」の電位に初期化し、その初期化時のノードN1の電位がアンテナ1に誘起されたノイズにより変化したとき、これを検知してノイズを検知する。

(もっと読む)

1 - 7 / 7

[ Back to top ]