Fターム[2G060DA21]の内容

電気的手段による材料の調査、分析 (24,887) | 電界効果トランジスタ(FET) (316) | 保護のための構成 (12)

Fターム[2G060DA21]の下位に属するFターム

Fターム[2G060DA21]に分類される特許

1 - 2 / 2

液体状態検知センサ

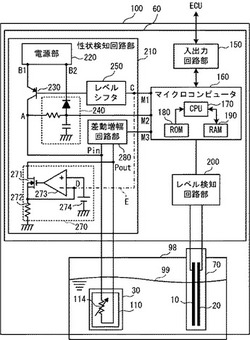

【課題】電源部と発熱抵抗体との間の通電経路で万が一グランドショートが発生しても、発熱抵抗体への通電回路および発熱抵抗体に繋がるバッテリに負荷がかかることを防止することができる液体状態検知センサを提供する。

【解決手段】電源部220と発熱抵抗体114との間の通電経路上の測定点Aはマイクロコンピュータ160の入力ポートM2に接続され、測定点Aの電位が測定されている。万が一電源部220と発熱抵抗体114との間にてグランドショートが発生した場合、発熱抵抗体114への通電時に測定点Aの電位はグランド電位となる。この状態(グランド電位)が検知されると直ちにトランジスタ230がOFFに制御され、発熱抵抗体114への通電が停止される。これにより、上記通電経路上に配置された電子部品等に高電圧が印加されたり、バッテリに負荷がかかったりするのを防止できる。

(もっと読む)

電気的構成部材

電気的構成部材(1)は、基板(2)を備えたセンサチップ及び/又はアクチュエータチップを有しており、その基板上にパッシベーション層(3)と、アクティブな表面領域(5a、5b)を有するセンサ構造及び/又はアクチュエータ構造が配置されている。チップは、カプセル部(6)によって包囲されており、そのカプセル部が開口部(7)を有し、その開口部が少なくとも1つのアクティブな表面領域(5a、5b)への通路を形成する。基板(2)上に、層スタックが配置されており、その層スタックは−パッシベーション層(3)から始まって基板(2)へ−少なくとも1つの第1の導体路層(15)、第1の電気的絶縁層(14)、第2の導体路層(17)及び第2の電気的絶縁層(16)を有している。第1の導体路層(15)は、チップの、開口部(7)によって覆われる領域の完全に外部に配置されている。第2の導体路層(15)の少なくとも1つの導体路が、センサ構造及び/又はアクチュエータ構造と接続されている。 (もっと読む)

1 - 2 / 2

[ Back to top ]