Fターム[2G132AA03]の内容

Fターム[2G132AA03]に分類される特許

1 - 20 / 151

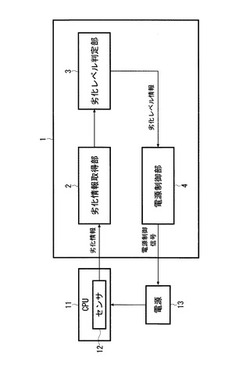

電子機器の保守装置、方法、及びプログラム

【課題】電子機器の通常動作を妨げることなく、CPUの経時劣化を保障し、電子機器の性能を維持することができるようにする。

【解決手段】保守装置1は、CPU11に内蔵されるセンサ回路12からCPU11の劣化に応じて変化する劣化情報をCPU11の通常動作時に取得する劣化情報取得部2と、劣化情報に基づいてCPU11の劣化の進行度を示す劣化レベルを判定する劣化レベル判定部3と、劣化レベルの増大に伴いCPU11に印加される電源電圧を増加させるように電源13を制御する電源制御部4とを備える。

(もっと読む)

試験管理装置

【課題】試験の信頼性を低下させることなく、試験時間を短縮する。

【解決手段】試験リスト保持部12は、被試験対象物に実施すべき複数の試験項目とその順番を規定した試験リストを保持する。対応テーブル保持部13は、各試験項目の結果値をランク分けし、各ランクと、省略または追加する試験項目とを対応付けたテーブルを保持する。試験結果値取得部22は、試験リストにしたがい実施された試験項目の試験結果値を取得する。ランク判定部23は、対応テーブル保持部13を参照して、試験結果値取得部22により取得された試験結果値をランク分けする。試験リスト管理部24は、ランク判定部23により決定されたランクに応じて試験リストの内容を適応的に変更する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】複数のコアチップが積層された半導体装置において、各コアチップにそれぞれ任意のイネーブル信号を供給するために必要な貫通電極の数を削減する。

【解決手段】インターフェースチップIFと複数のコアチップCC0〜CC7が積層されており、複数のコアチップCC0〜CC7は、貫通電極TSV1を介してインターフェースチップIFに共通接続されており、インターフェースチップIFは、貫通電極TSV1を介して複数のコアチップCC0〜CC7にイネーブル信号TLSEをシリアルに供給し、複数のコアチップCC0〜CC7は、イネーブル信号TLSEを構成する複数ビットのうち当該コアチップに割り当てられたチップ識別情報に対応するビットの論理レベルに基づいて活性化される。本発明によれば、イネーブル信号を供給するために必要な貫通電極の数を削減することが可能となる。

(もっと読む)

テスト回路を内蔵した集積回路

【課題】集積回路の動作を検証するために、波形測定装置のような高価で扱いが難しい測定装置を用いて端子の波形を測定していたので、測定装置の操作に不慣れな検証者には扱い難かった。本発明は、単体で簡単に動作検証ができる集積回路を提供することを目的にする。

【解決手段】マッピング制御回路を用いて既存の内蔵メモリの一部をテストデータ格納領域として確保し、サンプリング制御回路でサンプリングしたテストデータをテストデータ格納領域に格納する。また、テスト終了後にこの領域を開放するようにする。集積回路単体で動作検証でき、またテスト専用メモリが不要なので、チップサイズが増加しない。

(もっと読む)

論理検証シナリオ生成装置、及び、論理検証シナリオ生成プログラム

【課題】CPUの論理検証に用いる検証シナリオ、及び期待値の生成負荷を抑える。

【解決手段】RTL記述されたCPUの論理検証のためのテストプログラムを生成する論理検証シナリオ生成装置であって、テストライブラリと、期待値フォーマット記憶部と、検証命令アドレス、前命令空間、後命令空間、データ空間、分岐命令空間、スタック空間とを有するメモリモジュールであって、テストライブラリから順次選択した検証命令と前後命令組合せとに基づいて、検証命令アドレスに検証命令を、前命令空間に前命令を、後命令空間に後命令を記憶し、前命令が分岐命令である場合に前命令の分岐先アドレスに検証命令アドレスを記憶したメモリモジュールをテストプログラムとして生成するテストプログラム生成部と、テストプログラムの各命令について期待値フォーマットを取得し、当該命令をデコードしたデコード情報に基づいて期待値を生成する期待値生成部と、を有する。

(もっと読む)

故障検出方法、半導体装置、マイクロコンピュータ応用システム

【課題】故障検出の対象とされる回路のアナログ量を変化させて故障検出を行うことにより、故障検出精度を向上させる。

【解決手段】チューニング回路(104A)によって、所定の条件下で上記被故障検出回路(104B)のアナログ量を変更し、上記被故障検出回路におけるアナログ量の変化に基づく上記被故障検出回路の状態変化を、故障検出回路(103)によって判別して上記被故障検出回路の故障を検出する。これにより、故障検出回路(103)の出力を半導体装置の外部でモニタすることなく、上記被故障検出回路の故障を検出することができる。しかも、上記被故障検出回路におけるアナログ量の変化に基づく上記被故障検出回路の実際の状態変化を故障検出回路によって判別するようにしているため、故障検出の精度の向上を図ることができる。

(もっと読む)

解析システム及び半導体装置

【課題】LSI等の半導体装置内部の信号の遷移を容易に確認することが可能な解析システム及び半導体装置を提供すること。

【解決手段】半導体装置の内部において、解析対象となる内部信号が入力され、内部信号の遷移を検出すると所定のコードに変換して出力するとともに、内部信号の遷移を報知する報知信号を出力する符号化回路と、半導体装置の内部において、符号化回路から出力されるコードを格納する内部メモリと、半導体装置の外部において、符号化回路から出力される報知信号が入力され、内部信号の遷移タイミングを計時する計時回路と、半導体装置の外部において、計時回路で計時された時間情報を格納する外部メモリと、を備える。

(もっと読む)

電子部品及び検査システム

【課題】特別な検査装置を要することなく、基板への実装状態の適否を容易且つ迅速に検査可能な電子部品の提供。

【解決手段】デバイス1に内蔵されたCPU14は、I/F17が外部端末3から検査開始コマンドを受信したことを契機として検査処理を開始し、冗長端子11である検査用端子13をプルアップ抵抗付きの入力に切り替え、検査用端子13に所定電圧を印加し、検査用端子13の入力電圧を検出し、検出した入力電圧を検査結果として外部端末3へ送信する。

(もっと読む)

プログラマブル・ロジック・コントローラ、および、プログラマブル・ロジック・コントローラにおける故障診断方法

【課題】自己診断により入力回路部分の故障を検出することが可能なPLCを提供する。

【解決手段】制御処理回路40は、診断信号生成部43で生成した診断信号IT1〜ITを診断信号出力部44から出力し、AND回路30、信号入力部41を介して、故障判定部42へ取り込み、診断信号IT1〜IT4と信号入力部41から入力した入力信号DI1〜DI4とを、故障判定部42で比較し、一致しなかったとき、信号入力部41に故障ありと判定する。次に、制御処理回路40は、診断信号出力部44から出力した診断信号ET1,ET2を絶縁入力回路10のフォトカプラ12へ入力して、絶縁入力回路10のフォトカプラ11を動作させ、その出力信号d1〜d4を、信号入力部41を介して取得し、その入力信号DI1〜DI4を故障判定部42で期待値と比較し、一致しなかったとき、絶縁入力回路10に故障ありと判定する。

(もっと読む)

システムインパッケージとその試験方法

【課題】外部から直接にアクセスできない複数のチップのいずれが不良であるかを判定するBIST機能を有するシステムインパッケージ。

【解決手段】本発明のシステムインパッケージは、予め設定された論理の検査データを、システム内のアドレス空間における特定アドレスである隠し欠陥アドレスにて出力する不良発生源部11が設けられ、端子が外部端子に直接接続されない、他の複数のチップである、フラッシュメモリ2及びメモリコントローラ3と、内部配線である共通I/O線にて接続されたDRAM1を有しており、第2特殊MRSコマンドがコマンドレジスタに書き込まれ、BIST機能がイネーブルとなったテストモードの際、DRAM1における隠し欠陥アドレスがイネーブルとなり、共通I/O線に検査データを出力する。

(もっと読む)

劣化検出回路、劣化検出システム及び劣化検出方法

【課題】回路規模を増大することなくトランジスタの劣化具合を正確に評価することができる電圧出力回路、劣化検出システム及び劣化検出方法を提供すること

【解決手段】本発明にかかる劣化検出回路10は、電源(VDD)100と電源(VDD)100よりも電位が低い電源(GND)110との間に設けられたMOSトランジスタ30と、電源(VDD)100と電源(GND)110との間においてMOSトランジスタ30と直列に接続され、MOSトランジスタ30の劣化進行度よりも遅い劣化進行度を有する抵抗部20と、MOSトランジスタ30と抵抗部20との接点における電圧を、MOSトランジスタ30の劣化度を測定するために出力する劣化度測定用出力端子40と、を備えるものである。

(もっと読む)

ICチップ、自己診断方法、自己診断プログラム及びICカード等

【課題】動作不可能な状態になることなく確実に自己診断を実施し、信頼性を担保することができるICチップ及び自己診断方法等を提供する。

【解決手段】CPU9は、実行にかかるクロックが、外部から供給されるクロックであるか、又は内部で発信されるクロックであるかを判断し、前記外部から供給されるクロックであると判断した場合には、CPU9は、ATR信号が出力された後に、外部からコマンドが入力されるまでICチップ4を省電力状態に移行する。

(もっと読む)

半導体集積回路、故障検出方法及びマイクロコントローラ

【課題】出力部と同じ入出力端子に接続された入力部の故障を、出力部とは独立して検出可能な半導体集積回路を提供する。

【解決手段】入力部11と入出力端子P1との間にスイッチSW1を設け、入力部11と出力部12との間にスイッチSW2を設け、入力部11の検査時に、スイッチSW1は入力部11と入出力端子P1とを電気的に切り離し、スイッチSW2は入力部11と出力部12とを電気的に切り離し、入力値生成部13は、入力値を入力部11に入力し、故障判定部14は、入力値と、入力部11からの出力値とを比較し、入力部11の故障の有無を判定する。

(もっと読む)

電子部品の検査装置

【課題】BGAを用いた電子部品の接続箇所の検査を効率良く実施できるようにする。

【解決手段】電子部品1は、複数の接続端子を配列したBGAを用いて実装したCPU2を有する。CPU2の接続端子の検査は、全ての接続端子を複数のグループに分けて検査する。端子選択部23は、各グループから検査対象となる接続端子をターゲット端子として1つずつ選択する。モニタ部25で、各ターゲット端子と他の接続端子との短絡を各グループにおいて同時に検査する。各グループ内の全ての接続端子をターゲット端子に選択して検査を行ったら、処理を終了する。

(もっと読む)

半導体装置とその異常予測方法

【課題】動作異常を事前に予測し、故障箇所により異常動作時の動作を変更可能とする半導体装置と方法の提供。

【解決手段】第1のCPU101と、前記第1のCPUと同一又は同等の構成を有する第2のCPU102と、前記第1のCPUの出力と前記第2のCPUの出力を比較する比較器103と、を備え、前記第2のCPUは、前記第1のCPUよりも動作マージンが低くなるように作りこまれており、前記第1のCPUと前記第2のCPUへ同一の信号を入力し、第1のCPU101と第2のCPU102の出力の比較結果の不一致を検出することで、異常の予測が行われる。比較器での比較結果がエラーを示すとき、装置をリセットするリセット制御回路104を備えている。

(もっと読む)

LSI評価ボード装置

【課題】 本発明の課題は、プログラムされたユーザー論理を用いたLSIのプロトタイピングにおいて、評価精度を向上させることを目的とする。

【解決手段】 上記課題は、2つのデバイスで構成されるプロトタイピング環境を実装するLSI評価ボード装置は、有効なバストランザクションの検出に応じて、前記2つのデバイスの動作に係る回路構成のクロック停止を指示する第一指示回路と、前記クロック停止の指示に応じて、前記デバイス間を接続する外部バスに係る回路構成を除く前記2つのデバイスの動作に係る回路構成のクロックの停止を制御するクロック制御回路とを有するLSI評価ボード装置により達成される。

(もっと読む)

半導体集積回路及び半導体集積回路の故障診断方法

【課題】CPUのパフォーマンスに影響を及ぼすことなく、故障診断を行うことを可能にする半導体集積回路を提供する。

【解決手段】通常動作において利用される第1のバスBUSA、及びそれとは異なる第2のバスBUSAに接続されたCPU1から第2のバスを介して出力される診断情報に基づいて、診断マクロ6が誤り検出情報を求め、プログラムの実行に応じて求められた最終の誤り検出情報と保持している1つの期待値との比較によりCPUが故障しているか否かを判定するようにして、通常動作に利用される第1のバスの負荷を増加させずに、故障診断を行えるようにする。

(もっと読む)

診断装置及び診断方法

【課題】交換モジュールの検査を低コストで実現すること。

【解決手段】本発明に係る診断装置1は、検査用プログラマブル論理回路21と、複数の検査モードの情報を格納する検査用記憶手段22と、を有する検査用ボード2と、制御用プログラマブル論理回路11と、複数の検査モードの情報を格納する制御用記憶手段14と、検査用ボード2が接続された場合に、検査用記憶手段22及び制御用記憶手段14に格納された複数の検査モードの情報に基づいて、検査用プログラマブル論理回路21及び制御用プログラマブル論理回路11を検査用の論理に置き換え、複数の検査モードを順次実行することで診断を行う診断プロセッサ15と、を有する交換モジュールと1、を備えるものである。

(もっと読む)

断線検出回路及び断線検出方法

【課題】外部の配線容量に影響されることなく、正確に断線診断を行えるようにする。

【解決手段】本発明に係る断線検出回路1は、S/HコンデンサC1と、フルチャージ部23と、ディスチャージ部22と、S/HコンデンサC1の電位をデジタル信号に変換するA/D変換部24と、A/D変換部24による変換結果を格納する記憶回路部25と、フルチャージ部23によりS/HコンデンサC1へのフルチャージを制御し、ディスチャージ部22によりS/HコンデンサC1のディスチャージを制御し、ディスチャージ前後のA/D変換結果を記憶回路部25に格納するA/D変換制御部28と、記憶回路部25に格納されたディスチャージ前後のA/D変換結果を比較する比較部26と、ディスチャージ前後の電位の差分を検知する差分判定部27と、差分が有ると判定された場合に、断線があると判定する制御部とを備える

(もっと読む)

半導体集積回路

【課題】 マイクロコンピュータ等の半導体集積回路がユーザモードで正常に動作することをプログラムメモリに試験用プログラムを格納せずに短時間で確認できるようにする。

【解決手段】 半導体集積回路(100)は、プログラムメモリ(114)と、中央処理ユニット(111)と、内部情報レジスタ(131a)とを備える。中央処理ユニット(111)は、ユーザモード時にはプログラムメモリ(114)に格納されたプログラムを実行し、テストモード時には外部装置から供給されるプログラムを実行する。内部情報レジスタ(131a)は、ユーザモードでの起動時にユーザモードでの起動の証拠となる内部情報を格納する。

(もっと読む)

1 - 20 / 151

[ Back to top ]