Fターム[2G132AB20]の内容

Fターム[2G132AB20]に分類される特許

1 - 20 / 107

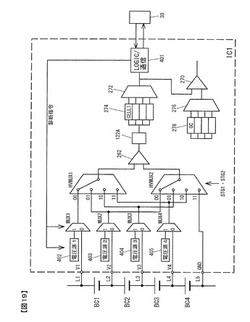

電池監視装置

【課題】信頼性の向上を図ることができる電池監視装置の提供。

【解決手段】電池監視装置は、直列接続された複数の電池セル(BC1〜BC4)の各セル電圧値を測定する電圧測定部を有する集積回路IC1と、複数の電池セルの正負両極と集積回路とを接続する複数の電圧計測ラインL1〜L5と、測定された各セル電圧値に基づいて電池セルの状態を監視する制御回路30と、を備え、集積回路は、互いに異なる擬似電圧を生成する擬似電圧生成部402〜405を有し、電圧測定部は、計測対象となる電池セルの正負両極に接続された一対の電圧計測ラインを選択する選択回路HVMUX1,HVMUX2と、選択回路により選択された一対の電圧計測ラインからの電圧を検出する検出回路262,122Aと、を有し、制御回路は、擬似電圧を選択回路に入力し、検出回路により検出された電圧値に基づいて選択回路による選択状態を診断する。

(もっと読む)

電子部品、測定方法および監視装置

【課題】接合部の損傷を事前に検知する。

【解決手段】電子部品は、第1部材と、第2部材と、接合部と、測定部とを備える。第1電極は、第1部材上に形成される。第2電極は、第1部材上の、第1電極が形成された領域の周囲の領域に形成される。第3電極は、第2部材に形成される。第2電極が第2部材に形成され、第3電極が第2部材の第2電極が形成された領域の周囲の領域に形成されてもよい。接合部は、第1電極と第2電極と第3電極と接合する。測定部は、第1電極および第2電極のうち少なくとも一方を含む接続経路の電気特性を測定する。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

電子機器の保守装置、方法、及びプログラム

【課題】電子機器の通常動作を妨げることなく、CPUの経時劣化を保障し、電子機器の性能を維持することができるようにする。

【解決手段】保守装置1は、CPU11に内蔵されるセンサ回路12からCPU11の劣化に応じて変化する劣化情報をCPU11の通常動作時に取得する劣化情報取得部2と、劣化情報に基づいてCPU11の劣化の進行度を示す劣化レベルを判定する劣化レベル判定部3と、劣化レベルの増大に伴いCPU11に印加される電源電圧を増加させるように電源13を制御する電源制御部4とを備える。

(もっと読む)

半導体集積回路及び誤動作防止方法

【課題】実システム動作中に電源状態を監視できる手段を提供する。

【解決手段】半導体集積回路は、発振器14と、電源電圧に応じて発振周波数が変化するリング発振器11と、発振器14の信号に基づいて、所定の判定期間を計測するインターバルタイマ13と、判定期間にリング発振器11が発振する発振周波数を測定する周波数測定用カウンタ12と、発振周波数の上限値と下限値とを保持する不揮発性メモリ15と、カウンタが測定した発振周波数が、不揮発性メモリ15が保持する上限電圧/下限電圧の判定コードの範囲内であるかを判定し、判定結果を出力する電圧判定回路16と、を備える。

(もっと読む)

モニタリング装置及びモニタリングシステム

【課題】LSI等の不具合発生時の原因追求を容易化する。

【解決手段】LSI内又はLSIの近傍にモニタリング装置100を配置し、モニタリング装置100内で、周波数カウンタ20が、一定時間でのリングオシレータ10の発振周波数を計測し、計測した発振周波数を示す発振周波数情報を生成し、時刻カウンタ30が、周波数カウンタ20により発振周波数が計測された時刻を示す時刻情報を生成し、出力制御部80が、発振周波数情報と時刻情報とを対応付けて記憶装置90に出力し、記憶装置90が、発振周波数情報と時刻情報をログとして記憶する。これにより、LSIが起動してから不具合発生までの間の発振周波数の推移を観測することで遅延の相対的な変化を確認することができ、LSIの個体差を気にする必要がなく、不具合発生時の原因追求を容易化できる。

(もっと読む)

信号監視回路及び半導体装置

【課題】半導体装置のサイズを小さくできる信号監視回路を提供する。

【解決手段】半導体装置の電源端子と接地端子との間に直列に設けられた、電流源と、所定信号の状態に応じてオンオフする第一スイッチと、所定信号が監視対象の信号に設定されるとオンする第二スイッチと、を備え、所定信号の状態を前記半導体装置の消費電流によって監視する構成とした信号監視回路。

(もっと読む)

トレースデータ取得装置、トレースデータ取得装置のトレースデータ取得方法およびデバッグシステム

【課題】LSIの実行を停止させることなく、被試験プログラムを分割せずに、必要なトレースデータを効率良く取得できるようにすることを目的とする。

【解決手段】トレースデータ入出力状況分析部140は、トレースデータバッファ120の空き容量102に基づいて、トレースデータ101の種類を優先度の高い順に選択する。トレースデータ取捨選択部110は、LSIのトレース信号発生源からトレースデータ101を入力し、入力したトレースデータ101が選択種類のトレースデータ101であるか否かを判定する。トレースデータ101が選択種類のトレースデータ101である場合、トレースデータ取捨選択部110はトレースデータ101をトレースデータバッファ120に記憶する。トレースデータ101が選択種類のトレースデータ101でない場合、トレースデータ取捨選択部110はトレースデータ101を破棄する。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、各前記回路ブロック毎に電源電圧を供給し、前記電源電圧を電圧調整回路により切り替える電圧供給回路を有し、前記電圧調整回路を切り替える電圧制御信号を記憶する電源電圧制御メモリを有する電圧設定回路を有し、前記半導体装置の回路の複数箇所に回路の電圧を検出する電圧検出スイッチを有し、前記電圧検出スイッチを指定することで電圧を検出する回路の位置を切り替え、且つ、前記電源電圧制御メモリにアドレスを指定して値を書き込む制御を行う回路スイッチ制御回路を有する半導体装置を用いる。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、前記回路ブロックがそれぞれ正常に動作し得る最小限度の電圧を供給する複数の電圧供給回路を備え、各前記回路ブロックへの最小限度の電圧を供給する制御内容を記憶する電源電圧制御メモリを有し、前記電源電圧制御メモリの記憶する制御内容に従って前記電圧供給回路が各前記回路ブロックに供給する電圧を切り替える電源切り替え手段を備えた半導体装置を用いる。

(もっと読む)

異常通知システムおよび半導体試験装置

【課題】異常検出回路が異常を検出したときに迅速且つ確実に異常処理を行うことを目的とする。

【解決手段】複数の下位モジュール4とこれらの下位モジュール4の制御を行う上位モジュール3との間をバス2により接続した異常通知システム1は、下位モジュール4から上位モジュール3に割込み信号を出力するシリアル伝送経路5と、下位モジュール4に備えられ、複数の異常検出回路20が異常を検出したことを示す異常情報に下位モジュール4を特定するモジュール特定情報を付加した複数ビットの出力情報をパラレルデータからシリアルデータに変換してシリアル伝送経路5に出力するパラレルシリアル変換部24と、上位モジュール3に備えられ、シリアル伝送経路5から入力した出力情報をシリアルデータからパラレルデータに変換して異常情報およびモジュール特定情報を得るシリアルパラレル変換部12と、を備える。

(もっと読む)

半導体集積回路装置

【課題】制御信号の系統を整理して、不定信号伝播防止回路等の検討漏れの危険性を回避し、さらに、自動化ツールへの搭載へ向けた検討を容易にし、また、チップ内部での電源遮断制御を容易化することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、各独立した電源領域AreaA〜AreaIごとに電源遮断の優先順を設け、優先順の高い回路がONしている場合にはそれより優先順の低い電源領域はOFFにできないという規則を設けて、設計方法の容易化を図る。また、各独立した電源領域AreaA〜AreaI内において、さらに別の電源を印加できる領域を設け、その領域に中継バッファ(リピータ)やクロックバッファ、情報退避用の情報保持ラッチを集積する。レイアウト上は、電源線の電流を分散させる目的でセルがロウ方向に並ぶ方向と垂直な方向にまとめてレイアウトすればよい。

(もっと読む)

モジュールおよび電子機器

【課題】カーケンダルボイドやエレクトロマグレーションよる例えば能動素子と回路パターンを接続する接合材の接合部に対応する破断を検出して能動素子の接合部を含む回路基板の故障を予兆することが可能なモジュールを提供する。

【解決手段】第1導体で形成された回路パターンを有する回路基板と、前記第1導体とは異なる第2導体で形成された接合材と、前記接合材により前記回路パターンに接合された受動素子および能動素子と、前記回路基板に信号回路と別に設けられた検出回路とを備え、前記検出回路は前記回路基板に設けられ、前記第1の導体と前記第2の導体とを電気的に接続した検出器と、前記検出器に電流を流す電源部と、前記検出器の一方の導体と前記電源の間に介在され、前記第1、第2の導体間の電気的特性を測定する計測部とを備えること特徴とするモジュール。

(もっと読む)

解析システム及び半導体装置

【課題】LSI等の半導体装置内部の信号の遷移を容易に確認することが可能な解析システム及び半導体装置を提供すること。

【解決手段】半導体装置の内部において、解析対象となる内部信号が入力され、内部信号の遷移を検出すると所定のコードに変換して出力するとともに、内部信号の遷移を報知する報知信号を出力する符号化回路と、半導体装置の内部において、符号化回路から出力されるコードを格納する内部メモリと、半導体装置の外部において、符号化回路から出力される報知信号が入力され、内部信号の遷移タイミングを計時する計時回路と、半導体装置の外部において、計時回路で計時された時間情報を格納する外部メモリと、を備える。

(もっと読む)

プログラマブル・ロジック・コントローラ、および、プログラマブル・ロジック・コントローラにおける故障診断方法

【課題】自己診断により入力回路部分の故障を検出することが可能なPLCを提供する。

【解決手段】制御処理回路40は、診断信号生成部43で生成した診断信号IT1〜ITを診断信号出力部44から出力し、AND回路30、信号入力部41を介して、故障判定部42へ取り込み、診断信号IT1〜IT4と信号入力部41から入力した入力信号DI1〜DI4とを、故障判定部42で比較し、一致しなかったとき、信号入力部41に故障ありと判定する。次に、制御処理回路40は、診断信号出力部44から出力した診断信号ET1,ET2を絶縁入力回路10のフォトカプラ12へ入力して、絶縁入力回路10のフォトカプラ11を動作させ、その出力信号d1〜d4を、信号入力部41を介して取得し、その入力信号DI1〜DI4を故障判定部42で期待値と比較し、一致しなかったとき、絶縁入力回路10に故障ありと判定する。

(もっと読む)

除電装置の監視装置、除電装置の監視方法及び除電装置の監視用プログラム

【課題】半導体ウエハWの電気的特性検査を行う際に、被処理体に帯電した静電気を除去する除電装置を監視して信頼性の高い電気的特性検査を行うことができる除電装置の監視装置を提供する。

【解決手段】本発明の除電装置の監視装置(監視回路)22は、メインチャック14とプローブカードが相対的に移動し、メインチャック14上の半導体ウエハWとプローブカード15を接触させて半導体ウエハWの電気的特性検査を行う際に、放電スイッチ回路21を用いてメインチャック14から半導体ウエハWに帯電した静電気を除去する除電装置20を監視する装置であって、除電装置20の放電スイッチ回路21Aと連動し且つ放電スイッチ回路21Aの誤動作を検出する検出スイッチ回路22Aと、検出スイッチ回路22Aを開閉する検出駆動回路22Bと、検出スイッチ回路22Aを介して放電スイッチ回路21Aの誤動作を判定する判定回路22Cと、を備えている。

(もっと読む)

半導体装置とその異常予測方法

【課題】動作異常を事前に予測し、故障箇所により異常動作時の動作を変更可能とする半導体装置と方法の提供。

【解決手段】第1のCPU101と、前記第1のCPUと同一又は同等の構成を有する第2のCPU102と、前記第1のCPUの出力と前記第2のCPUの出力を比較する比較器103と、を備え、前記第2のCPUは、前記第1のCPUよりも動作マージンが低くなるように作りこまれており、前記第1のCPUと前記第2のCPUへ同一の信号を入力し、第1のCPU101と第2のCPU102の出力の比較結果の不一致を検出することで、異常の予測が行われる。比較器での比較結果がエラーを示すとき、装置をリセットするリセット制御回路104を備えている。

(もっと読む)

半導体製品ダイのテスト方法及び同テストのためのテストダイを含むアセンブリ

【課題】製品ダイ(2011,300)の製品回路(202,302,304)をテストするためのテストアセンブリ(2000)を提供すること。

【解決手段】一実施形態では、テストアセンブリは、テストダイ(2010,400)及び該テストダイをホストコントローラ(2002)へ電気的に結合する相互接続基板(2008)を含む。該テストダイは、テスト回路(202A,402,404)及び製品回路を統合化された設計(102)に同時に設計するステップを含むテストダイ及び製品ダイに関する設計方法論(100)に従って設計可能である。テスト回路は、該テスト回路により必要とされるシリコン領域の量にほぼ関係なく、対応する製品回路に関して高度の欠陥検出範囲を提供するよう設計可能である。次いで該設計方法論は、統合化された設計をテストダイ及び製品ダイへと分割する(104)。テストダイはテスト回路を含み、製品ダイは製品回路を含む。

(もっと読む)

電圧監視回路および該電圧監視回路を内蔵した半導体装置

【課題】半導体装置に集積した場合に、電圧監視回路のスペースを極めて小さくすることができ、コスト上昇を抑えることが可能な電圧監視技術の提供。

【解決手段】個別電源回路11〜14毎に、該個別電源回路11〜14の出力電圧Vo1〜Vo4を監視し、異常を検出した場合に異常信号を出力する個別電圧監視回路21〜24を備える。各個別電圧監視回路21〜24は、前段の個別電圧監視回路の出力信号(OUTi)が異常信号の場合は、自身も異常信号を出力する(OUTi+1)とともに、前段の個別電圧監視回路の出力信号が正常信号の場合は、自身の監視結果を出力する構成を有し、複数の個別電源回路11〜14のいずれかに出力電圧(OUT1〜4)に出力電圧異常が発生した場合に、異常信号を出力Doutとして出力する。個別電圧監視回路21〜24を半導体装置の小さい領域にまとめてレイアウトすると省スペース化が可能になる。

(もっと読む)

検出データ処理装置及びプログラム

【課題】回路基板における異常又は故障を高精度に検出することを支援する。

【解決手段】故障診断装置10の解析データ抽出部104は、回路基板の動作状態を検出する動作状態検出部1から取得された検出データの複数のグループについて互いに相関関係を求め、他のグループとの相関関係を表す値が予め設定された閾値よりも小さいグループの検出データを解析データとして選択し抽出する。第一マハラノビス距離算出部106は、正常な回路基板を動作させたときの検出データから解析データ抽出部104が抽出した解析データを用いて生成された第一のマハラノビス空間と、診断対象の回路基板を動作させたときの検出データと、に基づいて1段目のマハラノビス距離を算出する。

(もっと読む)

1 - 20 / 107

[ Back to top ]