Fターム[2G132AE22]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 制御回路 (1,346)

Fターム[2G132AE22]の下位に属するFターム

プログラムによる制御 (494)

複数試験装置の一括制御(ホストシステム) (60)

Fターム[2G132AE22]に分類される特許

1 - 20 / 792

インターフェースボード

基板検査装置および基板検査方法

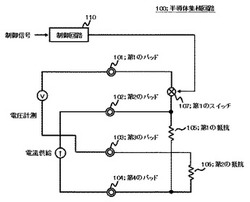

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体装置の検査装置及び検査方法

【課題】半導体装置からのエミッションの検出を加熱しながら行う半導体装置の検査装置を提供する。

【解決手段】検査装置1は、半導体チップ2を載置する観察ステージ16を、半導体チップ2の基板材料と同じSiで製造し、半導体チップ2の裏面側に撮像素子35を配置した。半導体チップ2で発生した微弱な光は、半導体チップ2、観察ステージ16を透過して撮像素子35に入射する。観察ステージ16は、Siから製造されているので、ヒータ25によって簡単に加熱できる。また、観察ステージ16の上方には、プローブカード19及びLSIテスタ20が配置されており、半導体チップ2の回路のテストが可能である。

(もっと読む)

電子部品、測定方法および監視装置

【課題】接合部の損傷を事前に検知する。

【解決手段】電子部品は、第1部材と、第2部材と、接合部と、測定部とを備える。第1電極は、第1部材上に形成される。第2電極は、第1部材上の、第1電極が形成された領域の周囲の領域に形成される。第3電極は、第2部材に形成される。第2電極が第2部材に形成され、第3電極が第2部材の第2電極が形成された領域の周囲の領域に形成されてもよい。接合部は、第1電極と第2電極と第3電極と接合する。測定部は、第1電極および第2電極のうち少なくとも一方を含む接続経路の電気特性を測定する。

(もっと読む)

半導体装置の故障位置解析方法及び装置

【課題】SiC半導体装置における故障位置をOBIRCH法により解析して特定できるようにした半導体装置の故障位置解析方法及び装置を提供する。

【解決手段】半導体装置の基板の裏面側から、該基板の表面側のデバイス及び回路に、レーザー光を走査しながら照射して加熱すると共に、前記デバイス及び回路に電流を流し、電流の変化によって抵抗値変化を検出して、故障位置を解析する半導体装置の故障位置解析方法において、前記半導体装置が、NドープSiC基板を用いた半導体装置であり、前記レーザー光として、波長650〜810nmのレーザー光を用いる。

(もっと読む)

再構築したメモリ空間の回収方法

【課題】廃棄されたダイから使用可能なメモリ空間を回収するメモリ容量を有するメモリを回収する方法を提供する。

【解決手段】再構築したメモリ空間の回収方法は、廃棄されたダイを回収し、使用可能なメモリ空間に応用し、規格化又は非規格化のメモリ容量を有するメモリを形成する。再構築したメモリ空間の回収方法は、ブロックエリア、ページエリア及びセルエリアを有するダイを準備するステップと、ダイのブロックエリア、ページエリア及びセルエリアのうちの1つを走査し、ダイに対応したエリア中にテストデータを書き入れ、ダイによりテストデータの読み書き及び比較を行ってテスト結果を得て、このテスト結果に基づき、正常及び異常なブロックエリア、ページエリア又はセルエリアを標記するステップとを含む。

(もっと読む)

検査装置及び検査システム

【課題】汎用性を有し、高速で動作する半導体装置を検査できる検査装置を提供する。

【解決手段】検査装置は、第1貫通電極24bと、テスト信号を生成する信号生成ユニット30とを有する第1半導体基板24と、複数の接触子60を有するプローブ基板27と、第2貫通電極25bと、複数の接触子60と信号生成ユニット30との間の信号経路をプログラム可能に設定するスイッチマトリックス20eとを有する第2半導体基板と、を備え、第1半導体基板24と第2半導体基板25とは積層されており、第1貫通電極24bは、信号生成ユニット30が生成したテスト信号をスイッチマトリックス20eに伝達し、第2貫通電極25bは、スイッチマトリックス20eによって経路設定されたテスト信号を所定の接触子60に伝達し、信号生成ユニット30から、着脱自在に接続される電気的接続部を介さずに、接触子60にテスト信号が伝達される。

(もっと読む)

試験装置

【課題】電源電圧変動を制御可能な試験装置を提供する。

【解決手段】試験装置2は、被試験デバイス(DUT)1を試験する。メイン電源10は、DUT1の電源端子P1に供給すべき電力信号VDDを生成する。メイン電源10の出力端子P4とDUT1の電源端子P1の間の電源ライン上には、可変電源経路部30が設けられる。可変電源経路部30は、その電気的特性が可変に構成される。制御部32は、可変電源経路部30の電気的特性を制御する。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

評価システム

【課題】製品ボードに搭載される製品FPGAの端子数に制限されず、内部信号の観測を可能とし、製品FPGAを製品ボードに搭載された実使用状態で論理検証することが可能な評価システムを提供することを課題とする。

【解決手段】評価システム1は、製品ボード2、評価ボード3、およびそれらを接続するシリアル・インターフェース5を備える。製品ボード2に搭載される製品FPGA6はコアロジック60に入力される外部入力信号を分岐する分岐回路61を備える。評価ボード3は観測FPGA8を備える。観測FPGA8はコアロジック60と論理的に等価な観測コアロジック81および観測コアロジック81の内部信号を取得する内部信号取得回路82を備える。コアロジック60の実動作に供される外部入力信号が評価ボード3に送られ観測コアロジック81がコアロジック60の実動作と等価に動作する。その時の内部信号を取り出し論理検証を行う。

(もっと読む)

移動体通信装置試験システムおよび試験方法

【課題】試験対象に対してシーケンス測定を実行する際に、取得データ量の面で、誤った測定の無駄な測定をしないで済むようにする。

【解決手段】シーケンス測定制御手段35が実行指定された測定シーケンスにしたがう制御を開始する前に、実行指定された測定シーケンスで送受信部21が解析対象として取得する予定のデータ量の合計値を算出するデータ量算出手段40と、算出したデータ量の合計値が受信データメモリ23の所定容量に応じて予め設定した許容値を超えるか否かを判定するデータ量判定手段41とを備え、シーケンス測定制御手段35は、データ量判定手段41により算出したデータ量の合計値が許容値を超えると判定されたとき、その判定結果を表示部61に表示して、ユーザーに通知する。

(もっと読む)

信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

(もっと読む)

半導体集積回路検査装置,および,半導体集積回路の検査方法

【課題】テスト時間をより短縮するテストパターンを作成する半導体集積回路検査装置,および,半導体集積回路の検査方法を提供する。

【解決手段】半導体集積回路検査装置20は,テストパターンを複数の区間に分割した分割テストパターン毎に,分割テストパターンに対する論理演算を異なる周期のクロック信号に基づき半導体集積回路に実行させることにより得られた半導体集積回路31の故障判定結果に基づき,分割テストパターン毎の最適クロック周期を算出する最適周期算出部213と,テストパターンと,テストパターンに係る分割テストパターン毎の最適クロック周期を有するテストパターンファイルを生成する新テストパターンファイル生成部214を有する。

(もっと読む)

半導体集積回路装置の試験方法及び半導体集積回路装置

【課題】 半導体集積回路装置の試験方法及び半導体集積回路装置に関し、所定の回路動作を行った状態のまま半導体集積回路装置側の操作で所望の温度に制御する。

【解決手段】 スクリーニング試験前の工程にて測定された半導体集積回路装置の回路毎の電源電流値或いは電流ランクのいずれかにより、前記半導体集積回路装置全体毎または個別の回路動作毎に、適切な周波数に周波数設定し、所望の発熱量になるよう発熱量の制御を行い、スクリーニング試験時に、所定の回路動作を行った状態のまま所望の温度に制御する。

(もっと読む)

半導体試験装置、電気長測定方法

【課題】測定経路端を接地して電気長を測定する場合に、経路に断線があっても測定結果を得られるようにする。

【解決手段】測定経路端を接地して電気長を測定する半導体試験装置であって、測定経路に測定信号を出力する信号発生手段と、測定経路から分岐して入力される入力信号と、任意の閾値電圧とを比較する比較手段と、信号発生手段に測定信号を出力させ、比較手段の入力信号が第1閾値電圧以上となってから第2閾値電圧以下となるまでの時間を計測し、所定時間内に計測された場合には、計測された時間に基づいて測定経路の電気長を算出し、所定時間内に計測されなかった場合には、比較手段の入力信号が第1閾値電圧以上となってから、第1閾値電圧よりも高い第3閾値電圧以上となるまでの時間を計測して、測定経路の異常箇所までの電気長を算出する電気長測定制御手段とを備える。

(もっと読む)

半導体試験装置における電気長測定方法

【課題】ウェハを対象とした半導体試験装置において、簡易にプローブ先端を接地状態として電気長測定を行なえるようにする。

【解決手段】試験対象のウェハと接触するプローブを複数備えた半導体試験装置における、プローブを一端とする信号経路の電気長測定方法であって、電気伝導性領域を有するキャリブレーションウェハの電気伝導性領域を全プローブに接触させ、信号経路の他端から測定信号を入力し、電気伝導性領域との接触部で反射した信号波形を他端側で測定することにより電気長を算出する。

(もっと読む)

試験装置および試験方法

【課題】正確なタイミングでサンプリングしたデータ値を期待値と比較する。

【解決手段】データ信号とデータ信号をサンプルするタイミングを示すクロック信号とを出力する被試験デバイスを試験する試験装置であって、データ信号をバッファリングするバッファ部と、当該試験装置の試験周期毎に、制御信号およびデータ信号の期待値を発生するパターン発生部と、試験周期毎に、制御信号がバッファ部からのデータの読出しを指示することを条件として、バッファ部からデータ信号を読み出す読出制御部と、読出制御部により読み出されたデータ信号とパターン発生部から発生された期待値とを比較する判定部とを備える試験装置を提供する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】精度の高いディレイテストを行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路1は、クロック信号CLKに同期して動作する複数のレジスタを有する内部回路11と、クロック信号CLKに同期して動作し第1ノードから第2ノードまでの信号伝搬時間を測定する遅延測定回路12と、遅延測定モードの場合に、遅延測定回路12に対してのみクロック信号CLKを供給し、電圧検出モードの場合に、内部回路11及び遅延測定回路12に対してクロック信号CLKを供給するクロック供給回路13と、を備える。

(もっと読む)

半導体試験装置、半導体試験方法及びプログラム

【課題】ウェハに含まれる半導体集積回路の電気的特性の測定には、測定対象となる全ての半導体集積回路が専用の測定回路を備えている必要があるが、全ての半導体集積回路に対して専用の測定回路を配設すると、半導体集積回路の面積が増加してしまう問題がある。そのため、半導体集積回路の面積を増加させることなく、半導体集積回路の電気的特性の測定を可能とする半導体試験装置が望まれる。

【解決手段】半導体試験装置は、第1の半導体集積回路と、電気的特性を測定するための測定回路及び測定端子と、前記測定回路に近接する第2の半導体集積回路と、を含むウェハの特性の測定を行う測定部と、第2の半導体集積回路に対して実施するウェハテストから得られる第1の電気的特性と、測定端子から測定した第2の半導体集積回路についての第2の電気的特性と、の相関に基づいて第1の半導体集積回路について第2の電気的特性を推定する制御部と、を備えている。

(もっと読む)

1 - 20 / 792

[ Back to top ]