Fターム[2G132AF00]の内容

電子回路の試験 (32,879) | テストヘッド (2,056)

Fターム[2G132AF00]の下位に属するFターム

プローブ (1,700)

ピンエレクトロニクス(プローブ切替等) (206)

プローブの加熱、冷却をするもの (55)

Fターム[2G132AF00]に分類される特許

1 - 20 / 95

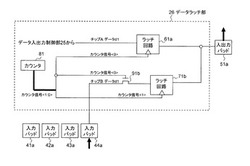

半導体装置およびその検査方法

【課題】ウエハ検査時に必要なプローブピンを削減可能にした半導体装置を提供する。

【解決手段】第1のデータを記憶する記憶素子と、データ読み出しの指示が入力されると、記憶素子から第1のデータを読み出して出力するデータ入出力制御部と、データ入出力制御部から出力される第1のデータを第1の端子に出力し、第1のデータを第1の端子に出力するとき、自装置の第2の端子と他の半導体装置の第1の端子とを接続するプローブカードを介して他の半導体装置から受信する第2のデータを保持し、その後、第2のデータを自装置の第1の端子に出力するデータラッチ部とを有する。

(もっと読む)

半導体集積回路のテストボード

【課題】半導体集積回路のテスト時に発生する電源ノイズは、多種多様である。そのため、テスト時に生じる多様な電源ノイズを低減させる半導体集積回路のテストボードが、望まれる。

【解決手段】半導体集積回路のテストボードは、被検査デバイスに供給する電流値を被検査デバイスに供給されるクロックに同期させて変化させる電源電流制御回路を備えている。電源電流制御回路は、被検査デバイスに供給されるクロックに同期させて、被検査デバイスに供給される電流値を変化させる。

(もっと読む)

半導体試験装置、電気長測定方法

【課題】測定経路端を接地して電気長を測定する場合に、経路に断線があっても測定結果を得られるようにする。

【解決手段】測定経路端を接地して電気長を測定する半導体試験装置であって、測定経路に測定信号を出力する信号発生手段と、測定経路から分岐して入力される入力信号と、任意の閾値電圧とを比較する比較手段と、信号発生手段に測定信号を出力させ、比較手段の入力信号が第1閾値電圧以上となってから第2閾値電圧以下となるまでの時間を計測し、所定時間内に計測された場合には、計測された時間に基づいて測定経路の電気長を算出し、所定時間内に計測されなかった場合には、比較手段の入力信号が第1閾値電圧以上となってから、第1閾値電圧よりも高い第3閾値電圧以上となるまでの時間を計測して、測定経路の異常箇所までの電気長を算出する電気長測定制御手段とを備える。

(もっと読む)

半導体試験装置における電気長測定方法

【課題】ウェハを対象とした半導体試験装置において、簡易にプローブ先端を接地状態として電気長測定を行なえるようにする。

【解決手段】試験対象のウェハと接触するプローブを複数備えた半導体試験装置における、プローブを一端とする信号経路の電気長測定方法であって、電気伝導性領域を有するキャリブレーションウェハの電気伝導性領域を全プローブに接触させ、信号経路の他端から測定信号を入力し、電気伝導性領域との接触部で反射した信号波形を他端側で測定することにより電気長を算出する。

(もっと読む)

半導体テスト信号伝送ケーブル

【課題】半導体テスト装置のテストヘッドカードに対する追加回路を容易に実装できるようにする。

【解決手段】テストヘッドカードとDUTボードとの間で半導体テストに関する信号を伝送する半導体テスト信号伝送ケーブルであって、テストヘッドカード側と接続する第1ケーブル部と、DUTボード側と接続する第2ケーブル部と、第1ケーブルと第2ケーブルとの間に取り付けられた電子回路収容部材とを備えた半導体テスト信号伝送ケーブル。第2ケーブル部のDUTボード側端には、スプリングピンを備えることができる。

(もっと読む)

半導体集積回路装置のテスト方法およびテストボード

【課題】半導体集積回路装置の入力端子数よりも少ない端子数のテスタを用いて半導体集積回路装置のテストを行うテスト方法を提供すること。

【解決手段】半導体集積回路装置のテスト方法は、半導体集積回路装置の複数の入力端子とテスタからのテスト信号を受信するテスタ端子とを、多対1に電気的に接続するテストボードを介して、該テスタから該半導体集積回路装置に所定のテストパタン信号を送信する工程と、前記半導体集積回路装置の出力端子から出力された出力信号と、前記所定のテストパタン信号に対応する期待値とを比較して、前記半導体集積回路装置の良否を判定する工程と、を含む。

(もっと読む)

電子部品試験装置、ソケットボード組立体、及びインタフェース装置

【課題】被試験電子部品の品種切替時における作業性の向上を図ることが可能な電子部品試験装置を提供する。

【解決手段】電子部品試験装置1は、DUT90が電気的に接続されるDSA10と、DSA10が着脱可能に装着されるハイフィックス30と、ハイフィックス30が着脱可能に装着されるテストヘッド60と、を備えており、ハイフィックス30は、DSA10に係合するフック431を有し、DSA10は、フック431が係合するフック受け部222と、ハイフィックス30に向かって進退可能なプッシュピン24と、を有し、フック431には、プッシュピン24が当接するピン受け部433が形成されており、プッシュピン24がピン受け部433を押圧することで、フック431の係合が解除される。

(もっと読む)

半導体試験装置および半導体試験装置のユニット接続方法

【課題】各ユニットを接続するシーケンスを再開するときに、メモリに記憶された情報を使用することなく、シーケンスを再開できる半導体試験装置を提供する。

【解決手段】テストヘッドとベースユニットとの間およびベースユニットとプローブカードとの間を接続して構成する半導体試験装置であって、テストヘッドとベースユニットとの間を接続してロックする第1のロック機構10のロック状態を検出するアンロック側センサ20およびロック側センサ21と、ベースユニットとプローブカードとの間を接続してロックする第2のロック機構40のロック状態を検出するアンロック側センサ30およびロック側センサ31と、それぞれのロック状態に基づいて、第1のロック機構10と第2のロック機構40とのシーケンスの制御を行うシーケンス制御部32と、を備えている。

(もっと読む)

水冷式半導体試験装置の冷却水タンク

【課題】水冷式半導体試験装置の冷却水を貯蔵する冷却水タンクにおいて、配管内の結露を起因とする水位上限オーバーフロー誤検出を防止する。

【解決手段】側面に水位上限を定める開口部が設けられた冷却水タンク本体と、開口部によりタンク本体内部と連結したサブタンクと、水位上限を超えた冷却水を、サブタンクを経由して外部に排出する排出用配管とを備え、サブタンクは、開口部より高い位置において外気開放され、底面が開口部より低い位置にある水冷式半導体試験装置の冷却水タンク。

(もっと読む)

パフォーマンスボードの落下防止機構を備えたテストヘッド

【課題】既存のパフォーマンスボードに対しても効果が得られる落下防止機構を備えたテストヘッドを提供する。

【解決手段】補強枠を備えたパフォーマンスボードを装着するテストヘッドであって、パフォーマンスボード装着面側の、パフォーマンスボードの補強枠の対向する辺の対角位置付近に対応して配置され、補強枠を保持するロック状態/補強枠を保持しないアンロック状態を手動で切り替える2つのパフォーマンスボード落下防止機構を備えたテストヘッド。パフォーマンスボードの補強枠の対向する辺は、パフォーマンスボードの長手方向に対応する辺とすることができる。

(もっと読む)

着脱装置、テストヘッド、半導体試験装置及び着脱方法

【課題】基板をテストヘッドから取り外す際にコネクタが破損することを防止することのできる着脱装置を提供する。

【解決手段】基板3をテストヘッド11に対して着脱するための着脱装置は、基板3に設けられた凹部33と、テストヘッドに設けられた凸型部材23とを備えた嵌合機構を備え、また、凸型部材23を基板3に対して垂直方向に移動させる駆動機構24を備える。第1コネクタ32と第2コネクタ22とが嵌合した状態から、第1コネクタ32と第2コネクタ22との嵌合が解除される際には、凹部33に凸型部材23が挿入され、凸型部材23の側面から嵌合部材235が突出して凹部33の窪み部331に嵌合した状態で、駆動機構24が、基板3がテストヘッド11から離れる方向に、凸型部材23を移動させ、もって第1コネクタ32と第2コネクタ22との嵌合が解除される。

(もっと読む)

集積回路およびウェーハを試験する無線周波数技術構造および方法

【課題】集積回路を有するウェーハの無線試験を行うためのウェーハ上に形成された試験回路を含む装置および方法を提供する。

【解決手段】ウェーハ16の外部にある試験ユニット12、および集積回路を含むウェーハ上に製造された少なくとも1つの試験回路14を含む。試験ユニット12は、RF信号を送信し、試験回路14に電力を供給する。試験回路14は、可変リング発振器を含み、集積回路の公称動作周波数での一連のパラメータ試験を実行し、試験結果を分析のために試験ユニット12に送信する。

(もっと読む)

自動テスト機器用高速故障捕捉装置および方法

【課題】 故障処理回路において、テスト対象メモリ(MUT)から故障ロケーション情報を識別するために使用される故障捕捉回路が開示される。

【解決手段】 故障捕捉回路は、複数のチャネルを備え、MUTに接続するように適合される故障検出回路を含む。故障検出回路は、テスト信号をMUTに与え、そこからの出力信号を処理して故障情報にするように動作する。テスト時間を最小化するために、故障メモリ回路および高速リンクが設けられる。高速リンクは、故障メモリ回路を故障検出回路に接続し、シリアルデータ転送能力をその間に提供する。

(もっと読む)

試験装置及び試験方法

【課題】光インターフェースを備える被試験デバイスを試験する。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスを試験する試験信号を発生する試験信号発生部と、試験信号を光試験信号に変換する電光変換部と、電光変換部が変換した光試験信号を被試験デバイスの光入力部に伝送すると共に、被試験デバイスが出力する光応答信号を受け取って出力する光インターフェース部と、光インターフェース部が出力する光応答信号を電気信号の応答信号に変換して送信する光電変換部と、光電変換部が送信する応答信号を受信する信号受信部と、を備える試験装置および試験方法を提供する。

(もっと読む)

試験装置および接続装置

【課題】付加回路を用いて既存の試験装置を低コストで高速および高機能化する。

【解決手段】被試験デバイスの種類に応じたソケットボードに接続されて、被試験デバイスを試験する試験装置であって、被試験デバイスを試験する試験モジュールを内部に有するテストヘッドと、テストヘッド内の試験モジュールにケーブルを介して接続されると共に、ソケットボードに接続される機能ボードと、機能ボードに搭載され、試験モジュールおよび被試験デバイスに接続される付加回路と、を備える試験装置を提供する。

(もっと読む)

半導体装置の試験方法

【課題】半田接続することなく波形測定が可能な半導体装置の試験方法を提供する。

【解決手段】半導体装置Wと接続されたコンタクトリング40の接点41と、パフォーマンスボード31の端子とが対向接続した状態で半導体装置の試験を行う半導体試験装置を用いた半導体装置の試験方法であって、

前記コンタクトリングよりも外側にはみ出した外側領域92と、前記コンタクトリングの前記接点と対向する第1の端子93及び前記パフォーマンスボードの前記端子と対向する第2の端子94を各々両面に有し、前記第1の端子及び前記第2の端子に接続された測定用端子96を前記外側領域内に有する測定用基板90を用意する工程と、

該測定用基板を、前記コンタクトリングと前記パフォーマンスボードとの間に挟んで配置し、前記測定用端子を用いて前記半導体装置の測定試験を行う工程と、を含む。

(もっと読む)

コンタクタ、半導体装置の試験装置、及び半導体装置の製造方法

【課題】コンタクタ、半導体装置の試験装置、及び半導体装置の製造方法において、試験の信頼性を高めること。

【解決手段】第1の材料を含むコンタクタ母材1と、コンタクタ母材1の先端部1aのうち、半導体装置30の電極31との接触面1bにのみ選択的に形成された、第2の材料を含む導体膜10aとを有するコンタクタ9による。

(もっと読む)

半導体試験装置

【課題】テストヘッド側保持構造を改良して、トッププレートの移動機能を保持したまま、プローブカード反り防止機能が向上された半導体試験装置を実現する。

【解決手段】プローバに接するトッププレ−トと、このトッププレ−トをフローティング支持するテストヘッド本体とを具備する半導体試験装置において、前記トッププレ−トと前記テストヘッド本体との間に設けられ前記プローバとトッププレ−トとの結合動作後に前記トッププレ−トと前記テストヘッド本体とを固定する固定手段を具備したことを特徴とする半導体試験装置である。

(もっと読む)

端子、同軸ケーブルモジュール、及びインタフェース装置

【課題】電子部品試験装置のインタフェース装置の製造期間の短縮化を図ることが可能な端子を提供する。

【解決手段】端子60Aは、同軸ケーブル50の信号線51を突出させつつ同軸ケーブル50のシールド層53がそれぞれ固定される複数の固定部62が並列に設けられた本体部61と、同軸ケーブル50の信号線51と実質的に同一方向に本体部61から突出しており、ソケットボード30のスルーホールに挿入される複数の突出部63と、を備えている。

(もっと読む)

任意波形発生器

【課題】本発明の目的は、DUTに至るまでの伝送路により生じる任意波形信号の損失を、わずかなコストで容易に低減することのできる、任意波形発生器を実現することである。

【解決手段】本発明は、任意波形信号を発生させる波形発生部と、この波形発生部の出力端に接続された出力抵抗とを備え、被試験対象デバイスに任意波形信号を出力する任意波形発生器において、前記被試験対象デバイスに至る伝送経路で生じる、周波数に応じた任意波形信号の振幅損失を補正する補正回路を備えることを特徴とする。

(もっと読む)

1 - 20 / 95

[ Back to top ]