Fターム[2G132AL00]の内容

電子回路の試験 (32,879) | 目的、その他 (6,788)

Fターム[2G132AL00]の下位に属するFターム

被試験体の識別、存在の検知 (22)

接続の確実化 (517)

接続の確認、誤接続の検出 (109)

接続線の本数の減少(端子数の減少) (295)

多品種への対応(汎用性のあるもの) (130)

試験時間の短縮 (1,339)

試験精度の向上 (1,554)

不良箇所、原因の特定等 (520)

試験装置の調整 (288)

インピーダンスマッチ (76)

温度調整 (87)

レベル変換 (8)

複数の被試験体の試験 (254)

母線(バス等)に接続した状態での試験 (19)

異常時の処理、保護 (119)

低機能装置で高機能素子を試験 (203)

試験装置の構成要素の配置改善 (287)

試験装置の動作試験 (78)

試験方法としては一般的なもの (13)

Fターム[2G132AL00]に分類される特許

1 - 20 / 870

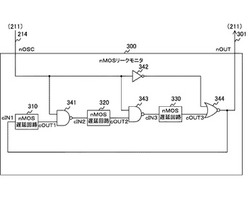

発振回路およびテスト回路

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

電圧出力装置および抵抗測定装置

【課題】半導体スイッチを介して測定対象体に対する測定用電圧の出力をオン・オフする構成において、スパイク電圧を大幅に低減する。

【解決手段】規定電圧値V1の測定用電圧Vmを測定対象体21に出力する電圧出力装置1であって、測定用電圧Vmを出力すると共に測定用電圧Vmの電圧値を制御可能な電源部2と、電源部2から出力される測定用電圧Vmの測定対象体21に対する出力をオン・オフする半導体スイッチ3aと、電源部2および半導体スイッチ3aを制御する処理部5とを備え、処理部5は、半導体スイッチ3aをオフ状態に制御した状態において電源部2に対する制御を実行して測定用電圧Vmの電圧値を段階的に複数回に亘って変化させて規定電圧値V1に設定する電圧設定処理、および半導体スイッチ3aをオン状態に制御して規定電圧値V1に設定された測定用電圧Vmを測定対象体21に出力する電圧出力処理を実行する。

(もっと読む)

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

半導体装置

【課題】複数箇所のタイミング違反検出を、小規模な回路構成で実現する。

【解決手段】選択信号に基づいて、複数の信号からいずれか1つを選択する第1のセレクタと、上記選択信号に基づいて、ラッチされた複数の信号からいずれか1つを選択する第2のセレクタと、クロック信号CLKを所定時間遅延する遅延回路と、遅延回路により遅延したクロック信号に同期して、第1のセレクタの出力をラッチするタイミング違反検出用フリップフロップ回路と、タイミング違反検出用フリップフロップ回路の出力と第2のセレクタの出力とを比較する比較回路とを、備える。複数の信号に対し、個別に回路を設けることなく、1つのタイミング違反検出回路で構成することができる。

(もっと読む)

検査装置及び検査システム

【課題】汎用性を有し、高速で動作する半導体装置を検査できる検査装置を提供する。

【解決手段】検査装置は、第1貫通電極24bと、テスト信号を生成する信号生成ユニット30とを有する第1半導体基板24と、複数の接触子60を有するプローブ基板27と、第2貫通電極25bと、複数の接触子60と信号生成ユニット30との間の信号経路をプログラム可能に設定するスイッチマトリックス20eとを有する第2半導体基板と、を備え、第1半導体基板24と第2半導体基板25とは積層されており、第1貫通電極24bは、信号生成ユニット30が生成したテスト信号をスイッチマトリックス20eに伝達し、第2貫通電極25bは、スイッチマトリックス20eによって経路設定されたテスト信号を所定の接触子60に伝達し、信号生成ユニット30から、着脱自在に接続される電気的接続部を介さずに、接触子60にテスト信号が伝達される。

(もっと読む)

電源装置およびそれを用いた試験システム

【課題】電源電圧の変動を抑制する。

【解決手段】メイン電源は、DUT1の電源端子P1の電位を所定の目標値に近づくように帰還制御する。制御端子PCNTには、補償電源が生成すべき補償電流の目標波形REFを指示する電流制御信号SCNTが入力される。電流検出回路22は、インダクタL1に流れる電流ILに応じた検出信号VCSを生成する。パルス変調器24は、検出信号VCSを電流制御信号SCNTに応じた目標波形REFと比較し、比較結果に応じてレベルが変化するパルス信号Spを生成する。ドライバ26は、パルス信号Spにもとづいて、第1スイッチSW1および第2スイッチSW2を相補的にスイッチングする。

(もっと読む)

電源瞬断試験装置

【課題】電源電圧の瞬断、瞬オンに対する自動車用電子機器の動作限界を定量的に調査する手段を提供する。

【解決手段】被試験機に印加する通常の電源電圧である+Bおよび被試験機のメモリーホールドなどのための常時印加の電圧であるAccの瞬断について、様々なパターンを再現するために当該時間、電圧についてもプログラムを用いて少しつづ徐々に変化させて被試験機に印加し、これに基づく被試験機の応答を監視して別に定めた短い時間ごとに出力論理の正否を確認することにより、自動車用に最近多く用いられるデジタル機器独特のプログラムによる思いも寄らない誤動作の発生を確認でき、さらに誤動作発生時の誤動作モードをきちんと捕らえて適切な設計対応を取ることができる。

(もっと読む)

高周波モジュールおよび高周波モジュールの検査方法

【課題】高周波回路チップ上の回路と、モジュールを構成する配線基板上の回路についてその相対位置を検出することによって、容易に実装状態が測定できる高周波モジュールおよび高周波モジュールの測定方法を提供する。

【解決手段】入出力端子6を備えた高周波回路チップ1と、高周波回路チップ1の入出力端子6を、バンプ5を介してフリップチップ接続する接続用パッド7を含む配線部を備えた配線基板2とを備えた高周波モジュールであって、入出力端子の2端子間に接続された、スパイラルインダクタ3sと、スパイラルインダクタ3sに対向する位置に配設され、接地電位に接続された検出用導体4dとを備え、接続用パッド間のインダクタンスを測定することによって、スパイラルインダクタ3sと検出用導体4dとの距離の変化に起因する入出力端子6と接続用パッド7間の距離の変化を測定可能に構成される。

(もっと読む)

集積回路,集積回路の試験装置および集積回路の試験方法

【課題】集積回路上の冗長メモリの試験に際し、冗長メモリにおける不良発生位置を取得する。

【解決手段】スペアのメモリセルをもつ冗長メモリ30と、冗長メモリ30に与えるテストパターンと当該テストパターンを冗長メモリ30に与えた際に冗長メモリ30から出力されるべきデータの期待値とを生成する生成部41と、生成部41によって生成された期待値と、第1生成部41によって生成されたテストパターンを冗長メモリ30に与えた際に冗長メモリ30から出力されるデータとを比較する比較部42と、比較部42の比較結果を記憶する記憶部10と、比較部42の比較結果が不一致である場合、当該比較結果を、当該比較結果を得た冗長メモリ30の位置情報に対応付けて記憶部10に書き込む一方、比較部42の比較結果が一致である場合、当該比較結果の記憶部10への書込を抑止する書込制御部50Aと、を有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

クロック周波数検出装置

【課題】電子装置において、動作クロックの周波数の異常を、動作クロックを選択的に通過させるフィルタ回路を用いることなく、高精度に検出できるようにする。

【解決手段】PLL回路10にて生成された動作クロックを受けて動作する制御装置2において、動作クロックの周波数の異常判定を行う際には、動作モード切換部32が、半導体メモリ12への書込用電圧を生成するF/V変換回路20のF/V変換特性を、動作クロックの周波数変動に対し出力電圧が略一定となる第1特性から、動作クロックの周波数に対応して出力電圧が変化する第2特性に切り換え、電圧検出部34が、その出力電圧を検出し、周波数異常判定部36が、その検出された電圧値に基づき動作クロックの周波数異常を判定する。

(もっと読む)

半導体装置

【課題】誤ってテストモードにエントリされたとしても、正常に動作させる。

【解決手段】半導体装置は、内部回路をテストするテスト回路2に対してテストを開始させるテストモードエントリ信号が入力されたことに応じて、内部のラッチ10をセットすることにより、テスト回路2に対し、テスト回路2の駆動を許可するテストイネーブル信号をラッチ10から出力するテスト信号発生回路1を備える。テスト信号発生回路1が、ラッチ10がテストイネーブル信号を出力している場合、テストイネーブル信号を遅延させて、ラッチ10をリセットするリセット信号を生成するリセット信号生成回路30と、ラッチ10がテストイネーブル信号を出力している場合に、外部から供給されるトグル信号に基づいて、リセット信号生成回路30によるリセット信号を生成する動作を初期化する遅延初期化信号を出力する遅延初期化回路40と、を有している。

(もっと読む)

半導体集積回路、スキャンフリップフロップ及び半導体集積回路のテスト方法

【課題】稼働中の故障診断の際に内部状態の退避及び復帰を図ることができるとともに、回路規模の増大を防ぐことが可能にする。

【解決手段】本発明に係る半導体集積回路10は、スキャンフリップフロップ210,310と、スキャン制御部100とを備え、スキャンフリップフロップ210は、スキャン制御部100の制御に基づいて、内部状態として保持しているバックアップデータを出力し、のスキャンフリップフロップ310は、スキャン制御部100の制御に基づいて、スキャンフリップフロップ210から出力されたバックアップデータを、スキャンフリップフロップ310内に保持するものである。

(もっと読む)

スイッチ装置、伝送路切替装置、および試験装置

【課題】長寿命化した圧電式アクチュエータを備えるスイッチ装置。

【解決手段】第1接点が設けられた基体と、第2接点を移動させて第1接点と接触または離間させるアクチュエータと、を備え、アクチュエータは、支持層と、支持層の上面に形成される第1圧電膜と、支持層を介して第1圧電膜に対向して、支持層の第1圧電膜が形成される面とは反対側の面に設けられ、駆動電圧に応じて伸縮してアクチュエータのそり量を変化させる第2圧電膜と、第1圧電膜および第2圧電膜のそれぞれの上面と下面とに、それぞれの駆動電圧を印加する電極層と、第2圧電膜と第2圧電膜の支持層側とは反対側の電極層との間に形成された導電性酸化物を含む第2導電性酸化物膜と、を有するスイッチ装置を提供する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】半導体集積回路の外部端子としてTRSTがなくても、論理シミュレーションの際に、タップコントローラのステートを確定する。

【解決手段】タップコントローラ2は、リセット端子(端子p4)を有し、回路部3は、タップコントローラ2における状態遷移を制御するステート制御信号と、クロック信号を入力し、ステート制御信号とクロック信号に応じて、リセット端子p4にリセット信号を供給することで、タップコントローラ2のステートを確定する。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体検査装置

【課題】測定針の位置を正確に認識して測定針を正確に半導体装置の電極パッドに接触させることができる半導体検査装置を提供すること。

【解決手段】検査ボード2と、前記検査ボード2に接続された測定針3と、前記測定針3の先端部側を、測定対象の半導体装置12に対して垂直となるように規制する規制板4と、前記測定針3の先端部の位置を光学的に検出し、前記測定対象の半導体装置12を所定の検査位置に移動させることができるステージ11とを備え、前記規制板4の前記ステージ11に対向する面に、前記測定針3の先端部の位置を示す指標6が配置されている。

(もっと読む)

試験管理装置

【課題】試験の信頼性を低下させることなく、試験時間を短縮する。

【解決手段】試験リスト保持部12は、被試験対象物に実施すべき複数の試験項目とその順番を規定した試験リストを保持する。対応テーブル保持部13は、各試験項目の結果値をランク分けし、各ランクと、省略または追加する試験項目とを対応付けたテーブルを保持する。試験結果値取得部22は、試験リストにしたがい実施された試験項目の試験結果値を取得する。ランク判定部23は、対応テーブル保持部13を参照して、試験結果値取得部22により取得された試験結果値をランク分けする。試験リスト管理部24は、ランク判定部23により決定されたランクに応じて試験リストの内容を適応的に変更する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】精度の高いディレイテストを行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路1は、クロック信号CLKに同期して動作する複数のレジスタを有する内部回路11と、クロック信号CLKに同期して動作し第1ノードから第2ノードまでの信号伝搬時間を測定する遅延測定回路12と、遅延測定モードの場合に、遅延測定回路12に対してのみクロック信号CLKを供給し、電圧検出モードの場合に、内部回路11及び遅延測定回路12に対してクロック信号CLKを供給するクロック供給回路13と、を備える。

(もっと読む)

半導体装置、電子機器、および半導体装置の検査方法

【課題】電源端子または接地端子の接続不良を容易に検出する。

【解決手段】半導体装置の電源端子TCと第1の入出力端子T1との間には、電源端子TCがカソード側となり、第1の入出力端子T1がアノード側となるようにダイオードD11が設けられる。判定部10Aは、電源電圧Vccに等しいハイレベルの信号が第1の入出力端子T1に入力されたとき、電源端子TCの電圧が第1の入出力端子T1の電圧よりも低いか否かを判定する。

(もっと読む)

1 - 20 / 870

[ Back to top ]