Fターム[2H092JA33]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 半導体層 (1,729) | 大きさ (545) | 厚さ規定 (269)

Fターム[2H092JA33]に分類される特許

1 - 20 / 269

半導体装置

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程により、ソース電極層及びドレイン電極層を形成後、酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の不純物を除去する工程を行う。

(もっと読む)

薄膜トランジスタ

【課題】バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供する。

【解決手段】表示装置用のボトムゲート型の薄膜トランジスタであって、基板1と、ゲート電極配線2と、ゲート絶縁膜3と、チャネルとなる第1の半導体層4と、第1及び第2のコンタクト層5a、5bとなる第2の半導体層と、ソース又はドレイン電極配線7a、7bとを有し、ソース又はドレイン電極配線7a、7bに対して露出する第2の半導体層の露出部に、絶縁性半導体層6a、6bが形成されている。

(もっと読む)

半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタを具備する画素において、開口率の向上を図る。

【解決手段】酸化物半導体を用いたトランジスタ881は、リーク電流が小さいため、画素880内の容量素子を設ける必要がなくなる。または容量素子を小さくすることができ、たとえば液晶容量よりも小さくすることができる。これらによって、画素880の開口率を向上することができる。前記トランジスタのチャネル形成領域は、酸化物半導体を有し、前記容量素子の容量は、前記液晶素子の容量よりも小さい。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜の水素濃度および酸素欠損を低減する。また、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させる。

【解決手段】下地絶縁膜と下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜に重畳して設けられたゲート電極と、を有し、下地絶縁膜は、電子スピン共鳴にてg値が2.01で信号を表し、酸化物半導体膜は、電子スピン共鳴にてg値が1.93で信号を表さない半導体装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】酸化物半導体層、及びチャネル保護層を覆うようにソース電極層、及びドレイン電極層となる導電膜を形成した後、酸化物半導体層、及びチャネル保護層と重畳する領域の導電膜を化学的機械研磨処理により除去する。ソース電極層、及びドレイン電極層となる導電膜の一部を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、チャネル保護層を有することにより、導電膜の化学的機械研磨処理時に当該酸化物半導体層に与える損傷、または膜減りを低減できる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。該半導体装置を作製する。半導体装置を歩留まりよく作製し、生産性を向上させる。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程によりゲート電極層、又はソース電極層及びドレイン電極層を形成後、ゲート電極層又は酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の残留物を除去する工程を行う。

(もっと読む)

酸化物半導体及び半導体装置

【課題】酸化物半導体の組成若しくは欠陥制御をすることを目的の一とし、また、薄膜ト

ランジスタの電界効果移動度を高め、オフ電流を抑えつつ十分なオンオフ比を得ることを

他の目的の一とする。

【解決手段】InMO3(ZnO)n(M=Ga、Fe、Ni、Mn、Co及びAlから

選ばれた一又は複数の元素、nは1以上50未満の非整数)でありさらに水素を含む。こ

の場合において、Znの濃度がIn及びM(M=Fe、Ga、Ni及びAlから選ばれた

一又は複数の元素)よりも低くする。また、当該酸化物半導体はアモルファス構造を有し

ている。ここでnの値は、好ましくは1以上50未満の非整数、より好ましくは10未満

の非整数とする。

(もっと読む)

積層構造、有機半導体素子、配線および表示装置、並びに有機半導体素子の製造方法

【課題】バリア性の高い保護層を有する積層構造、有機半導体素子、配線および表示装置、並びに有機半導体素子の製造方法を提供する。

【解決手段】導体または半導体を含む有機層と、絶縁材料により構成され、前記有機層を覆う保護層と、外周が前記絶縁材料と親和性を有する親和層に覆われ、前記保護層に分散された複数の粒体とを備えた積層構造。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制すること。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜において、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域は、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さくする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 光リーク電流を抑制した高い耐光性を有するTFTを、製造工程を簡素化することにより低コストで実現する。

【解決手段】 TFT100は、絶縁基板107としてのガラス基板上に形成された遮光膜113と、遮光膜113上に形成された絶縁膜112と、絶縁膜112上に形成された半導体膜111と、半導体膜111上に形成されたゲート絶縁膜104とを基本的に有する。遮光膜113、絶縁膜112及び半導体膜111の三層から成る積層体100aは、各層が同時にパターニングされている。そして、積層体100aの各層がシリコン又はシリコンを含む材料から成る。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いたボトムゲート型のトランジスタにおいて、高いゲート電圧がゲート電極層に印加される場合、ドレイン電極層の端部近傍(及びソース電極層の端部近傍)に生じる恐れのある電界集中を緩和し、スイッチング特性の劣化を抑え、信頼性が向上された構造を提供する。

【解決手段】チャネル形成領域上に重なる絶縁層の断面形状を、テーパ形状とし、チャネル形成領域上に重なる絶縁層の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。チャネル形成領域上に重なる絶縁層の断面形状の下端部のテーパ角θを60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。

(もっと読む)

半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

半導体装置

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な

容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜

上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、

前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、

容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成する。

(もっと読む)

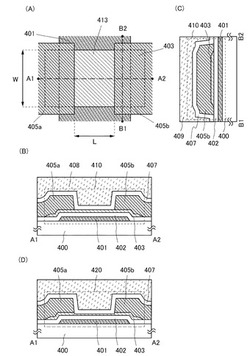

薄膜トランジスタおよび電子機器

【課題】性能向上を容易に実現することが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、ゲート電極と、そのゲート電極から分離絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備える。ソース電極とドレイン電極との間においてゲート電極とソース電極およびドレイン電極とが重ならない第1領域における分離絶縁層の厚さは、ゲート電極とソース電極およびドレイン電極のうちの少なくとも一方とが重なる第2領域における分離絶縁層の厚さよりも小さい。

(もっと読む)

液晶装置、液晶装置の製造方法、電子機器

【課題】液晶層中の不純物の偏在に起因する表示不具合が改善された液晶装置、液晶装置の製造方法、この液晶装置を備えた電子機器を提供すること。

【解決手段】本適用例の液晶装置は、基板としての素子基板10上にトランジスターとしてのTFT30と、画素電極15と、画素電極15をTFT30の半導体層30aにおける第2ソース・ドレイン領域30dに電気的に接続させる柱状のコンタクト部CNT4とを有し、コンタクト部CNT4は、画素電極15の液晶層側の表面において突出部15aを形成している。

(もっと読む)

表示装置および表示装置の製造方法

【課題】酸化物半導体の特性の変化を防ぎつつ、耐圧特性も向上させた薄膜トランジスタを用いた表示装置を提供すること。

【解決手段】表示装置は、薄膜トランジスタを含む。薄膜トランジスタは、ゲート電極と、ゲート電極を覆い絶縁物質を含むゲート絶縁層と、前記ゲート絶縁層の上面に接する酸化物半導体膜と、前記酸化物半導体膜の上面にあり互いに離間する第1の領域と第2の領域にそれぞれ接するソース電極およびドレイン電極と、前記第1の領域と前記第2の領域の間の第3の領域に接し、前記絶縁物質を含むチャネル保護膜と、を含む。平面的にみて前記ゲート電極に重なる前記酸化物半導体膜の上面の領域は第3の領域に含まれかつ小さく、前記酸化物半導体膜のうち前記ゲート電極に重なる部分の一部を除く部分は、前記ゲート電極に重なる部分の前記一部より抵抗が低い。

(もっと読む)

1 - 20 / 269

[ Back to top ]