Fターム[2H092JB67]の内容

液晶−電極、アクティブマトリックス (131,435) | アクティブ基板の能動素子以外の構造 (19,547) | 容量素子 (3,806) | 容量素子の接続 (1,973)

Fターム[2H092JB67]の下位に属するFターム

配線と接続 (216)

容量素子用配線を設けたもの (1,655)

Fターム[2H092JB67]に分類される特許

1 - 20 / 102

半導体装置およびその作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】加熱処理により酸素を放出する絶縁体基板と、該絶縁体基板上に設けられた酸化物半導体膜と、を有し、該酸化物半導体膜にチャネルが形成されるトランジスタを有する半導体装置である。加熱処理により酸素を放出する絶縁体基板は、絶縁体基板の少なくとも酸化物半導体膜が設けられる側に、酸素イオン注入を行うことで作製することができる。

(もっと読む)

アクティブマトリクス基板及び液晶表示装置

【課題】 アクティブマトリクス基板の特性の向上、及び、白黒表示間のコントラストが向上した液晶表示装置を提供する。

【解決手段】 マトリクス状に配置された画素電極と、行方向に隣接する2つの画素電極の両方と重畳して配置された列方向に伸びるソース配線と、ソース配線と交差して配置された行方向に伸びる保持容量配線とを備えるアクティブマトリクス基板であって、上記画素電極、ソース配線及び保持容量配線は、絶縁膜を介してそれぞれ異なる層に形成されており、上記ソース配線は、行方向に隣接する2つの画素電極下にそれぞれ屈曲点を有し、かつ、行方向に隣接する2つの画素電極の間隙を横切る横断部を有し、上記保持容量配線は、行方向に隣接する2つの画素電極の間隙と重畳して配置された列方向に伸びる延伸部を有し、上記ソース配線は、実質的に保持容量配線との交差点でのみ保持容量配線と重畳しているアクティブマトリクス基板。

(もっと読む)

液晶表示装置

【課題】広い視野角を有しており、かつ従来と比べて製造コストが低い液晶表示装置を提供する。

【解決手段】下地絶縁膜101上に形成され、トランジスタのソース102d、チャネル領域102c、及びドレイン102bが形成された島状の第1の半導体膜102と、ソース102d又はドレイン102bとなる第1の半導体膜102と同一の材料から構成され、下地絶縁膜101上に形成された第1の電極102cと、第1の電極102cの上方に形成され、第1の開口パターン112を有する第2の電極108と、第2の電極108の上方に配置された液晶110とを具備する。

(もっと読む)

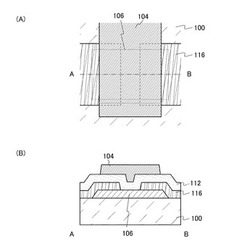

表示装置

【課題】黒レベルを表示するときの液晶表示装置のディスクリネーション及び光漏れとい

った液晶の配向不良を低減でき、コントラストが高く、視認性の良い液晶表示装置を提供

することを課題とする。

【解決手段】画素電極203a〜203bの一部を凸部204に重なり合うように形成す

る。凸部の高さが高すぎると、液晶が基板面に対し斜めに配向することによるため、光漏

れが増える(図1(c))。凸部の高さが低いと、ディスクリネーションを減らす効果が

低い。そこで最適な凸部の高さを決定する。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】トランジスタ上に第1の絶縁膜を有し、第1の絶縁膜上に第1及び第2の配線を有し、第1及び第2の配線上に第2の絶縁膜を有し、第2の絶縁膜上に電極を有し、電極上に第3の絶縁膜を有し、第3の絶縁膜上に画素電極を有し、画素電極は、電極と重なる第1の領域と、電極と重ならない第2の領域と、を有し、画素電極は、第1の配線に電気的に接続されており、第1の配線は、トランジスタのソース又はドレインの一方と電気的に接続されており、電極は、画素部の外側において前記第2の配線と電気的に接続されている。

(もっと読む)

タッチセンシング基板及びそれの製造方法

【課題】タッチセンシング基板及びその製造方法を提供する。

【解決手段】第1光センシング素子は、ベース基板上に配置され、第1の光によって動作し、第1ゲート電極、第1ゲート電極と重なる第1アクティブパターン、第1アクティブパターンと部分的に重なる第1ソース電極、及び第1ドレーン電極を含む。第2光センシング素子は、ベース基板上に配置され、第2の光により動作し、第2ゲート電極、第2ゲート電極と重なる第1アクティブパターンと異なった物質を含む第2アクティブパターン、第2アクティブパターンと部分的に重なる第2ソース電極、及び第2ドレーン電極を含む。第1バイアス配線は、第1及び第2ゲート電極から延長されて第1及び第2ゲート電極と接続される。ソース及びドレーン電極がソース及びドレーン接続電極によりコンタクトホールを通じて接続されることによって、ソース及びドレーン電極のショート不良を防止することができる。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

液晶表示装置

【課題】 表示品位の低下を抑制できる液晶表示装置を提供する。

【解決手段】 本発明の液晶表示装置1は、画素電極218と共通電極216とは、平面視してX方向に沿って交互に配置されており、絶縁部材217は、画素電極218側の第1面217a

と、第1基体21の第1主面21a側の、X方向における両端が第1面217aの両端に比べて

内側に位置している第2面217bとを有しており、画素電極218は、絶縁部材217の第1面217aを被覆しているとともに、平面視してX方向における両端部が隣り合う共通電極216

に重なっていることを特徴とする。

(もっと読む)

液晶表示装置及び電子機器

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。なお、当該酸化物半導体層を高純度化することで、当該トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上述したように当該トランジスタは、85℃という高温においてもオフ電流値を100aA/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置の表示の劣化を抑制することができる。

(もっと読む)

液晶パネル及びそれを用いた電子機器並びに投写型表示装置

【課題】半導体装置でパシベーション膜として一般的に使用されている減圧CVD法による窒化シリコン膜は、膜厚の10%程度のばらつきが生じるので、これを反射型液晶パネルに用いると、パシベーション膜の膜厚のばらつきによって反射率が大きく変化したり、液晶の屈折率が変動したりするという不具合がある。

【解決手段】基板(1)上に反射電極(14)がマトリックス状に形成されるとともに各反射電極に対応して各々トランジスタが形成され、前記トランジスタを介して前記反射電極に電圧が印加されるように構成された液晶パネル用基板において、パシベーション膜(17)として、膜厚が500〜2000オングストロームの酸化シリコン膜を使用し、入射光の波長に応じて膜厚を適当な値に設定するようにした。

(もっと読む)

液晶装置の製造方法、液晶装置、および、液晶装置を備えた電子機器

【課題】簡単な構成で放電による回路構成の損傷を防止できる反射型液晶パネルの製造方法を提供する。

【解決手段】MOS−FETアレイ回路および画素電極が積層された積層領域317Cを含む表示素子部317が一面に複数配列形成され、隣り合う周縁電極317Bが離間する素子側マザー基板と、この素子側マザー基板の一面に対向配置され、素子側マザー基板の一面に対向する対向面に透明電極が設けられた対向側マザー基板と、を用い、素子側マザー基板の周縁電極317Bは、外周縁から隣接する他の周縁電極317Bに向けて突出し先端に向けて幅狭となる放電誘発部317Eを有する。

(もっと読む)

液晶装置、その製造方法、および、電子機器

【課題】MOS−FETアレイ回路の損傷を防止でき、製品の歩留まりを向上できる反射型液晶パネルを提供する。

【解決手段】一面にMOS−FETアレイ回路およびこのMOS−FETアレイ回路上配置された反射電極の延在部317B(導通部319)を含む表示素子部317が設けられた素子基板と、この素子基板の一面に対向配置され、素子基板の一面に対向する対向面に透明電極が形成された対向基板と、素子基板と対向基板との間に、表示素子部317を囲んで環状に設けられたシール材340と、このシール材340で囲まれた領域内に封入された液晶と、を備え、素子基板の外周縁の位置においては、シール材340がMOS−FETアレイ回路が積層する延在部317B(導通部319)に積層しない。

(もっと読む)

表示装置

【課題】表示装置の消費電力を低減し、且つ表示品質の低下を抑制すること。

【解決手段】表示装置の各画素に設けられるトランジスタとして、酸化物半導体層を具備するトランジスタを適用する。なお、当該酸化物半導体層を高純度化することで、当該トランジスタのオフ電流を少なくすることが可能である。そのため、当該トランジスタのオフ電流によるデータ信号の値の変動を抑制することができる。すなわち、当該トランジスタが設けられた画素へのデータ信号の書き込み頻度を低減した場合(休止期間が長期化した場合)における表示の劣化(変化)を抑制することができる。加えて、休止期間において信号線に供給される交流の駆動信号の周波数を低減した場合における表示のちらつきを抑制することができる。

(もっと読む)

液晶表示装置

【課題】画素の開口率の大幅な低下を惹起せしめることなく、画素電極と対向電極との間の容量を大きくできる液晶表示装置の提供。

【解決手段】横電界方式、一本のドレイン信号線から2つの画素列に対しドレイン信号を供給する構成において、隣接する画素の間にドレイン信号線が形成されていない部分を有し、薄膜トランジスタの画素電極と接続されるソース電極を、容量素子の一方の電極として、実質的に画素領域として機能しない領域となる隣接画素の領域にまで延在させて構成する。各画素には、対向電極が形成されており、容量素子の前記一方の電極は、絶縁膜を介して前記対向電極と重畳させて配置される。

(もっと読む)

液晶表示装置の動作方法

【課題】PINダイオードの特性とデータ保持用のTFTの特性とを両立させることが可能な液晶表示装置の動作方法を提供する。

【解決手段】液晶表示装置1の動作方法は、PINダイオード4の真性半導体層が、遮光膜10にHIGH電圧が印加されているときにイントリンシックになるように、所定の濃度の不純物がチャネルドープされており、薄膜トランジスタ6に印加する電圧と同じ極性の電圧を、薄膜トランジスタ6と同じタイミングにおいて遮光膜10に印加するように電圧を切り替える電圧切り替え工程を含んでいる。

(もっと読む)

シングルセルギャップの半透過型液晶ディスプレイ及びその駆動方法

【課題】本発明は、シングルセルギャップの半透過型液晶ディスプレイ及びその駆動方法を提供する。

【解決手段】本発明は、上基板と、複数の画素がマトリックス状に配列され且つ各画素が反射領域及び透過領域を有する下基板と、を備える半透過型液晶パネルを備えるシングルセルギャップの半透過型液晶ディスプレイの駆動方法である。前記下基板の各画素にマルチプレクサを追加し、前記マルチプレクサは、それぞれ反射領域のコンデンサ及び透過領域のコンデンサに接続され、且つ変調走査信号及び異なる電圧データ信号に基づいて、前記異なる電圧データ信号を各画素の反射領域のコンデンサ及び透過領域のコンデンサに入力することによって、透過領域の電圧透過率(VT)曲線及び反射領域の電圧反射率(VR)曲線を一致させる。又、本発明は、シングルセルギャップの半透過型液晶ディスプレイにも関する。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一とする。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成された表示部用配線とを有すればよい。

(もっと読む)

表示装置及び電子機器

【課題】高コントラストな表示特性を得ようとすると保持容量素子のサイズが大きく高精細化できない。

【解決手段】書込みトランジスターと駆動トランジスターとを備え、画素電極に対して表示画像に応じた電位をデータ線から安定して供給する。

(もっと読む)

薄膜トランジスタ、表示装置、および電子機器

【課題】酸化物半導体層の還元および酸素欠陥による劣化を防止でき、これにより長期に安定した特性を維持可能な薄膜トランジスタを提供することを目的とする。

【解決手段】非晶質酸化物からなる酸化物半導体層7と、この酸化物半導体層7に接して設けられたソース電極9sおよびドレイン電極9dとを備えている。そして特に、ソース電極9sおよびドレイン電極9dが、イリジウム(Ir)または酸化イリジウム(IrO2)を用いて構成されている。また、酸化物半導体層7は、酸化物材料からなる絶縁ゲート絶縁膜5および絶縁膜11で覆われている。

(もっと読む)

アクティブマトリクス型表示装置

【課題】表示装置の画素を構成する電荷保持容量の電流リーク電流を防止し、表示装置の表示画質低下を防止する技術を提供する。

【解決手段】表示装置は、ポリシリコン3とパッド電極8とが接続する第1のコンタクトホール7と、有機絶縁膜に開口した第2のコンタクトホール12と、パッド電極8と画素電極16とが接続する第3のコンタクトホール15と、共通電極13とを有する。これらを平面視した際に、第1のコンタクトホール7と第3のコンタクトホール15は第2のコンタクトホール12の内側に有り、第1のコンタクトホール7と第3のコンタクトホール15は互いに重ならず、ゲート線5に垂直な方向では第3のコンタクトホール15、第1のコンタクトホール7、第2のコンタクトホール12の端部、共通電極13の順に並び、かつ、ゲート線5に平行な方向では第2のコンタクトホール12の端部がパッド電極8の外側に位置する。

(もっと読む)

1 - 20 / 102

[ Back to top ]