Fターム[2H092KA21]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子、光導電体層の材料 (8,799) | 容量素子用絶縁層 (389)

Fターム[2H092KA21]の下位に属するFターム

Fターム[2H092KA21]に分類される特許

1 - 20 / 24

液晶表示装置

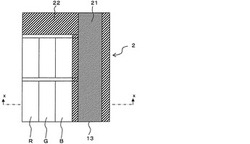

【課題】 配線容量の低減を図り、液晶表示装置の高精細化や狭額縁化を図る。

【解決手段】 走査線及び信号線の交点に配列されるスイッチング素子12と、マトリクス状に配置されスイッチング素子によって駆動される画素電極と、画素電極の印加電圧を保持するための保持容量とを有するアレイ基板2と、対向電極を有し、アレイ基板2と所定の間隔を隔てて対向配置される対向基板3とを備え、これらアレイ基板2と対向基板3の間に液晶層が封入されてなる液晶表示パネル1を備えた液晶表示装置である。アレイ基板2の電源配線及び電気信号配線の少なくとも一部(例えば保持容量配線13や額縁領域の引き出し配線41)は、配線上に誘電率の低い絶縁性着色層(青色絶縁性着色層21)が積層された構造を有する。

(もっと読む)

半導体装置、半導体装置の製造方法および電気光学装置

【課題】ゲート電極の形状を改良して、インパクトイオン化の原因となるドレイン端での電界集中を防止可能な薄膜トランジスタを備えた半導体装置、この半導体装置の製造方法、および当該半導体装置を素子基板として用いた電気光学装置を提供すること。

【解決手段】半導体装置10xの薄膜トランジスタ30nにおいて、ゲート電極3nは、その表面を酸化してなるシリコン酸化膜3sにより覆われて、エッジ部分3w、3x、3y、3zが丸みを有しているため、ゲート電極3nには、電界の集中するエッジ部分がない。このため、ゲート電極3nのエッジ部分に対してゲート絶縁層2を介して対向するチャネル領域130nのドレイン端では、電界が集中しないので、インパクトイオン化が発生しにくい。それ故、下地絶縁層12上に形成された薄膜トランジスタ30nであっても、良好な電流−ゲート電圧特性を有する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】容量結合駆動方式の液晶表示装置において、駆動ICチップの装着時の熱圧着操作に起因する局所的な輝度レベルのズレによる表示不良(ツールムラ)や、液晶層の厚みの偏りに起因する輝度レベルのズレ(ギャップムラ)、またはその他の特定箇所に生じる輝度レベルのズレによる表示不良による表示不良(定点ムラ)を解消または低減することのできるものを提供する。

【解決手段】定点ムラの発生箇所に、補助容量(Cst)形成部の面積を所定量だけ増加させた輝度補正エリア101,102を設ける。すなわち、容量結合駆動の際のバイアス電圧(重畳電圧)を局所的に変化させることで、輝度を抑え、輝度ムラを解消する。この際、面積増加の量は、定点ムラによる輝度のズレの約1/2だけをうち消すように設定する。また、最大補正箇所103から輝度補正エリア101,102の縁に向かって直線的に減少するように設定する。

(もっと読む)

電気光学装置用基板、電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置の表示性能を高める。

【解決手段】電気光学装置用基板は、Y方向に沿って1画素分相互にずらして配置された素子部130a及び130bと、データ線側LDD領域1b−1及び1b−2を夫々覆う部分Py1及びPy3と、画素電極側LDD領域1c−1及び1c−2を夫々覆う部分Py2及びPy4と、データ線側LDD領域1b−3及び1b−4を夫々覆う部分Py5及びPy7と、画素電極側LDD領域1c−3及び1c−4を夫々覆う部分Py6及びPy8とを備える。更に、画素電極9a1及び9a2は、部分Py1及びPy3が形成されX方向に沿って相隣接する画素に夫々配置され、画素電極9a3及び9a4は、部分Py5及びPy7が形成されX方向に沿って相隣接する画素に夫々配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】フォトマスクの枚数を低減しながらも、容易且つ高精度に半導体装置を製造する。

【解決手段】ゲート配線5と、ソース配線6と、ゲート配線5及びソース配線6に接続された薄膜トランジスタ12と、薄膜トランジスタ12に接続された絵素電極11とを備えた半導体装置1を製造する場合に、絵素電極11とソース配線6とを同時にパターン形成する。

(もっと読む)

液晶表示装置

【課題】画素電極と信号配線間の容量を低減して信号配線の信号電圧の影響を小さくし、横筋等のクロストークを防止する。

【解決手段】画素電極8と信号配線6の間の層間絶縁膜7に対して凹部10を形成し、この凹部10に層間絶縁膜7よりも比誘電率の小さな物質、例えば、配向膜11を充填する。これによって、画素電極8と信号配線6間の容量を低減して、画素電極8と信号配線6のクロストークを低減する。

(もっと読む)

薄膜トランジスタパネルおよび液晶表示装置

【課題】 開口率を大きくするため、補助容量ラインをITO等の透明導電材料によって形成した液晶表示装置において、開口率をさらに大きくする。

【解決手段】 オーバーコート膜17の上面には画素電極5が設けられている。画素電極5間におけるアクティブ基板2の上面には走査ライン3が設けられている。走査ライン3上におけるゲート絶縁膜10の上面には補助容量ライン7の補助容量電極部7aが設けられ、その上面には遮光膜8が設けられている。遮光膜8は画素電極5間からの光漏れを防止するためのものである。この場合、遮光膜8はアクティブ基板2上に設けているので、対向基板22下に設ける場合と比較して、遮光膜8の幅を小さくしても、画素電極5間からの光漏れを確実に防止することができ、ひいては開口率をさらに大きくすることができる。

(もっと読む)

電気光学装置の製造方法、電気光学装置および電子機器

【課題】保持容量の単位面積当たりの容量値を高めるための構成を利用して、ゲート絶縁

層の下層側に形成された下層側導電層への電気的な接続を効率よく行うことのできる電気

光学装置の製造方法、電気光学装置、およびこの電気光学装置を備えた電子機器を提供す

ること。

【解決手段】液晶装置の素子基板10を構成するにあたって、ゲート絶縁層4の厚い下層

側ゲート絶縁層4aを形成した後、ドライエッチングにより下電極3cと重なる部分およ

び下層側導電層層接続用コンタクトホール89の形成領域の下層側ゲート絶縁層4aを除

去する。次に、薄い上層側ゲート絶縁層4bを形成し、この上層側ゲート絶縁層4bを保

持容量1hの誘電体層4cとして用いる。

(もっと読む)

黒色層を有する電子デバイス

電子デバイスは、ピクセルの制御回路と、開口部を含む第1の黒色層と、第2の黒色層とを含むことができる。この制御回路は、第1の黒色層と第2の黒色層との間に、ある高度で位置することができる。電子デバイスの形成方法は、基体上に第1の黒色層を形成するステップを含むことができ、第1の黒色層は開口部を含む。この方法は、第1の黒色層を形成するステップの後に、基体上にピクセルの制御回路を形成するステップを含むこともできる。この方法は、制御回路を形成するステップの後に基体上に第2の黒色層を形成するステップをさらに含むことができる。  (もっと読む)

(もっと読む)

液晶表示装置アレイ基板及びその製造方法

【課題】ストレージキャパシタの面積を減らしても、容量を維持するようにした液晶表示装置のアレイ基板及びその製造方法を提供する。

【解決手段】基板上に形成される複数のゲート配線90及びゲート配線90に交差するように複数形成されるデータ配線92と、ゲート配線90及びデータ配線92の交差部に形成される薄膜トランジスタTと、ゲート配線90に平行に形成されるストレージキャパシタ第1電極130と、薄膜トランジスタTのドレイン電極116と電気的に接触されて第1電極130領域上に形成されるストレージキャパシタ第2電極136を含む画素電極と、ゲート配線90の所定領域及びデータ配線92と薄膜トランジスタTが形成される領域に対応するように前記基板上に形成されるブラックマトリックス95と、が含まれる。

(もっと読む)

液晶表示装置およびその製造方法

【課題】大きな安定化蓄積容量を有する液晶表示装置を提供する。

【解決手段】液晶表示装置は、薄膜トランジスタおよび蓄積容量を有するTFT基板と、カラーフィルタ基板と、前記基板間に液晶を有し、前記蓄積容量は、下部電極(2、11)と、この下部電極を覆う第1の絶縁膜(3、13A)と、前記第1の絶縁膜を覆う第2の絶縁膜(6、15)と、第2の絶縁膜の上に形成された上部電極(4、18A)を備える。

(もっと読む)

平面表示装置

【課題】 半透過型の平面表示装置において、フリッカが少ない良好な表示を得る。

【解決手段】 平面表示装置において、透過電極と走査線Gnとの間の寄生容量CgAと、透過電極に対する全寄生容量CloadAと、画素電極15b、17bと走査線Gnとの間の寄生容量CgBと、画素電極15b、17bに対する全寄生容量CloadBとを、CgA/CloadA=CgB/CloadBの関係式が成り立つように設定する。

(もっと読む)

液晶表示パネル

【課題】視角特性の対称性に優れたMVAモードの液晶表示パネルを提供する。

【解決手段】アレイ基板101及び対向基板102と、負の誘電異方性を有する液晶組成物を含みアレイ基板101及び対向基板102間に挟持される液晶層190と、アレイ基板101及び対向基板102の少なくとも一方において所定方向に伸びるようにして並べられ、液晶層190内に得られる電界の傾きを制御して液晶分子190Aの平均的なダイレクタ方向が所定方向に直交する複数の配向領域Iに液晶層190を配向分割する複数の傾き制御部15、18とを備え、液晶層190は液晶分子190Aの平均的なダイレクタ方向が所定方向に直交する方向からずれた複数の配向緩和領域A〜Hを有し、複数の配向緩和領域A〜Hの平均的なダイレクタ方向の単位ベクトルnをこれら配向緩和領域の面積Sでそれぞれ重み付けしたベクトル値の総和がゼロを含む所定の範囲内に設定される。

(もっと読む)

半導体装置の作製方法

【課題】レジストが形成されている半導体にイオンの導入すると、イオンとレジストの成分とが反応してガス(解離ガス)が発生し、解離ガスの成分が半導体に導入され、該半導体の物性を低下させる要因となっている。

【解決手段】有機膜から発生する解離ガスの処理を行うことを特徴とする。特に、本発明は、イオンの導入を行う前の解離ガスの処理を行うことを特徴とする。そのための方法として、イオンの導入を複数回に分けて行うことを特徴とする。解離ガスは、イオンの導入が始まった直後に最も多く発生する。そのため、イオンの導入を複数回に分け、少なくとも2回目以降のそれぞれのイオンの導入において、排気を行い解離ガスを処理室内から除去しながらイオンの導入を行えば、解離ガスの成分が半導体中に導入されることを低減もしくは防止することが可能となる。

(もっと読む)

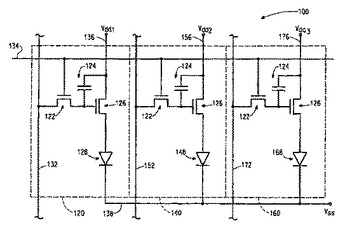

表示装置

【課題】液晶表示装置の静電破壊強度を向上する。

【解決手段】第2の半導体層12の行方向(紙面上で左右方向)に沿ったエッジE2は、保持容量ライン122の行方向に沿ったエッジE3より外側に配置されている。この第2の半導体層12のエッジE2は、第1の半導体層10に近い側のエッジである。第2の半導体層12のエッジE2を被覆しているゲート絶縁膜12の部分は、保持容量ライン122によって被覆されていない。また、第2の半導体層12の右側のエッジE5はコンタクト形成領域12Aからまず直線的に列方向に延び、その途中で行方向に直角に屈曲し、さらに列方向に屈曲して保持容量ライン122と交点P2で交差するようにしている。

(もっと読む)

電気光学装置および電子機器

【課題】 2つの非線形素子を極性を逆向きにして並列に電気的して画素スイッチング素子を構成した場合でも、その占有面積を狭くすることのできる電気光学装置、およびこの電気光学装置を備えた電子機器を提供すること。

【解決手段】 電気光学装置の素子基板には、データ線2(第1の上電極53)、第1の下電極51、第2の上電極54および第2の下電極52が略井桁状に配置され、第1の下電極51とデータ線2との重なり領域、および第2の下電極52と第2の上電極54との重なり領域に第1の非線形素子5aおよび第2の非線形素子5bが形成され、これらの非線形素子5a、5bは、極性を逆向きにして並列に接続されて画素スイッチング素子5として用いられる。

(もっと読む)

表示装置の欠陥検出方法および表示装置の欠陥検出装置

【課題】 マトリクス構造における進行性のある欠陥を容易に検出可能にする。

【解決手段】 マトリクス構造で格子状に交差する複数のゲート線4c、4d及び複数のデータ線3aを有する。複数のゲート線4c、4d及び複数のデータ線3aの交差部毎に配置された画素部2aに所定の駆動電圧が印加される。駆動電圧よりも大きな電圧を画素部に印加して欠陥110の進行を加速させる工程と、駆動電圧を画素部2aに連続的に印加して欠陥110の進行を加速させる工程との少なくともいずれか一方の工程を有する。

(もっと読む)

画素構造、アクティブマトリクス基板、アクティブマトリクス基板の製造方法、電気光学装置、並びに電子機器

【課題】 製造プロセスにおける半導体層の熱的制限の影響が少なく、低コスト化に有利な画素構造を提供する。

【解決手段】 画素構造は、画素電極20と、この画素電極20に対応するスイッチング素子10とを有する。画素電極20とスイッチング素子10とが同一の基板P上に形成されており、スイッチング素子10における半導体層11に比べて基板P側の層(第1層L1)に画素電極20が配されている。

(もっと読む)

電気光学装置用基板、電気光学装置及び電子機器

【課題】外部からのプローブを接触される等の必要がなく、十分な測定精度の得られる検査を実現する。

【解決手段】 互いに交差する複数の走査線及び複数のソース線Sと、前記複数の走査線及び前記複数のソース線の交差に対応してマトリックス状に配置された複数の画素と、第1及び第2の端子を有し、前記第1の端子に供給される電位信号と前記第2の端子に供給される電位信号との電位を比較して、前記第1の端子に供給される電位信号が低い場合には前記第1の端子の電位をより低くし、前記第1の端子に供給される電位信号が高い場合には前記第1の端子の電位をより高くして出力する増幅器4aと、前記第1及び第2の端子の一方に基準電位を供給し、他方に前記画素に書込まれた電位信号を読み出して供給する供給手段13,9’と、前記第1及び第2の端子に夫々電気的に接続される第1及び第2の容量4i,4hとを具備したことを特徴とする。

(もっと読む)

電気光学装置、電子機器、および電気光学装置の製造方法

【課題】 補助容量を設けた場合でも、画素の開口率が低下することのない電気的光学装置、電子機器、および電気光学装置の製造方法を提供すること。

【解決手段】 液晶装置において、二端子型非線形素子14が形成された第1基板10には、さらに、補助容量線17と、補助容量18と、補助容量18および二端子型非線形素子14の上層側に形成された層間絶縁膜とが形成されている。第2電極133と二端子型非線形素子14の第2導電層131は一体の導電パターン139から構成されている。画素電極16は、層間絶縁膜19の上層側に形成され、かつ、層間絶縁膜19のコンタクトホール191を介して第2電極133に電気的接続している。

(もっと読む)

1 - 20 / 24

[ Back to top ]