Fターム[3K107HH02]の内容

エレクトロルミネッセンス光源 (181,921) | 回路 (6,105) | 入力波形 (613)

Fターム[3K107HH02]に分類される特許

1 - 20 / 613

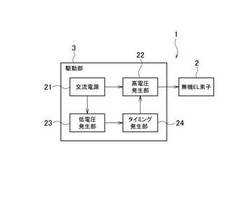

無機EL発光装置

【課題】無機EL素子の寿命の低下および消費電力を抑えつつ、輝度を向上する。

【解決手段】無機EL発光装置1は、一対の電極を有する無機EL素子2と、無機EL素子2の一対の電極に交流電圧を印加する駆動部3とを備え、交流電圧の波形は、半周期期間ごとに、第1の矩形波、および第1の矩形波に対して時間的に離間した第1の矩形波と同極性の第2の矩形波を有する。

(もっと読む)

発光装置、モジュール、電子機器

【課題】電気光学装置において、新規の構成を有する画素回路を用いることにより、従来

の構成の画素よりも高い開口率を実現することを目的とする。

【解決手段】i行目を除くゲート信号線の電位は、i行目のゲート信号線106が選択さ

れている以外の期間においては定電位となっていることを利用し、i−1行目のゲート信

号線111をi行目のゲート信号線106によって制御されるEL素子103への電流供

給線として兼用することで配線数を減らし、高開口率を実現する。

(もっと読む)

レベルシフタ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路の最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路を提供する。

【解決手段】第1固定電源側の2つのトランジスタ回路が第1導電型のトランジスタから成り、第2固定電源側の2つのトランジスタ回路が第2導電型のトランジスタから成るとともに、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成るレベルシフタ回路において、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

表示装置およびその駆動方法

【課題】簡単な画素回路構成で製造歩留まりの低下がなく、表示品質を維持しつつEL素子の輝度劣化の回復を実現できる表示装置およびその駆動方法を提供する。

【解決手段】複数の発光画素を有する表示装置3であって、発光画素22は、駆動トランジスタ102と、信号電流が流れることにより発光する発光素子101と、データ線11と発光素子101との導通及び非導通を切り換えるスイッチングトランジスタ107とを備え、表示装置3は、信号電圧をデータ線11に供給するデータ駆動回路141と、所定のバイアス電圧をデータ線11に供給するバイアス供給回路142とを備え、信号電流を発光素子101に流さない期間と同期して、制御線13を電圧変化させることでスイッチングトランジスタ107をオン状態とすることにより、発光素子101のアノードに所定のバイアス電圧を印加する。

(もっと読む)

表示装置および表示方法

【課題】表示画質を高めることができる表示装置を得る。

【解決手段】表示画面から間欠的に表示光が発せられるように制御される表示部と、表示部に表示されるべき映像の動き量に基づいて、表示光が発せられる表示光タイミングを制御する制御部とを備える。この表示装置では、表示部の表示画面から、間欠的に表示光が発せられることにより、表示が行われる。その際、表示光タイミングは、表示部に表示されるべき映像の動き量に基づいて制御される。

(もっと読む)

発光装置

【課題】表示むらを抑制すること、又は異なる画素におけるトランジスタ特性のばらつきを低減すること、あるいは、発光素子の劣化等に伴う輝度の低下を抑制する事が可能な発光装置を提供する。

【解決手段】基板100の上に設けられたトランジスタ121と、発光素子109とを具備する画素部120を有し、トランジスタは、チャネル形成領域を形成する単結晶半導体層122を有し、基板と単結晶半導体層との間に、酸化シリコン層が設けられており、トランジスタのソース又はドレインと発光素子の電極とが電気的に接続され、発光素子の発光時にトランジスタを飽和領域で動作させる。また、発光素子の階調表示を、トランジスタのゲートに印加する電位を変化させることによって行う。

(もっと読む)

発光素子

【課題】第1画素とこの第1画素と異なる領域に形成された第2画素とを有する発光素子において、下部電極のレイアウトを簡単にすることができると共に、第1、第2画素の見栄えが互いに異なることを抑制することができる発光素子を提供する。

【解決手段】第1画素Aの第1下部電極20aと第2画素Bの第2上部電極22bとを電気的に接続し、第1画素Aの第1上部電極22aと第2画素Bの第2下部電極20bとを電気的に接続する。これによれば、外部回路と接続される下部電極を1つにすることができ、下部電極のレイアウトが複雑になることを抑制することができる。また、第1画素Aの第1下部電極20aと第2画素Bの第2下部電極20bとを立体交差させる必要もなく、第1、第2画素A、Bの見栄えが互いに異なることを抑制することもできる。

(もっと読む)

表示装置

【課題】大型でも均一な画像が得られる表示装置を提供する。

【解決手段】表示装置は、画素回路がマトリクス状に配置された画素アレイ部とこれを駆動する駆動部を有し、駆動部は、各画素回路において、第一の補正動作および発光動作を少なくとも行うように構成されており、第一の補正動作の期間は、書込制御線駆動部が、サンプリングトランジスタを導通状態に制御するタイミングに応じて規定され、書込制御線駆動部と電源駆動部とは、画素アレイ部の両側から所定の信号と所定の電源電圧とを供給して各画素回路を駆動し、各画素回路における補正動作期間のばらつきを抑制する。

(もっと読む)

発光装置

【課題】トランジスタがノーマリオンであっても、閾値電圧のばらつきによる画素間の輝度のばらつきが抑えられる発光装置。

【解決手段】通常のゲート電極(第1ゲート電極)の他に、閾値電圧を制御するための第2ゲート電極が備えられたトランジスタを用いて、発光素子への電流の供給を制御する構成を有する。さらに、上記発光装置は、上記トランジスタの第1ゲート電極とドレイン端子の間の導通または非導通を選択する単数または複数のスイッチを有する。そして、トランジスタの閾値電圧を取得する際に、上記スイッチによりトランジスタの第1ゲート電極とドレイン端子の間を導通させ、なおかつ、第2ゲート電極の電位を制御することでトランジスタの閾値電圧をシフトさせる構成とする。

(もっと読む)

半導体装置、シフトレジスタ、表示装置

【課題】非選択期間においてノイズが少なく、且つトランジスタを常時オンすることのない半導体装置、シフトレジスタ回路を提供することを目的とする。

【解決手段】第1〜第4のトランジスタを設け、第1のトランジスタの、ソースとドレインのうち一方を第1の配線に接続し、他方を第2のトランジスタのゲート電極と接続し、ゲート電極を第5の配線に接続し、第2のトランジスタの、ソースとドレインのうち一方を第3の配線に接続し、他方を第6の配線に接続し、第3のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第2のトランジスタのゲート電極に接続し、ゲート電極を第4の配線に接続し、第4のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第6の配線に接続し、ゲート電極を第4の配線に接続する。

(もっと読む)

表示装置

【課題】駆動用トランジスタの特性のばらつきに起因する、画素間における表示素子の輝

度ムラを抑えることができる表示装置の提案を課題とする。

【解決手段】駆動トランジスタと、スイッチと、表示素子と、を有し、前記駆動トランジ

スタは、ソース又はドレインが第1の配線に電気的に接続され、ゲートが第2の配線に電

気的に接続されている表示装置である。そして、前記トランジスタのソース又はドレイン

から前記表示素子への電流の供給を前記スイッチによって制御する。

(もっと読む)

表示装置

【課題】駆動トランジスタと、駆動トランジスタのソースに電気的に接続される発光素子とが配設されている画素を有する表示装置において、当該発光素子が経時劣化する場合における表示不良を抑制する。

【解決手段】駆動トランジスタが発光素子に電流を供給する期間前にキャパシタの一方の電極と他方の電極に印加される電圧と略同一の電圧を当該期間における駆動トランジスタのゲートとソース間の電圧として保持する。具体的には、当該期間においてキャパシタの一方の電極と駆動トランジスタのゲートが電気的に接続するノードの電位を浮遊状態とし、且つキャパシタの他方の電極と駆動トランジスタのソースを電気的に接続させる。これにより、発光素子の経時劣化に伴って駆動トランジスタのソースの電位が変動する場合であっても当該駆動トランジスタのゲートとソース間の電圧を略一定に保持することができる。

(もっと読む)

半導体発光装置

【課題】半導体発光素子の発光効率を向上することができる半導体発光装置。

【解決手段】半導体発光素子D1と、半導体発光素子D1に流れるパルス電流を遮断して半導体発光素子D1の発光量を制御し且つパルス電流の遮断に伴って発生する半導体発光素子D1の拡散容量の放電が終了する前に半導体発光素子D1にパルス電流を流すように、半導体発光素子D1に印加すべきパルス信号のオン/オフのタイミングを制御するパルスタイミング制御部1とを備える。

(もっと読む)

電気光学装置、電気光学装置の駆動方法および電子機器

【課題】半導体基板にOLEDのような発光素子を含む画素回路を形成する。

【解決手段】画素回路110は、駆動トランジスター125、スイッチングトランジスター122、発光素子130を含み、これらの素子が半導体基板に形成されている。スイッチングトランジスター122には、第1基板電位V4が供給され、駆動トランジスター125には、第1基板電位V4とは異なる第2基板電位V3が供給される。

(もっと読む)

半導体装置

【課題】発光装置に含まれる発光素子の発光輝度を周囲の情報に応じて調節する表示シス

テムを提供する。

【解決手段】本発明において、センサー2011が周囲の情報を電気信号として検出し、

これをCPU2013は、あらかじめ設定しておいた比較データに基づきEL素子の発光

輝度を補正するための補正信号に変換する。この補正信号が電圧可変器2010に入力さ

れることにより、電圧可変器2010が所定の補正電位をEL素子に印加する。以上の表

示システムによりEL素子2003の発光輝度を制御することができる。

(もっと読む)

表示装置および電子機器

【課題】画面の明るさが瞬間的に変化する(フラッシュ)現象を防止または抑制する。

【解決手段】発光ダイオード(OLED)、駆動トランジスタMdおよび保持キャパシタCsを含む画素回路3(i,j)と、画素回路3(i,j)の駆動のための制御信号(電源駆動パルスDS)を発生する駆動信号発生回路(水平画素ライン駆動回路41)とを有する。水平画素ライン駆動回路41は、OLEDを逆バイアスしない発光停止のための期間(発光停止処理期間(LM−STOP))を規定する第2レベル(中電位Vcc_M)と、中電位Vcc_Mより低いレベルでOLEDを逆バイアスする処理期間を規定する第1レベル(低電位Vcc_L)と、中電位Vcc_Mより高く発光許可期間を規定する第3レベル(高電位Vcc_H)とを有する電源駆動パルスDSを発生し、画素回路3(i,j)画素回路に供給する。

(もっと読む)

電気光学装置、電気光学装置の駆動方法および電子機器

【課題】発光素子に電流を供給するトランジスターの特性を十分な精度で補償する。

【解決手段】画素回路110は、ゲート・ソース間の電圧に応じた電流を供給するトランジスター124と、トランジスター124により供給された電流に応じた輝度で発光するOLED130とを含む。トランジスター124のゲート・ソース間を、初期化期間にリセットし、閾値補償期間に閾値電圧をセットする。書込期間の開始から階調レベルに応じた時間が経過したタイミングであって、当該階調レベルによって指定される階調が暗くなるにつれて時間的に早まるタイミングで、トランジスター124のゲート・ソース間に階調に応じた電圧分、変化させ、発光期間に第1トランジスター124のゲート・ソース間の電圧に応じた電流をOLED130に供給する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

降圧DC/DCコンバータおよびその制御回路、それを用いた照明機器

【課題】発光素子を駆動する降圧DC/DCコンバータの動作周波数を安定化する。

【解決手段】電流検出回路10は、スイッチングトランジスタM1に流れる電流IM1が所定のピーク電流に達するとアサートされるオフ信号SOFFを生成する。パルス生成回路30は、オン信号SON、オフ信号SOFFがアサートされる度にレベルが遷移するパルス信号S2を生成する。電流源24は、DC/DCコンバータ6の出力電圧VOUTに応じた充電電流により第1キャパシタ22を充電する。演算回路50は、DC/DCコンバータ6の入力電圧VINおよび出力電圧VOUTに応じたしきい値電圧VC4を、VC4=(VIN−VOUT)×VOUT/VIN×m(mは定数)にもとづいて生成する。第1コンパレータ28は、第1キャパシタ22の電圧がしきい値電圧VC4に達するとアサートされるオン信号SONを生成する。

(もっと読む)

電気光学装置、電気光学装置の駆動方法および電子機器

【課題】シリコン基板にOLEDのような発光素子を含む画素回路を形成する。

【解決手段】画素回路が配列する表示部100と、表示部100から離間して囲むように設けられ、複数の画素回路を駆動する走査線駆動回路140、データ線駆動回路150とがシリコン基板に形成される。Nウェル104は、表示部100にわたって連続的に形成される。複数の画素回路の各々は、それぞれ複数のトランジスターを有し、当該トランジスターはNウェル104に共通に形成されるとともに、基板電位を共通である。表示部100におけるNウェル104は導電型の異なるP型半導体基板領域102で囲まれる。

(もっと読む)

1 - 20 / 613

[ Back to top ]