Fターム[4G077EE08]の内容

結晶、結晶のための後処理 (61,211) | 結晶成長共通−成長前の基板の処理、保護 (913) | 基板の表面処理 (858) | 基板へのドーピング (28)

Fターム[4G077EE08]に分類される特許

1 - 20 / 28

炭化珪素ウェハの製造方法、炭化珪素ウェハ及び炭化珪素半導体素子並びに電力変換装置

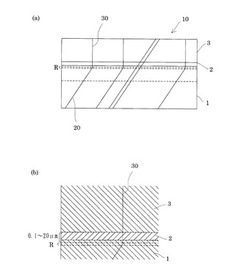

【課題】製造工程の複雑化を防止し、炭化珪素基板の制約がなく、かつ基底面転位(BPD)をより確実に貫通刃状転位(TED)に転換できる炭化珪素ウェハの製造方法を提供する。

【解決手段】炭化珪素基板1の一方面にSiイオンを注入し、又は電子線照射する第1工程と、炭化珪素基板1をアニール処理する第2工程と、炭化珪素基板1の一方面側をエピタキシャル成長させてエピタキシャル膜3を得を形成する第3工程とを備える。前記炭化珪素基板に注入されるイオンは、Siイオン、Cイオン、Hイオン、Heイオン、Pイオン、Alイオン、Bイオン及びNイオンからなる群から選択される少なくとも一種である。

(もっと読む)

導電層付き単結晶ダイヤモンドおよびそれを用いた工具

【課題】寿命検出機構、接触検出機構を備えた工具の刃先として利用可能な、導電層を有する単結晶ダイヤモンド及び該単結晶ダイヤモンドを利用した工具の提供。

【解決手段】少なくとも一つ以上の層状の導電層が主面にほぼ平行に形成されており、該導電層は絶縁性の単結晶ダイヤモンドの内部に形成されており、該単結晶ダイヤモンドの側面まで前記導電層が貫通していることを特徴とする導電層付き単結晶ダイヤモンド。前記単結晶ダイヤモンドとそれを支える支持体とを具備し、単結晶ダイヤモンドと支持体とは導電性の接合材で接合されており、単結晶ダイヤモンドの内部に形成された導電層と支持体とは接触している接合材を介して電気的に接続されていることを特徴とする導電層付き単結晶ダイヤモンドを用いた工具。

(もっと読む)

半導体基板及びその製造方法

【課題】単純な単結晶シリコン基板を出発基板として窒化ガリウム膜を形成することができ、反りやクラックが抑制された半導体基板及びその製造方法を提供する。

【解決手段】半導体基板10は、単結晶シリコン基板11と、前記単結晶シリコン基板11の最表面を除く表層領域に形成された転位層12と、前記単結晶シリコン基板11の前記最表面に形成されたバッファ層13と、前記バッファ層13の表面に形成された窒化ガリウム層14とを備えている。転位層12は、窒化ガリウム層14が形成された単結晶シリコン基板14の表層領域に転位が発生し且つ単結晶シリコン基板11の最表面には転位が発生しない条件下でイオン注入することにより形成される。イオン注入では、ドーズ量が5E+14atoms/cm2以上5E+17atoms/cm2以下のアルゴンイオンを注入する。

(もっと読む)

半導体基板及びその製造方法

【課題】単純な単結晶シリコン基板を出発基板として窒化ガリウム膜を形成することができ、反りやクラックが抑制された半導体基板及びその製造方法を提供する。

【解決手段】半導体基板10は、面方位(111)を有する単結晶シリコン基板11と、単結晶シリコン基板11の最表面を除く表層領域に形成された不完全な絶縁性を有する埋め込み酸化層12と、単結晶シリコン基板11の最表面に形成されたバッファ層13と、バッファ層13の表面に形成された窒化ガリウム層14とを備えている。埋め込み酸化層12は、単結晶シリコン基板11の表面にドーズ量が5E+14atoms/cm2以上5E+17atoms/cm2以下の酸素イオンを注入した後、500〜1350℃で熱処理することにより形成される。

(もっと読む)

炭化珪素単結晶の製造方法

【課題】p層とn層を順次積層させなくても、多形や転位の引継ぎを抑制しつつ、貫通転位を低減できるSiC単結晶の製造方法を提供する。

【解決手段】縦型MOSFETのドレインリークなどのリークを引き起こす転位は貫通らせん転位であるということに基づき、Alイオンの注入および活性化アニール後に溶融KOHエッチング等を行うことにより、リーク部に相当する場所に非常に深いエッチピット1bを形成する。そして、その表面に、エッチピット1bの側壁部に成長した部分同士が互いに接触する条件にてSiC成長層4をエピタキシャル成長させることで、SiC成長層4に転位が引き継がれないようにする。これにより、貫通らせん転位1aが存在しない表面を有するSiC成長層4を得ることが可能となる。したがって、p層とn層を順次積層させなくても、多形や転位の引継ぎを抑制しつつ、貫通転位を低減できるSiC単結晶を製造することができる。

(もっと読む)

ダイヤモンドの剥離方法

【課題】ダイヤモンドの剥離プロセスで必要なイオン注入工程を改善してより安価に剥離を実現するダイヤモンドの剥離方法を提供すること。

【解決手段】 ダイヤモンド基板(03)の主面にイオンを注入してダイヤモンド基板にイオン注入層を形成するイオン注入工程と、該イオン注入層(04)を形成した側の基板表面にダイヤモンド膜(02)を成長させて、イオン注入層が、ダイヤモンド層(02、03)に挟まれた構造を有する構造体を形成する工程とを含む工程によって得られた前記構造体をエッチング液に浸漬して電圧を印加し、イオン注入層を電気化学的にエッチングすることで、該ダイヤモンド層を分離する剥離工程を含むダイヤモンドの剥離方法であって、該イオン注入工程において、該イオン注入層として注入エネルギー10keV以上1MeV未満且つ2段以上の多段注入で9.0μm未満の層厚を形成することを特徴とするダイヤモンドの剥離方法。

(もっと読む)

オフ角を有する単結晶基板の製造方法

【課題】単結晶の気相合成において利用できるオフ基板の製造に際して、製造コストを削減でき、且つ同一のオフ角を有する基板を簡単かつ大量に製造することが可能な新規な方法を提供する。

【解決手段】気相合成法による半導体ダイヤモンド等のエピタキシャル成長が可能な材料であって、その表面が、エピタキシャル成長が可能な結晶面に対してオフ角を有する材料を基板として用い、該基板にイオン注入を行って、基板の表面近傍に結晶構造の変質した層を形成し、気相合成法によって該基板上に結晶成長を行い、次いで、成長した結晶層と基板とを分離させて得られた結晶層を基板として用い、該基板にイオン注入を行って、基板の表面近傍に結晶構造の変質した層を形成し、気相合成法によって該基板上に結晶成長を行い、成長した結晶層と基板とを分離させることを特徴とする、オフ角を有する単結晶基板の製造方法。

(もっと読む)

化合物半導体基板

【課題】Si単結晶基板を用いた化合物半導体基板において、化合物半導体基板の機械強度低下と熱伝導率低下を、Si単結晶基板のドーパント濃度制御で低減する。

【解決手段】Si単結晶基板上に中間層とデバイス活性層を備えた化合物半導体基板で、Si単結晶基板は、中間層側の一主面の表面から厚さ方向に向かってドーパント濃度が1×1019atoms/cm3以上1×1021atoms/cm3以下である領域1と、ドーパント濃度が連続的に減少する遷移領域1と、ドーパント濃度が1×1012atoms/cm3以上5×1017atoms/cm3以下である領域2と、ドーパント濃度が連続的に増加する遷移領域2と、ドーパント濃度が1×1019atoms/cm3以上1×1021atoms/cm3以下である領域3とからなる。

(もっと読む)

大領域窒化物結晶およびその作製方法

【課題】大領域のガリウム含有窒化物結晶の成長のための方法を提供する。

【解決手段】転位密度が約107cm−2よりも低い少なくとも2つの結晶201、202を提供する工程と、ハンドル基板を提供する工程と、少なくとも2つの結晶201、202をハンドル基板に対してウェーハ接合する工程と、少なくとも2つの結晶201,202を成長させて、溶合結晶として合体させる工程と、を含み、第1の結晶201と第2の結晶202との間の極性配向不整角度γは、0.5度未満であり、方位配向不整角度αおよびβは1度未満である。

(もっと読む)

炭化珪素基板の製造方法

【課題】製造工程を簡略化すると共に、表層部にらせん転位が存在することを抑制することができるSiC基板の製造方法を提供する。

【解決手段】炭化珪素からなり、主表面および当該主表面の反対面である裏面を備え、らせん転位1を表層部2aに含む欠陥含有基板2を用意する工程と、欠陥含有基板2のうち主表面に外力を印加することにより表層部2aの結晶性を低下させる第1外力印加工程と、外力印加工程の後、欠陥含有基板2を熱処理することにより表層部2aの結晶性を回復させる第1熱処理工程と、を含む製造方法とする。

(もっと読む)

電子デバイス用エピタキシャル基板およびその製造方法ならびにIII族窒化物電子デバイス用エピタキシャル基板

【課題】シリコン基板の所定領域にアルミニウム拡散領域を設け、表面粗さを適正範囲に設定することにより、その上方に成長されるIII族窒化物半導体の結晶性を向上させることができる電子デバイス用エピタキシャル基板およびその製造方法ならびにIII族窒化物電子デバイス用エピタキシャル基板を提供する。

【解決手段】シリコン基板2と、該シリコン基板上に形成した窒化アルミニウム単結晶核生成層と、該窒化アルミニウム単結晶層3上に形成した、少なくとも一組以上の超格子層4を含むバッファ構造体とを具える電子デバイス用エピタキシャル基板であって、前記シリコン基板の表層部には、前記窒化アルミニウム単結晶層と接する表面から基板厚さ方向に広がるアルミニウム拡散領域5が設けられ、前記シリコン基板の、前記窒化アルミニウム単結晶層と接する表面の表面粗さRaは、0.2〜1nmの範囲であることを特徴とする。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】シリコン単結晶基板上に、欠陥密度が低く高品質なエピタキシャル層を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】バッファ層12は、シリコン基板11の格子定数と、エピタキシャル層13の格子定数との間の格子定数をもつ、第3族元素と第5族元素との化合物が選択されればよい。例えば、エピタキシャル層13が上述した3C−SiCから形成される場合、シリコン基板11の格子定数0.543nmと、エピタキシャル層13の格子定数0.435nmとの間の、0.469nmの格子定数をもつ砒化ホウ素が好ましく選択される。

(もっと読む)

炭化シリコンの製造方法

【課題】形成される炭化シリコン層の結晶性を悪化させることなく、従来に比べて生産性を向上させることができる炭化シリコンの製造方法を提供する。

【解決手段】シリコン基板1の表面にシリコン酸化層2を形成し、シリコン基板1内にシリコン酸化層2を通して炭素イオンを注入することによりシリコンと炭素の混在した炭素含有層3を形成し、シリコン基板1からシリコン酸化層2を選択的に除去することにより炭素含有層3を露出させ、シリコン基板1を熱処理して炭素含有層3を単結晶化させることにより単結晶炭化シリコン層4を形成し、熱処理の過程で単結晶炭化シリコン層4の表面に形成された酸化層5を除去することにより単結晶炭化シリコン層4を露出させて、SiCウエハ10を製造する。

(もっと読む)

半導体基板の製造方法

【課題】反りやクラックの抑制された窒化ガリウム層を有する半導体基板を、低コスト、高効率で製造することができる半導体基板の製造方法を提供する。

【解決手段】面方位が(111)のシリコン基板10を準備する工程と、シリコン基板10の両面に窒化ガリウム層12をエピタキシャル成長させる工程と、窒化ガリウム層12がエピタキシャル成長されたシリコン基板10を、エピタキシャル成長面と平行にスライスして2分割するスライス工程とを含み、1枚のシリコン基板10から2枚の窒化ガリウム層12が形成された半導体基板13を製造する。

(もっと読む)

ダイヤモンド材料

高い化学的純度、すなわち低い窒素含量と、高い同位体純度、すなわち低い13C含量とを有する単結晶ダイヤモンド、その製造方法及び該単結晶ダイヤモンドを含むソリッドステートシステムを開示する。 (もっと読む)

単結晶SiC基板の製造方法およびそれによって得られた単結晶SiC基板

【課題】比較的安価な多結晶SiC基板を母材基板として歪みが少なく大型で結晶性の良い単結晶SiC基板を安価に製造する方法を提供する。

【解決手段】Si母材層2に所定厚さの表面Si層3と埋め込み酸化物層4が形成されたSOI基板1に対し、表面Si層3側からPイオンを注入することにより、埋め込み酸化物層4をPSG層6に変成させて軟化点を低下させるPイオン注入工程と、PSG層6が形成されたSOI基板1を炭化水素系ガス雰囲気中で加熱して表面Si層3をSiCに変成させたのち冷却させて表面に単結晶SiC層を形成するSiC形成工程とを行なう。

(もっと読む)

エピタキシャル膜形成装置用のサセプタ、エピタキシャル膜形成装置、エピタキシャルウェーハ及びエピタキシャルウェーハの製造方法

【課題】エピタキシャルウェーハ全体における厚みのバラツキを小さくすることが可能なサセプタを提供する。

【解決手段】半導体ウェーハ22を収容する平面視略円形の凹部21aが設けられ、凹部21aには半導体ウェーハ22を支持する平面視略円形の凸部21dが設けられ、凸部21dの直径d1が凹部21aの直径d2よりも小とされ、かつ凸部21dの直径d1が、凹部21aに半導体ウェーハ22が載置された際に凸部21dと半導体ウェーハ22との境界全体に気相成長反応に供される反応ガスが流通可能となる大きさに設定されていることを特徴とするエピタキシャル膜形成装置用のサセプタ21を採用する。

(もっと読む)

シリコンウェーハの製造方法

【課題】注入したイオンの拡散を抑制しつつ、効果的に効率的よく注入ダメージを除去することができるシリコンウェーハの製造方法を提供する。

【解決手段】シリコン単結晶からなる基板1上にイオン注入処理をおこなう注入工程と、塩化水素ガスを含む雰囲気で熱処理することにより、イオン注入された前記基板1上のイオン注入によるダメージをエッチング除去するダメージ除去工程とを備え、前記ダメージ除去工程におけるエッチング除去量が、前記基板1の深さ方向に対する注入されたイオンのガウス分布の最大濃度深さRpの5〜120%の厚みであるシリコンウェーハの製造方法とする。

(もっと読む)

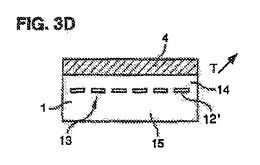

少なくとも1つの窒化材料層を有するハイブリッド基板の製造法

本発明は電子工学分野での応用を目的とする、少なくとも1つのIII/N型窒化材料層を具備してなるハイブリッド基板の製造法であって;六方単結晶の結晶構造を有するIII/N型窒化材料でできた原材基板(1)を選択する工程;前記基板内部に多数のナノ空隙(12)を生じさせて活性層(14)の境界となる脆弱領域(13)を作ることを目的として、前記窒化材料の「c」結晶軸に平行もしくは略平行な平面内にある「注入面」(10)と呼ばれる面の一つを通して、1×1016He+/cm2から1×1017He+/cm2のヘリウムイオンHe+を前記原材基板(1)に注入する工程;および、少なくとも前記ナノ空隙を空隙(12’)へと成長させることが可能な熱授受を含む授受からなる、活性層(14)を原材基板(1)から分離させることが可能な全エネルギー授受を施すことによって前記活性層(14)を移設する工程;からなることを特徴とする製造法に関する。  (もっと読む)

(もっと読む)

半導体基板の製造方法

【課題】 品質及び特性の優れた半導体装置の形成が可能な半導体基板を製造する。

【解決手段】 半導体基板の表面に酸化膜を形成する工程と、前記表面を前記酸化膜が覆っている状態で前記半導体基板に炭素を5×1013〜5×1015cm-2のドーズ量でイオン注入する工程と、前記表面を前記酸化膜が覆っている状態で前記イオン注入後に前記半導体基板をアニールする工程と、前記アニール後に前記表面上にエピタキシャル層を形成する工程とを有する。このため、不純物及び結晶欠陥を炭素によって強力にゲッタリングすることができる半導体基板を製造することができる。

(もっと読む)

1 - 20 / 28

[ Back to top ]