Fターム[4G077TC12]の内容

結晶、結晶のための後処理 (61,211) | 製造工程 (1,363) | 複数の工程からなるもの (584) | 複数の成長工程 (370)

Fターム[4G077TC12]の下位に属するFターム

二層 (176)

三層以上 (146)

基板の移動をともなう (5)

Fターム[4G077TC12]に分類される特許

1 - 20 / 43

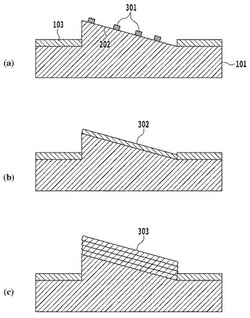

窒化物半導体薄膜およびその成長方法

【課題】従来よりも原子レベルで平坦な表面を有する窒化物半導体薄膜及びその成長方法を提供する。

【解決手段】ミスカットを有するGaN基板101のステップフロー成長(工程1)により制限領域内に形成されたテラス202に、工程1よりもキャリアガスに含まれる水素の組成を少なくして、トリメチルガリウム(TMG)又はトリエチルガリウム(TEG)を供給し、テラス202の上にGaNの2次元核301を1個以上100個以下発生させる(工程2)。次に、工程2よりもキャリアガスに含まれる水素の組成を多くする(工程3)。これにより、複数の2次元核301が横方向成長して1分子層の厚さの連続的なGaN薄膜302となる。工程2と工程3を交互に繰り返すことにより、2分子層以上の厚さのGaN薄膜303を成長させる。

(もっと読む)

基板上に堆積された窒化ガリウムフィルムにおける応力の制御方法

【課題】シリコンおよび炭化ケイ素基板上に堆積されたGaNフィルムにおける応力の制御方法、およびこれによって生成されたGaNフィルムを提供する。

【解決手段】典型的な方法は、基板を供給すること、および供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上にグレーデッド窒化ガリウム層を堆積させることを含む。典型的な半導体フィルムは、基板と、供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上に堆積されたグレーデッド窒化ガリウム層とを含む。

(もっと読む)

III族窒化物半導体素子製造用基板およびIII族窒化物半導体自立基板またはIII族窒化物半導体素子の製造方法ならびにIII族窒化物成長用基板

【課題】結晶層の結晶性や均一性を向上させることができるIII族窒化物半導体素子製造用基板の製造方法を提供する。

【解決手段】成長用下地基板10上に、クロム層20を形成する成膜工程と、該クロム層20を、所定の条件で窒化することによりクロム窒化物層30とする窒化工程と、該クロム窒化物層30上に、バッファ層40を介して、少なくとも1層のIII族窒化物半導体層50をエピタキシャル成長させる結晶層成長工程とを具えるIII族窒化物半導体素子製造用基板90の製造方法であって、前記クロム層20は、スパッタリング法により、スパッタリング粒子飛程領域における成膜速度が7〜65Å/秒の範囲で、厚さが50〜300Åの範囲となるよう成膜され、前記クロム窒化物層30は、炉内圧力6.666kPa以上66.66kPa以下の、温度1000℃以上のMOCVD成長炉内において、アンモニアガスを含むガス雰囲気中で形成される。

(もっと読む)

結晶成長方法および半導体素子

【課題】転位およびクラックの発生、並びに、基板の反りを抑制することが可能な結晶成長方法を提供する。

【解決手段】このIII族窒化物半導体の結晶成長方法は、シリコン基板100を加熱する工程と、加熱されたシリコン基板100に対して、少なくともTMA(トリメチルアルミニウム)を含むガスを先出し供給することにより、基板表面に凹状構造105を形成する工程とを備えている。

(もっと読む)

ホモエピタキシャルIII−V族窒化物品、デバイス、およびIII−V族窒化物ホモエピタキシャル層を形成する方法

【課題】LEDや高電子移動度トランジスタなどのデバイス用として有用なIII−V族窒化物品の提供。

【解決手段】自立III−V族窒化物基板上に堆積したIII−V族窒化物ホモエピタキシャル層を含むホモエピタキシャルIII−V族窒化物品であって、前記III−V族窒化物ホモエピタキシャル層が1E6/cm2未満の転位密度を有しており、(i)前記III−V族窒化物ホモエピタキシャル層と前記自立III−V族窒化物基板の間に酸化物を有するか、(ii)前記III−V族窒化物ホモエピタキシャル層と前記自立III−V族窒化物基板の間にエピ中間層を有するか、

(iii)前記自立III−V族窒化物基板がオフカットされており、前記III−V族窒化物ホモエピタキシャル層が非(0001)ホモエピタキシャルステップフロー成長結晶を含むことを特徴とする。

(もっと読む)

窒化アルミニウム単結晶層を有する積層体の製造方法、該製法で製造される積層体、該積層体を用いた窒化アルミニウム単結晶基板の製造方法、および、窒化アルミニウム単結晶基板

【課題】高品質の窒化アルミニウム単結晶自立基板を効率良く製造できる方法を提供する。

【解決手段】シリコン単結晶等からなるベース基板11を準備する工程、準備した前記ベース基板11の単結晶面上に厚さ10nm〜1.5μmの窒化アルミニウム単結晶層12を形成する薄膜エピタキシャル成長工程、前記工程で得られた窒化アルミニウム単結晶層12の上に、窒素含有量が前記窒化アルミニウム単結晶層よりも少ない窒化アルミニウム多結晶層13を形成する多結晶層成長工程、及び前記工程で得られた積層基板から前記ベース基板11を除去するベース基板除去工程を含んでなる、積層体14の製造工程の後、第二の窒化アルミニウム単結晶15を層状に成長させる工程、さらに該窒化アルミニウム単結晶層15の少なくとも一部を分離して、自立基板として使用可能な窒化アルミニウム単結晶基板16を得る工程を含む、窒化アルミニウム単結晶自立基板の製造方法。

(もっと読む)

III族窒化物半導体層の製造方法

【課題】反りの発生を低減させることができるIII族窒化物半導体層の製造方法を提供すること。

【解決手段】III族窒化物半導体層の製造方法は、下地基板10上に、炭化チタン、炭化ジルコニウム、炭化ハフニウム、炭化バナジウムまたは炭化タンタルから選択されるいずれかの炭化物層11を形成する工程と、炭化物層11の上部にIII族窒化物半導体層12を成長させる工程と、III族窒化物半導体層12中で亀裂を生じさせて、前記下地基板10を除去し、III族窒化物半導体層を得る工程とを含む

(もっと読む)

半導体素子の製造方法

【課題】ELOG法を用いて形成された開口面積の大きい空洞を半導体層内部に導入することにより成長用基板をウェットエッチング処理または外力印加によって容易に剥離することができる半導体素子の製造方法を提供する。

【解決手段】

成長用基板上を部分的に覆う選択成長用のマスクを成長用基板上に形成する。次に、成長用基板上のマスクで覆われていない非マスク部において、マスクの膜厚よりも厚い緩衝層を成長させた後、緩衝層の表面に所定のファセットを表出させる。次に、緩衝層を起点として半導体膜を横方向成長させてマスク上部に空洞を形成しつつマスクを覆う横方向成長層を形成する。横方向成長層の上にデバイス機能層をエピタキシャル成長させる。空洞形成工程は、互いに異なる成長速度で半導体膜の成長を行う第1ステップおよび第2ステップを交互に複数回実施する。

(もっと読む)

低欠陥密度の自立窒化ガリウム基板の製法およびそれにより製造されたデバイス

本発明は、成長面(105)を含む支持体(100)上でのエピタキシャル成長により窒化物単結晶を製造するための方法において、− 支持体(100)上に犠牲床(101)を形成するステップと;− 前記犠牲床上にピラー(102)を形成するステップであって、前記ピラーがGaNエピタキシャル成長と相容性のある材料で作られているステップと;− 窒化物結晶層(103)がピラーの間に形成されたホール(107)内を支持体に至るまで延在しないような成長条件の下で、ピラー上に窒化物結晶層(103)を成長させるステップと;− 支持体から窒化物結晶層を除去するステップと、を含む方法に関する。  (もっと読む)

(もっと読む)

窒化ガリウム系半導体電子デバイス、窒化ガリウム系半導体電子デバイスを作製する方法、エピタキシャル基板、及びエピタキシャル基板を作製する方法

【課題】1×1016cm−3以下のキャリア濃度の領域でキャリア補償の影響を低減可能なエピタキシャル基板を提供する。

【解決手段】エピタキシャル基板Eは、窒化ガリウム基板11及び窒化ガリウムエピタキシャル膜13を備える。窒化ガリウム基板11の主面11aにおいて、転位密度が1×108cm−2以下であるとき、窒化ガリウムエピタキシャル膜13中の電子トラップの密度が低減される。窒化ガリウム基板主面11aのオフ角が0.3度以上であるとき、窒化ガリウムエピタキシャル膜13は低い電子トラップの密度を有する。窒化ガリウムエピタキシャル膜13が1×1016cm−3以下のドナー濃度及び3×1015cm−3以下のアクセプタ濃度を有するので、窒化ガリウムエピタキシャル膜13における補償が低く、窒化ガリウムエピタキシャル膜に1×1016cm−3以下のキャリア濃度が提供される。

(もっと読む)

半導体材料を含む構造の品質を改善する方法

III−窒化物材料の半導体構造および層のエピタキシャル成長中に、連続する層の品質が連続して改善されるように応用可能な方法。中間エピタキシャル層は、成長ピットが、最初の表面に存在する表面転位で形成されるように、最初の表面に成長される。それから、次の層は、横方向に広がって少なくとも交差成長ピットの凝集を密閉するように、エピタキシャル横方向オーバーグロースの知られた現象に従って中間層上に成長される。好ましくは、横方向成長材料中の転位の数を減少させるために、次の層の成長より前に、誘電体材料が不連続に堆積するように誘電体材料の不連続膜が堆積される。本発明の方法は、同じ構造に対して複数回行うことができる。また、これらの方法によって製作された半導体構造。  (もっと読む)

(もっと読む)

窒化物系半導体基板及び半導体装置

【課題】充分な導電性を確保しつつ、高い熱伝導率と高い電子移動度を有する窒化物系半導体基板及び半導体装置を提供する。

【解決手段】直径25mm以上、かつ厚さ250μm以上の寸法を有する窒化物系半導体からなる基板であって、n型のキャリア濃度n[cm-3]が1.2×1018cm-3以上3×1019cm-3以下であり、かつ電子移動度μ[cm2/Vs]が、logeμ=17.7−0.288logenで表される値よりも大きく、かつlogeμ=18.5−0.288logenで表される値よりも小さい窒化物系半導体基板。また、その窒化物系半導体基板の上に窒化物系半導体をエピタキシャル成長させて半導体装置とする。

(もっと読む)

窒化物薄膜構造及びその形成方法

本発明は、窒化物薄膜構造及びその形成方法に関する。窒化物ではない基板上に窒化物薄膜を形成すれば、基板と窒化物薄膜との格子定数差によって多くの欠陥が生じる。また基板と窒化物薄膜との熱膨張係数差によって基板が反るという問題がある。本発明ではかかる問題を解決するために、中の空いている粒子、すなわち、中空構造物を基板上に塗布した後、その上に窒化物薄膜を成長させた薄膜構造及びその形成方法を提案する。本発明によれば、中空構造物によるELO(Epitaxial Lateral Overgrowth)効果を得ることができて高品質の窒化物薄膜を形成でき、薄膜構造内の屈折率が調節されることによって、本発明による薄膜構造をLEDのような発光素子で製作する時、光抽出効率が増大するという効果がある。それだけでなく、基板の熱膨張係数が窒化物薄膜に比べてさらに大きい場合には、窒化物薄膜内の中空構造物の圧縮によって窒化物薄膜の全体応力が低減して基板の反りを防止する効果もある。  (もっと読む)

(もっと読む)

積層体、自立基板製造用基板、自立基板およびこれらの製造方法

【課題】Al系III族窒化物単結晶自立基板を製造するためのベース基板として好適に使用できる、結晶レベルでの歪みが低減されており、クラックおよび反りの発生が抑制された自立基板製造用基板を提供する。

【解決手段】不活性ガス中1000℃において分解しない無機物質であって、1000℃以上1600℃以下で還元性ガスと接触することにより分解して揮発性物質を生成する無機物質の単結晶からなるベース基板、ベース基板上に形成された、単結晶Al系III族窒化物、または単結晶Al系III族窒化物と非晶質Al系III族窒化物との混合物からなる厚さ3nm以上200nm以下のAl系III族窒化物薄膜層、Al系III族窒化物薄膜層上に形成された、Al系III族窒化物薄膜層の厚さの100倍以上の厚さを備えたIII族窒化物非単結晶層、を備えて構成される積層体とし、ベース基板とAl系III族窒化物薄膜層との界面に複数の空隙を設ける。

(もっと読む)

ダイヤモンド単結晶基板の製造方法及びダイヤモンド単結晶基板

【課題】半導体材料、電子部品、光学部品、切削・耐磨工具などに用いられる大面積で高品質なダイヤモンド単結晶基板を高速に製造する方法を提供する。

【解決手段】種基板1として、主面の面方位が略<100>方向に揃った複数個のダイヤモンド単結晶基板を並べて配置し、気相合成法により種基板1上にダイヤモンド単結晶を成長させるダイヤモンド単結晶基板の製造方法であって、種基板1の主面の面方位が{100}面に対する傾きが5度以下であり、第一の段階における成長パラメータαが2.0以上3.0未満であり、第二の段階におけるαが3.0以上である。

(もっと読む)

GaN基板の製造方法、エピウエハの製造方法、半導体素子の製造方法およびエピウエハ

【課題】エピウエハを形成した場合に要求される反り以下になり、かつコストを低減できるGaN基板の製造方法、エピウエハの製造方法、半導体素子の製造方法およびエピウエハを提供する。

【解決手段】GaN基板10の半径をr(m)、厚みをt1(m)、エピウエハ20が形成される前のGaN基板の反りをh1(m)、AlxGa(1-x)N層21の厚みをt2m、エピウエハの反りをh2m、GaNの格子定数をa1、AlNの格子定数をa2としたときに、(1.5×1011×t13+1.2×1011×t23)×{1/(1.5×1011×t1)+1/(1.2×1011×t2)}/{15.96×x×(1−a2/a1)}×(t1+t2)+(t1×t2)/{5.32×x×(1−a2/a1)}−(r2+h2)/2h=0により求められるt1の値をGaN基板の最小厚みとし、この最小厚み以上400μm未満の厚みのGaN基板が形成される。

(もっと読む)

III−V族窒化物半導体基板及びIII−V族窒化物半導体基板の製造方法

【課題】粗研磨を実施したときのクラックの発生率を低下することができるIII−V族窒化物半導体基板及びIII−V族窒化物半導体基板の製造方法を提供する。

【解決手段】本発明に係るIII−V族窒化物半導体基板は、異種基板上にファセット面で成長したIII−V族窒化物半導体結晶の第1の領域と、異種基板上に所定の面方位で成長したIII−V族窒化物半導体結晶の第2の領域とを有し、第1の領域は、第2の領域に対して10%以下の面積比を有する。

(もっと読む)

改善されたエピタキシャル材料を製造するための方法

本発明は、小さい欠陥密度を有するIII族窒化物半導体材料からなる実質的に連続的な層を製造するための方法を提供する。この方法は、ベース基板上において核形成層をエピタキシャル成長させ、この核形成層を熱処理し、不連続なマスク層をエピタキシャル成長させることを含む。簡単に説明されるこの方法は、マスクし、消滅させ、および、融合させることによって欠陥を減少させることを促進し、それによって、小さい欠陥密度の半導体構造をもたらす。本発明は、広い範囲の半導体材料に適用されてもよく、元素半導体、例えば、ひずみSi(sSi)と組み合わせたSi(シリコン)、および/または、Ge(ゲルマニウム)、および、化合物半導体、例えば、II−VI族およびIII−V族の化合物半導体材料のいずれにも適用されてもよい。 (もっと読む)

エピタキシャル方法およびこの方法によって成長させられたテンプレート

本発明は、小さい欠陥密度を有しかつ選択された結晶極性をオプションとして有する、III族窒化物半導体材料からなる実質的に連続的な層を製造するための方法を提供する。この方法は、テンプレート構造上に不規則に配置されたIII族窒化物材料からなる複数のピラー/アイランドの上部にエピタキシャル成長の核形成および/または播種することを含む。アイランドの上部は、小さい欠陥密度を有し、また、選択された結晶極性をオプションとして有する。本発明は、また、マスク材料からなる実質的に連続的な層を有するテンプレート構造を含み、ピラー/アイランドの上部は、このマスク材料から突き出る。本発明は、広範囲の元素半導体材料および化合物半導体材料に適用されてもよい。 (もっと読む)

化合物半導体基板の製造方法

【課題】異種材料が埋め込まれた3−5族窒化物半導体を含む化合物半導体結晶を、厚さを大きくすることなしに結晶性よく基板上に成長させる、化合物半導体基板の製造方法を提供する。

【解決手段】成長基板11上に、成長基板11及び3−5族窒化物半導体を含む化合物半導体のいずれとも異なる異種材料が埋め込まれた窒化物半導体を含む窒化物半導体層13を設けて化合物半導体基板を製造する場合、異種材料としてタンタル、チタン、ジルコニウム、ハフニウム、ニオブ、プラチナ、バナジウム、パラジウム、またはそれらのいずれかを含む合金からなる金属材料を選択し、該金属材料による埋め込み部12Aを成長基板11上に形成し、埋め込み部12Aによって横方向成長を促進させつつ3−5族窒化物半導体を含む化合物半導体をエピタキシャル結晶成長させ、これにより、成長基板11の上に3−5族窒化物半導体を含む化合物半導体エピタキシャル結晶を積層する。

(もっと読む)

1 - 20 / 43

[ Back to top ]