Fターム[4K029BD02]の内容

Fターム[4K029BD02]に分類される特許

81 - 100 / 490

スパッタリング方法

【課題】 1μm以上の開口径を有する高アスペクト比のTSVホールHがパターニング形成された処理対象物に対して、被覆性よく成膜できるスパッタリング方法を提供する。

【解決手段】 真空チャンバ1内に処理対象物と、処理対象物に形成しようとする金属膜に応じて作製されたターゲット2とを対向配置し、処理対象物の全面に亘って垂直な磁場が作用するように垂直磁場を発生させ、この真空チャンバ内にスパッタガスを導入し、ターゲットに所定の電力を投入して真空チャンバ内にプラズマを形成してターゲットをスパッタリングし、処理対象物に高周波バイアス電力を投入してターゲットからのスパッタ粒子やプラズマ中で電子で電離したイオンを引き込むようにしたものにおいて、前記バイアス電力を、200〜600Wの範囲とする。

(もっと読む)

高温半導体素子用平角状金被覆銅リボン

【課題】 半導体の素子パッドとニッケル(Ni)被覆基板側のリード間を多数箇所同時に接続するボンディングリボンにおいて、超音波接合性、高温信頼性を向上する。

【解決手段】 金被覆銅リボンを銅芯材と金被覆層で構成し、

銅芯材を70Hv以下のビッカース硬さをもつ純度99.9%以上の銅(Cu)として導電性とループ形成性を付与し、被覆層を純度99.9%以上の金(Au)をアルゴンガス(Ar)等の希ガス雰囲気下でマグネトロンスパッタすることによって、微細な粒状の結晶組織として、芯材と被覆層とのビッカース硬さを同等にして、アルミパッドの損傷を防止するとともに、接合性を向上する。

希ガス雰囲気中でマグネトロンスパッタした金微細結晶組織は、硬さが金(Au)バルクよりも高く、粒状組織としたことで接合時の熱広がりを抑制する。

(もっと読む)

スパッタ方法及びスパッタ装置

【課題】単一のスパッタ装置によって金属材料を凹部に埋め込む際にその埋め込み性を向上させることができるスパッタ方法及び該スパッタ方法に用いられるスパッタ装置を提供する。

【解決手段】

基板Sの凹部内に金属材料を埋め込むスパッタ方法では、基板Sにバイアス電圧を印加しつつターゲット18をスパッタする第1の工程と、基板Sにバイアス電圧を印加しない状態でターゲットをスパッタする第2の工程とを有し、第1の工程と第2の工程とは真空槽11内で順に実行される。第1の工程では、ターゲット18から放出された金属粒子とプラズマ中の荷電粒子とが衝突する圧力でターゲット18をスパッタして電荷を帯びた金属粒子を生成し、電荷を帯びた金属粒子を凹部の内部に向けてバイアス電圧により引き込む。第2の工程では、基板Sに付着する金属粒子が凹部内に流動するように基板Sの温度を第1の工程よりも高くしてターゲット18をスパッタする。

(もっと読む)

半導体装置の製造方法

【課題】余分な工程を追加することなく、コンタクト抵抗の増加を抑制する半導体装置を提供する。

【解決手段】半導体装置の製造方法では、Cu配線上の第2層間絶縁膜内に設けたコンタクトホール内に第1のTi膜、TiN膜、第2のTi膜、第1のAl膜、及び第2のAl膜をこの順に形成する。第1のTi膜を成膜する際には、コンタクトホール底面上の第1の部分と第2層間絶縁膜上の第2の部分の膜厚の比(第1の部分)/(第2の部分)を0.05以下とする。また、第2のAl膜はアルミ・リフロー法を用いて形成し、この際に第2のTi膜及び第1のAl膜をアルミニウム・チタン合金膜とする。

(もっと読む)

円筒型Mo合金ターゲットの製造方法

【課題】 効率的に高い接合強度で長尺の一体型のターゲットを実現可能な円筒型Mo合金ターゲットの製造方法を提供する。

【解決手段】 Mo粉末とMo以外の高融点金属粉末とからなる複数の円筒型成形体を端面で接合する円筒型Mo合金ターゲットの製造方法であって、一方の円筒型成形体の接合端面を5〜85度のテーパー状に形成し、他方の円筒型成形体の接合端面を前記テーパー状の端面に対して補角となるすり鉢状に形成し、前記円筒型成形体を、前記接合端面同士が当接するように中空の円筒型充填空間を有する金属カプセルに挿入した後、減圧封止し、その後、熱間静水圧プレスを施し、一体型の焼結体を得る円筒型Mo合金ターゲットの製造方法である。

(もっと読む)

成膜方法及びターゲット

【課題】スパッタリング法を用いて形成されるタングステン膜の比抵抗を低下させることができる成膜方法及びこの成膜方法の実施に用いられるタングステンターゲットを提供する。

【解決手段】

タングステンを含有するターゲットTを希ガスによりスパッタしてタングステン膜を基板Sに形成する成膜方法において、ターゲットTとしてニッケルを含有するものを用いることで、成膜されたタングステン膜はニッケル酸化物を含有する。また、成膜されたタングステン膜におけるニッケルの濃度が、0.001質量%以上且つ1質量%以下となるようにする。

(もっと読む)

薄膜の形成方法

【課題】埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させることが可能な薄膜の形成方法を提供する。

【解決手段】表面に凹部8を有する被処理体Wの表面に薄膜を形成する形成方法において、被処理体の表面に埋め込み用の金属膜16して凹部を埋め込む埋め込み工程と、金属膜を覆うようにして被処理体の表面の全面に拡散防止用の金属膜18を形成する拡散防止膜形成工程と、被処理体をアニールするアニール工程とを有する。これにより、埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、スパッタ装置の処理能力を損なうことなく、スパッタに異常がないときは金属薄膜の反射率を面内で均一にすることができる半導体装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、シリコン基板にスパッタ成長により金属膜を形成する第1スパッタ工程と、該第1スパッタ工程の後に該第1スパッタ工程よりも高いDCパワーでさらに金属膜をスパッタ成長させる第2スパッタ工程と、該第1スパッタ工程と該第2スパッタ工程の後に、該第1スパッタ工程および該第2スパッタ工程で形成された金属膜の反射率の均一性を測定する検査工程とを備えたことを特徴とする。

(もっと読む)

表示装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置用Al合金膜である。

(1)Alと、X群から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含む第1の析出物について、円相当直径20nm以上の析出物が500,000個/mm2以上の密度で存在する。

(もっと読む)

半導体製造装置、ターゲットの表面処理方法、及びプログラム

【課題】ターゲットの表面の状態に応じてバーンインの最適化を図ることができる半導体製造装置、ターゲットの表面処理方法、及びプログラムを提供する。

【解決手段】本発明の一態様に係るスパッタリング装置1は、半導体ウエハWが配置されるテーブル3、及びテーブル3に対向する位置に設けられたターゲット4を収容する処理容器2と、処理容器2内に放電ガスを供給するガス供給部10と、ターゲット4に電力を供給して放電させ、これによりプラズマを生成してイオン化した放電ガスでターゲットをエッチングするパルス電源部12と、プラズマの生成後の放電電圧を測定する電圧測定部13Aと、ターゲット4のエッチングの進行状況に起因する電圧測定部13Aによる測定値の変化に基づいて、ターゲット4のエッチングを終了させる制御を行う制御部14Aとを備える。

(もっと読む)

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

均一かつ微細結晶組織を有する高純度銅加工材及びその製造方法

【課題】スパッタリングターゲットとして用いるに好適な、均一かつ微細結晶組織を有する高純度銅加工材を提供する。

【解決手段】Cu純度99.9999重量%以上の高純度銅からなる鋳塊を、550℃以上で熱間鍛造した後急水冷し、次いで、初期温度350℃以上で温間鍛造した後急水冷し、次いで、50%以上の総圧下率で冷間クロス圧延をし、次いで、200℃以上で歪取焼鈍を行うことにより、平均結晶粒径が20μm以下であり、かつ、個々の結晶粒についてその粒径分布を測定した場合に、平均結晶粒径の2.5倍を超える粒径の結晶粒が占める面積割合は、全結晶粒面積の10%未満である均一かつ微細な結晶組織を有する高純度銅加工材。

(もっと読む)

パターン形成用マスク及び該マスクを用いた成膜装置

【課題】従来の高温・低温・真空・ガス雰囲気中などの様々なマスク使用環境下で、格子状や環状などの所定のパターンの形成を、単独のマスクを用いて1回の成膜で行うことができるパターン形成用マスク、及び該マスクを用いた成膜装置の提供。

【解決手段】成膜装置に用いるパターン形成用マスクであって、膜形成材料側の面をMO面、パターンが形成される基板側の面をMU面として、マスクの開口部の一部に、MU面に近い側の断面積がMO面に近い側の断面積よりも小さくなっている非開口部分を有し、かつ、MU面と該非開口部分のMU面に対向する端部との間に空間を有するパターン形成用マスク。

(もっと読む)

Al基合金スパッタリングターゲット

【課題】Al基合金スパッタリングターゲットを用いた場合に、高速成膜してもスプラッシュの発生を抑制し得る技術を提供すること。

【解決手段】Ni−希土類元素−Al基合金スパッタリングターゲットの表層部、1/4×t部、1/2×t部の各スパッタリング面法線方向の結晶方位<001>、<011>、<111>、<012>および<112>を観察したとき、下記(1)、(2)の要件を満足することを特徴とする。

(1)前記<001>、<011>、および<112>の±15°の合計面積率をRとしたとき、Rが、0.35以上、0.8以下であり、かつ

(2)Ra、Rb、Rcが、R平均値[Rave=(Ra+Rb+Rc)/3]の±20%の範囲内にある。

(もっと読む)

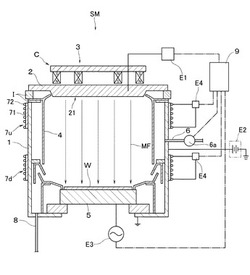

金属薄膜の形成方法

【課題】スパッタリングによる成膜レートを低くし、被処理体の表面に形成されたアスペクト比が3以上の孔または溝の内壁面および内底面に被覆性が良好な金属薄膜を形成し、少ない電力でも、ターゲットにおける自己保持放電を発生させる成膜方法を提供する。

【解決手段】ターゲット3に電圧Vおよび電流Iを印加しチャンバ2内でターゲットから放電が発生した後、スパッタガスの導入を止めてターゲットのイオンにより自己保持放電を発生させ、被処理体Wの表面の孔または溝内を含む被処理体の表面全面に金属薄膜を形成する工程において、ターゲットに印加する電流Iを一定とし、放電が不安定になった時に電圧Vを増大させるとともに、関係式(1)および(2)を満たすことを特徴とする。I>I0・・・(1)、P>P0・・・(2)(I0:自己保持放電を開始する電流の最小値、P:ターゲットの電力、P0:自己保持放電を開始する電力の最小値)

(もっと読む)

スパッタリング用ターゲットおよび半導体装置の製造方法

【課題】スパッタリング用ターゲットから垂直方向に叩き出されるターゲット原子の個数を増大させる。

【解決手段】薄膜形成に用いられるターゲット原子Pから構成されたターゲット5において、ターゲット5から斜め方向に叩き出されたターゲット原子Pを側壁に衝突させることでターゲット原子Pがターゲット5から放出されるのを遮る凹部5aを表面に形成する。

(もっと読む)

純銅板の製造方法及び純銅板

【課題】熱間鍛造や熱間圧延後の、冷間鍛造や冷間圧延、及び、その後の熱処理が不要な純銅板の製造方法、及び、その製造方法により得られた微細な組織を有すると共に部分再結晶化によって双晶組織を形成させる事により、高い特殊粒界比率を付与した、特に、スパッタリング用銅ターゲット素材やめっき用アノード等に適した純銅板を提供する。

【解決手段】純度が99.96wt%以上である純銅のインゴットを、550℃〜800℃に加熱して、総圧延率が85%以上で圧延終了時温度が500〜700℃であり、かつ、1パス当たりの圧下率が5〜24%の仕上げ圧延を1パス以上有する熱間圧延加工を施した後に、必要に応じて圧延終了時温度から200℃以下の温度になるまで200〜1000℃/minの冷却速度にて急冷する。

(もっと読む)

純銅板の製造方法及び純銅板

【課題】微細で均質な組織を有し、加工性が良好で、特に、重切削での加工を可能にした純銅板を得る。

【解決手段】純度が99.96wt%以上である純銅のインゴットを、550℃〜800℃に加熱して、総圧延率が80%以上で圧延終了時温度が500〜700℃である熱間圧延加工を施した後に、前記圧延終了時温度から200℃以下の温度になるまで200〜1000℃/minの冷却速度にて急冷し、その後、25〜60%の圧延率で冷間圧延して焼鈍する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

積層回路材料

【課題】特性インピーダンスを小さくできるために、超高周波又は超高速信号の伝送時においても反射や放射が少なく、かつ低損失である回路材料を提供する。

【解決手段】単一元素からなる原子層が単層若しくは複数層で構成する導体層と、導体層を構成する元素同士間の原子間結合よりもより安定な結合を形成する単一又は復数の元素からなる原子層が単層若しくは複数層で構成する拘束層とからなり、前記導体層と拘束層の原子同士が原子的整合状態(ヘテロ構造)で積層することを特徴とする回路材料の電気抵抗低下方法。

(もっと読む)

81 - 100 / 490

[ Back to top ]