Fターム[4K029DC34]の内容

物理蒸着 (93,067) | スパッタリング装置 (13,207) | スパッタ方式 (5,546) | 放電プラズマによるもの (2,861) | 電源 (2,524) | 直流 (1,517)

Fターム[4K029DC34]に分類される特許

41 - 60 / 1,517

Cu−Mn合金スパッタリングターゲット材、それを用いた薄膜トランジスタ配線及び薄膜トランジスタ

【課題】高いバリア性を有するCu−Mn合金膜を形成する。

【解決手段】半導体素子の配線の形成に用いられるCu−Mn合金スパッタリングターゲット材10であって、濃度が8原子%以上30原子%以下のMnと、不可避的不純物とを含むCu−Mn合金からなり、Cu−Mn合金の平均結晶粒径が10μm以上50μm以下である。

(もっと読む)

酸化物焼結体および酸化物透明導電膜

【課題】150℃以下の低い基板温度の成膜によっても、比抵抗が5×10-3Ω・cm以下、可視波長(400nm〜800nm)において98%以上の高い透過率を有する結晶性の透明導電膜を提供する。

【解決手段】Sn/Inが0.019〜0.102であり、かつ、In/(In+Sn+Co)が0.771〜0.967、Sn/(In+Sn+Co)が0.016〜0.091、Co/(In+Sn+Co)が0.015〜0.15であり、相対密度が98%以上、比抵抗が5×10-3Ω・cm以下である酸化物焼結体をスパッタリングターゲットとして成膜して透明導電膜を得る。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】高い移動度を実現でき、且つ、ストレス耐性(ストレス印加前後のしきい値電圧シフト量が少ないこと)にも優れた薄膜トランジスタ用酸化物を提供する。

【解決手段】本発明に係る薄膜トランジスタの半導体層用酸化物は、Zn、Sn、およびInと;Si、Hf、Ga、Al、Ni、Ge、Ta、W、およびNbよりなるX群から選択される少なくとも一種の元素(X群元素)と、を含むものである。

(もっと読む)

スパッタリングターゲット

【課題】高密度かつ低抵抗のスパッタリングターゲット、電界効果移動度の高い薄膜トランジスタを提供する。

【解決手段】Gaをドープした酸化インジウム、又はAlをドープした酸化インジウムを含み、正4価の原子価を示す金属を、Gaとインジウムの合計又はAlとインジウムの合計に対して100原子ppm超1100原子ppm以下含み、結晶構造が、実質的に酸化インジウムのビックスバイト構造からなる焼結体を含むスパッタリングターゲット。

(もっと読む)

Zn−Si−O系酸化物焼結体とその製造方法および透明導電膜

【課題】スパッタリングターゲットに利用された場合には異常放電等が抑制され、蒸着用タブレットに利用された場合にはスプラッシュ現象が抑制されるZn-Si-O系酸化物焼結体とその製法等を提供する。

【解決手段】酸化亜鉛を主成分とし、Siを含有するZn-Si-O系酸化物焼結体であって、Siの含有量が、Si/(Zn + Si)原子数比で0.1〜10原子%であり、Si元素がウルツ鉱型酸化亜鉛相に固溶していると共に、SiO2相および珪酸亜鉛(Zn2SiO4)であるスピネル型複合酸化物相を含有していないことを特徴とする。上記焼結体の製法は、原料粉末であるZnO粉末とSiO2粉末から得られた造粒粉を成形し、その成形体を焼成して上記焼結体を製造する際、700〜900℃の温度域を昇温速度5℃/分以上の速さで昇温させる工程と、成形体を焼成炉内において900℃〜1400℃で焼成する工程を有することを特徴とする。

(もっと読む)

ZnO焼結体の製造方法

【課題】膜特性の均一性に優れた透明導電膜作製用のZnO焼結体の製造方法を提供する。

【解決手段】ZnO焼結体は、ZnO粉末とB2O3粉末とを混合、焼成及び粉砕してZn4B6O13粉末を得る工程と、平均粒径が0.5〜1μmのZnO粉末と平均粒径が0.2〜0.5μmのZn4B6O13粉末とを混合、成形、焼成してZnO焼結体を得る工程とを含む方法により製造される。

(もっと読む)

純すずターゲット材料がマグネトロンスパッタ法を利用したフッ素ドープ酸化すず薄膜の製造方法

【課題】純すずターゲット材料がマグネトロンスパッタ法を利用したフッ素ドープ酸化すず薄膜の製造方法を提供する。

【解決手段】高純度すずをマグネトロンスパッタリングのターゲット材料として、マグネトロンスパッタの生産プロセスにおいて、反応ガス四フッ化炭素(CF4)と酸素(O2)を導入する。四フッ化炭素(CF4)は、作業ガスによって励起されるプラズマがフッ化物(F)イオンとフッ化物(F)励起状態原子を分離し、すずターゲット材料と合わせて、基板上にフッ素ドープ酸化すず薄膜を形成することにより、生産コストを軽減でき、フッ素ドープ酸化すず薄膜の品質を向上できる。

(もっと読む)

内燃機関用摺動部品、内燃機関、輸送機器および内燃機関用摺動部品の製造方法

【課題】チタンまたはチタン合金製の摺動部品の表面に設けられるDLC膜の密着性を向上させ、優れた耐衝撃性を実現する。

【解決手段】本発明による内燃機関用摺動部品は、チタンまたはチタン合金から形成された部品本体1aと、部品本体1aの表面に形成された表面硬化層1bと、表面硬化層1b上に設けられたダイヤモンドライクカーボン膜3と、表面硬化層1bとダイヤモンドライクカーボン膜3との間に設けられたチタン層2とを有する。表面硬化層1bは、チタン酸化物層である。

(もっと読む)

成膜方法

【課題】成膜用ワークの形状、構造に拘わらず、成膜室に搬入すると、直ちに成膜動作に入ることができる成膜方法を提供する。

【解決手段】成膜用ワーク(W)を射出成形するときに、該成膜用ワークを成膜室(11)内に搬入して成膜台(12)に載置すると、その成膜面あるいは成膜部(A’、B’、C’)がターゲット材料(14)と対面する所定姿勢に保持するアシスト部材(1、2)を成膜用ワーク(W)と一体的に成形し、これを成膜室(11)に搬入して成膜する。

(もっと読む)

複合体

【課題】導電性が高くIII族窒化物結晶との接合強度が高いとともに光透過性が高い複合体を提供する。

【解決手段】本複合体100は、III族窒化物結晶110とIII族窒化物結晶110上に配置された酸化物膜120とを含み、酸化物膜120はドーパントの濃度が互いに異なる第1領域121と第2領域122とを含み、第2領域122は第1領域121に比べてドーパントの濃度が高い。

(もっと読む)

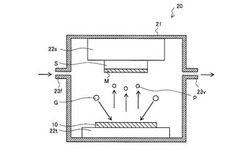

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】金属カルコゲナイド膜の積層体を有する相変化メモリにおいて、読み書き動作の速度を高めることのできる相変化メモリの形成装置、及び相変化メモリの形成方法を提供する。

【解決手段】GeTe膜とSbTe膜とを基板上にて交互に積層することによって相変化メモリを形成する際に、処理基板Sの温度を250℃以上350℃以下の所定温度に維持する。加えて、互いに異なる組成を有する二つのターゲットであるGeTeターゲット22aとSb2Te3ターゲット22bの各々を互いに異なるタイミングでアルゴンガスによりスパッタする。このとき、互いに異なる組成を有した二つ以上の金属カルコゲナイド膜であるGeTe膜とSb2Te3膜とを毎秒3nm以上10nm以下の速度で前記基板上に積層する。

(もっと読む)

両面真空成膜方法、及び該方法によって得られる積層体

【課題】単純な装置構成を用いて適宜に加熱処理等を施すことにより、両面に真空成膜が施された積層体を効率的に製造できる成膜方法を提供する。

【解決手段】ロール状に巻かれた長尺の基体を第1ロール室W1から第2ロール室W2へ向う第1の方向に第1ロール室から繰り出し、繰り出された基体10を脱ガスし、第1の面に第1成膜室41において第1の膜材料を成膜し、第1の膜材料が成膜された基体を、第2ロール室から第1ロール室へ向う第2の方向で第2成膜室42へ案内し、第2の方向に案内中の基体の第1の面とは反対側の第2の面に第2成膜室において第2の膜材料を成膜し、第1の面に第1の膜材料が成膜され且つ第2の面に第2の膜材料が成膜された基体を第1ロール室と第2ロール室の間に設けた第3ロール室W3でロール状に巻取り、第3ロール室で巻き取った基体を第1の方向に第1ロール室から繰り出し、上記全ての処理を繰り返す。

(もっと読む)

炭素薄膜成膜方法

【課題】水素フリーで緻密で硬質なダイヤモンドライクカーボン膜を容易に形成することができる炭素薄膜成膜法を提供する。

【解決手段】この炭素被膜成膜方法は、マグネトロンスパッタ法により試料基板電極上に配置された試料基板表面に炭素被膜を堆積させる炭素被膜成膜装置を用い、炭素ターゲット基板電極と試料電極に対し、下記1〜4の条件でそれぞれ電圧を印加させることを特徴とする。

1.ターゲット基板電極に印加する電圧が負のパルス電圧であって、かつ、そのパルス電圧時間比が40%以下であること。

2.ターゲット基板電極に印加するパルス電圧のパルス時間が20μs〜200μsであること。

3.試料基板電極に印加する電圧が負のパルス電圧であって、かつ、そのパルス電圧時間比が50%以下であること。

4.試料基板電極に印加する負パルス電圧の大きさが−20V〜−200Vであること。

(もっと読む)

透明導電膜の製造方法、反射膜の製造方法、液晶表示装置の製造方法、液晶表示装置、イメージセンサの製造方法、タッチパネルの製造方法、及び太陽電池の製造方法

【課題】透明導電膜の形成方法に依らずに、その表面に凹凸を形成することが可能な透明導電膜の製造方法を提供する。

【解決手段】本発明の透明導電膜の製造方法は、酸化物からなる透明導電膜を形成し、透明導電膜を水素含有ガスの還元雰囲気に晒すことで、透明導電膜の表面に凹凸を形成する、ことを特徴とする。

(もっと読む)

両面真空成膜方法、及び該方法によって得られる積層体

【課題】単純な装置構成を用いて適宜に加熱処理等を施すことにより、両面に真空成膜が施された積層体を効率的に製造できる成膜方法を提供すること等。

【解決手段】ロール状に巻かれた長尺の基体を第1の面を被成膜面として第1ロール室から第2ロール室へ向う方向に第1ロール室から繰り出し、繰り出された基体を脱ガスし、脱ガスされた基体の第1の面に第1成膜室において第1の膜材料を成膜し、第1の膜材料の上に第2成膜室において第2の膜材料を成膜し、膜材料が積層された基体を第2ロール室でロール状に巻取り、巻き取った基体を第1の面とは反対側の第2の面を被成膜面として方向に第1ロール室から繰り出し、上記全ての処理を繰り返す。

(もっと読む)

透明導電性フィルムおよびその製造方法

【課題】可撓性透明基材上に結晶性の透明導電体層を有する透明導電性フィルムにおいて、透明導電体層がパターン化された場合であっても、タッチパネル等に組み込んだ際に、パターン開口部とパターン形成部との境界が視認されることによる見栄えの低下を抑制する。

【解決手段】可撓性透明基材の一方の面に結晶性導電性金属酸化物からなる透明導電体層が形成された透明導電性フィルムであって、可撓性透明基材の厚みは80μm以下である。本発明の透明導電性フィルムは、140℃で30分加熱した際の寸法変化率H1と、透明導電性フィルムから透明導電体層をエッチングにより除去したものを140℃で30分加熱した際の寸法変化率H2との差H1−H2が−0.02%〜0.043%である。そのため、タッチパネル等に組み込んだ際のパターン境界での段差が低減され、見栄えの低下が抑制される。

(もっと読む)

透明導電性フィルムの製造方法

【課題】透明導電体層がパターン化されている透明導電性フィルムにおいて、基材の厚みを80μm以下と小さくした場合でも、透明導電体層のパターン境界が視認されることによる、見栄えの低下を抑止する。

【解決手段】本発明の製造方法は、可撓性透明基材上にパターン化されていない透明導電体層が形成された積層体を準備する積層体準備工程、透明導電体層の一部を除去して可撓性透明基材上に透明導電体層を有するパターン形成部と可撓性透明基材上に透明導電体層を有していないパターン開口部とにパターン化するパターン化工程、および透明導電体層がパターン化された後の前記積層体を加熱する熱処理工程、を有する。熱処理工程における、パターン形成部の寸法変化率H1とパターン開口部の寸法変化率H2との差H1−H2の絶対値は0.03%未満であることが好ましい。

(もっと読む)

透明導電膜及びその製造方法

【課題】本発明者が開発したマグネシウム・炭素系材料(Mg(OH)2・C)を用いた透明導電膜について、量産工程に適し、かつ、成膜後の経時変化を低減できる実用レベルの製造方法を実現する。

【解決手段】マグネシウムを含むターゲットと炭素を含むターゲットとを同時に用いてスパッタリングを行うことにより、基板上にマグネシウムと炭素と含む透明導電膜を成膜する成膜工程と、前記成膜した透明導電膜を水を含む雰囲気に保持する透明化工程と、表面材ターゲットを用いてスパッタリングを行うことにより、前記基板上に成膜した透明導電膜の膜面上に表面材薄層を形成する被覆工程とを実行する透明導電膜の製造方法。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】インジウム、チタン、及び亜鉛を含む酸化物半導体層をチャネル形成領域とするトランジスタ、及び該トランジスタを含む半導体装置を提供する。酸化物半導体層に接するバッファ層としては、チタン、アルミニウム、ガリウム、ジルコニウム、ハフニウム、又は希土類元素から選択された一以上の元素の酸化物を含む金属酸化層を適用することができる。

(もっと読む)

スパッタリング装置およびその成膜方法

【課題】被処理基板に対して成膜の初期段階から持続的に除電を行なうことによって、異常放電の発生を抑制することが可能なスパッタリング装置を得る。

【解決手段】スパッタリング処理によって被処理基板100に対して導電膜103を形成するスパッタリング装置は、処理室と、金属製のローラ基部3Lおよびローラ基部3Lの全周に設けられる樹脂材3Rを含む搬送ローラ3と、樹脂材3Rの表面を被覆しつつローラ基部3Lに電気的に導通された導電部3Sと、を備え、処理室内で被処理基板100に導電膜103を形成するとき、被処理基板100は、導電部3Sに当接して搬送ローラ3に搬送され、導電部3Sを通して除電されつつスパッタリング処理される。

(もっと読む)

41 - 60 / 1,517

[ Back to top ]