Fターム[4K029FA01]の内容

Fターム[4K029FA01]の下位に属するFターム

粗面化 (43)

平滑化 (18)

清浄化、クリーニング (462)

放電処理、プラズマ処理 (656)

加熱処理 (104)

樹脂下地層、アンダコート層の形成 (224)

Fターム[4K029FA01]に分類される特許

101 - 120 / 294

成膜方法及び太陽電池の製造方法

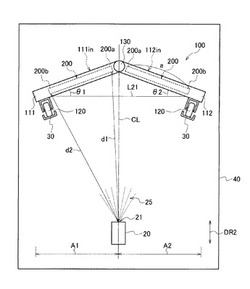

【課題】基板の表面にテクスチャが形成される場合でも、透明導電膜など、当該表面に形成される膜厚をより均一にすることができる成膜方法、及び太陽電池の製造方法を提供する。

【解決手段】幾何学的な凹凸が形成された基板200に蒸着源20から供給される蒸着材料25を蒸着させ、基板200の表面に透明導導電膜を形成する。蒸着源20の直上寄りに位置する基板200の端部200aと蒸着材料供給部21との距離d1、及び基板200の端部200bと蒸着材料供給部21との距離d2が略同一となるように、基板200を傾斜させた状態に位置させる。

(もっと読む)

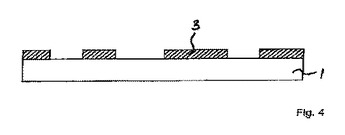

マスクブランク及びその製造方法

【課題】パターン形成用薄膜中のその周囲よりも多く酸素を含有する60nm以上150nm未満の大きさの高酸化物欠陥数を低減させ、高いレベルの欠陥品質を要求されるマスクブランクの製造方法を提供する。

【解決手段】透光性基板1上に金属及びケイ素のうち少なくともいずれかを含有する材料からなるパターン形成用薄膜2をスパッタ成膜装置を用いてスパッタリング法で形成することによりマスクブランク10を製造する。ここで、透光性基板1が搬入されるスパッタ成膜装置の室内の気体を水分および二酸化炭素を含有しない気体、ドライエアまたはこれらの混合気体に置換し終えた後に、該室内の減圧を行い、次いでパターン形成用薄膜2のスパッタリング法による成膜を開始する。

(もっと読む)

単結晶ダイヤモンド上にPZT薄膜を形成する方法、PZT薄膜が形成された単結晶ダイヤモンド、及びPZT薄膜が形成された単結晶ダイヤモンドを使用したキャパシタ

【課題】強誘電性を示すペロブスカイト構造のPZT(チタン酸ジルコン酸鉛)薄膜をダイヤモンド単結晶上に直接成長させることが困難なため、従来技術では、酸化物薄膜(例えばAl2O3/SrTiO3連続膜)を緩衝層として用いていたが、強誘電特性は不十分であった。

【解決手段】ダイヤモンド単結晶基板またはエピタキシャル薄膜上にフッ化物(CaF2、BaF2、MgF2の内一つ)を緩衝層として用いることにより、抗電界を同じ大きさ(33kV/cm)に保ちながら、従来の2倍の残留分極電荷(68μC/cm2)を持つ優れた強誘電性のPZT薄膜を提供する。更に、p型ダイヤモンド(13)/フッ化物(14)/PZT(15)/金属(16)構造からなるキャパシタを提供する。

(もっと読む)

酸化物半導体を用いた薄膜トランジスタおよびその製造方法

【課題】オフ特性およびキャリア移動度に優れた、高品質の、酸化物半導体を用いた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、ドレイン電極と、ゲート電極と、ゲート絶縁膜と、酸化物半導体からなる活性層とを備えてなる。そして、活性層とソース電極の間および活性層とドレイン電極の間には、炭素製のバッファ層が設けられてなる。

(もっと読む)

スパッタリングターゲット及びそれを用いた薄膜トランジスタ

【課題】Gaの含有量がInの含有量に比べ低い領域において、単一の結晶構造を主成分として有するスパッタリングターゲットに使用できる焼結体を提供する。

【解決手段】In、Ga、Znを0.28≦Zn/(In+Zn+Ga)≦0.38、0.18≦Ga/(In+Zn+Ga)≦0.28の原子比で含む酸化物であって、InGaO3(ZnO)で表されるホモロガス結晶構造を有する化合物を主成分とする酸化物からなる焼結体。

(もっと読む)

長期成膜時の安定性に優れたIn−Ga−Zn−O系酸化物焼結体スパッタリングターゲット

【課題】長期に渡る成膜を行った際に、得られる薄膜の特性の安定性に優れたスパッタリングターゲットを提供する。

【解決手段】In、Zn、及びGaを含み、表面と内部の化合物の結晶型が実質的に同一である酸化物焼結体からなり、下記(a)〜(e)の工程で製作されたスパッタリングターゲット。(a)原料化合物粉末を混合し、調製(b)混合物6.0mm以上に成形(c)3℃/分以下で昇温(d)1280〜1520℃で2〜96時間(e)表面を0.25mm以上研削

(もっと読む)

機能性フィルム及びその製造方法

【課題】真空成膜法によりコーティング膜上に無機膜を形成するときに、無機膜の割れ/抜け等の欠陥が発生するのを抑制でき、さらに生産性の高い機能性フィルム及びその製造方法を提供する。

【解決手段】コーティング膜12を塗布・乾燥し硬膜した後に、コーティング膜層表面にラミネートフィルム82を挟みながら巻き取りフィルムロール42とし、このフィルムロール42を真空成膜装置22にセットして、無機膜の製膜前にラミネートフィルム82を剥離する。ここで、ラミネートフィルム82には、コーティング膜に対して0.01N/25mm以上0.06N/25mm以下の剥離力である粘着層を有する粘着フィルムを用いる。

(もっと読む)

成膜方法

【課題】基板上に膜を成膜する際に、マスクやレジスト膜を用いることなく、所望のパターンを有する膜を安価に得ることができる成膜方法を提供する。

【解決手段】本発明の成膜方法は、基材1の表面1aに撥液膜2を形成する工程と、この撥液膜2上に、インクジェット法により所定のパターンを有する複数種類の樹脂層5a〜5cを形成する工程と、これらの樹脂層5a〜5cに、CF4プラズマを用いて撥液性を示すフッ素イオンを打ち込むことにより撥液化処理7を施し付着エネルギーの異なる複数種類の樹脂層5a〜5cとする工程と、複数種類の樹脂層5a〜5cを含む基材の表面に膜材料を堆積し、これら複数種類の樹脂層それぞれの表面に、種類毎に異なる厚みの膜を形成する工程と、を有する。

(もっと読む)

成膜方法

【課題】基板上に膜を成膜する際に、マスクやレジスト膜を用いることなく、しかも、簡便な方法により、膜を安価に得ることができる成膜方法を提供する。

【解決手段】基材1の表面に撥液膜2を形成する工程と、この撥液膜上に、インクジェット法により、所定のパターンを有する樹脂層5を形成する工程と、樹脂層及び撥液膜に親液化処理を施す工程と、樹脂層のみに撥液化処理7を施す工程と、樹脂層を含む撥液膜上に蒸着材料8を堆積し、この蒸着材料を、樹脂層以外の撥液膜上に集合させ、この集合した蒸着材料を膜9とする工程と、を有する。

(もっと読む)

液体噴射ヘッド、アクチュエーター装置及び液体噴射装置

【課題】結晶成長時の揺らぎが小さく、変位特性のよい液体噴射ヘッド、これを用いた噴射特性のよい液体噴射装置、並びに変位特性のよいアクチュエーター装置を提供する。

【解決手段】液体を噴射するノズル開口に連通する液体流路が設けられた流路形成基板上に第一電極60と、圧電体層70と、第二電極80とからなる圧電素子300を備え、圧電体層70は、鉛(Pb)、チタン(Ti)及びジルコニウム(Zr)からなる圧電体膜71と、圧電体膜71間に設けられたニオブ(Nb)、鉛(Pb)、チタン(Ti)及びジルコニウム(Zr)を含有するニオブ含有膜72とからなる。

(もっと読む)

成膜方法

【課題】基板上に膜を成膜する際に、マスクやレジスト膜を用いることなく、所望のパターンを有する膜を安価に得ることができる成膜方法を提供する。

【解決手段】本発明の成膜方法は、基材1の表面1aに撥液膜2を形成する工程と、この撥液膜2上に、インクジェット法により所定のパターンを有する樹脂層5を形成する工程と、この樹脂層5に、CF4プラズマを用いて撥液性を示すフッ素イオンを打ち込むことによりフッ素化処理7を施す工程と、樹脂層5を含む撥液膜2上に蒸着材料を堆積し、この蒸着材料を、樹脂層の付着エネルギーが低くかつ所定のパターンを有する領域以外の撥液膜上に集合させ、この集合した蒸着材料を膜とする工程と、を有する。

(もっと読む)

硬質膜の成膜方法および硬質膜

【課題】摺動部材の摺動面に成膜する場合などにおいても十分な耐摩耗性を有するDLC膜およびその成膜方法を提供する。

【解決手段】基材2の表面に形成された中間層3と表面層4とからなる硬質膜1の成膜方法であって、該成膜方法は、基材2上に金属系材料を主体とする中間層3を形成する中間層形成工程と、中間層3の上にDLCを主体とする表面層4を形成する表面層形成工程とを有し、中間層形成工程および表面層形成工程において、中間層3および表面層4は、スパッタリングガスとしてArガスを用いたUBMS装置を使用し、上記表面層形成工程は、上記装置内の真空度が0.2〜0.9Paであり、基材2に印加するバイアス電圧が70〜400Vである条件下で、炭素供給源となるターゲットから生じる炭素原子を、中間層3上に堆積させてDLCを主体とする表面層4を形成する工程である。

(もっと読む)

多結晶薄膜、その成膜方法、及び薄膜トランジスタ

【課題】十分に結晶化された多結晶薄膜を提供する。

【解決手段】インジウム元素及び酸素元素を含有した非晶質膜をスパッタリング装置で成膜し加熱することで、X線回折測定において2θが25deg〜35degの範囲に観測される(222)配向のロッキングカーブの半値全幅が0.4deg以下である多結晶薄膜を形成する。又、金属酸化物をスパッタリングによって成膜するに際し、プラズマの照射を2〜5秒間隔として成膜しその後結晶化する。

(もっと読む)

真空成膜方法およびその装置

【課題】成形機から取り出された被成膜製品の水分吸蔵を抑制して真空引きに消費するエネルギを低減できる省エネルギ化を、成形機の外で実現できるようにして、既設成形機の利用を可能にした真空成膜装置を提供する。

【解決手段】成形機11の傍に隣接して真空成膜装置本体12を設置し、成形機11と真空成膜装置本体12との間に移載装置13を設置する。移載装置13は、被成膜製品Wを保持する被成膜製品保持部25の両側に被成膜製品保温装置26を設け、移載中の被成膜製品Wに温風を吹き付けて成型直後の高温被成膜製品Wを保温および乾燥する。さらに、この移載装置13のX方向ガイドレール21に、成形機11からの脱型時の被成膜製品Wに帯電した静電気を除去する静電気除去装置27を設ける。

(もっと読む)

半導体装置及びその作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5ラ1010dyn/cm2 〜5ラ1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

二層薄膜構造体、超電導物質三層薄膜構造体及びその製造方法

【課題】

格子定数を変化させたCeO2層の作用でCeO2面側に高い臨界電流を有する超電導膜を得ることができるCeO2層を有するA l2O3-CeO2二層薄膜構造体、当該Al2O3-CeO2二層薄膜構造体を用いて、格子定数を変化させたCeO2層を活用してCeO2面側に高い臨界電流を有する超電導膜を形成したAl2O3-CeO2-超電導物質三層薄膜構造体及びその製造方法を提供する。

【解決手段】

厚さ0.4mm〜1.0mmのAl2O3単結晶層上に、厚さ20nm〜300nmのCeO2層を設けた薄膜構造体に、エネルギー密度1mJ/cm2〜250mJ/cm2のレーザ光を1000〜1000000パルス照射し、CeO2層の格子定数を変化させたCeO2を有するAl2O3-CeO2二層薄膜構造体のCeO2層側に厚さ100nm〜800nmの超電導薄膜を設けたAl2O3-CeO2-超電導物質三層薄膜構造体及びその製造方法。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】エピタキシャル層の形成中にシリコン基板の表面に設けられた不純物の埋込層からのオートドープを抑制することのできるエピタキシャルウェーハの製造方法を提供すること。

【解決手段】本発明のエピタキシャルウェーハの製造方法は、シリコン基板の主表面にイオン注入法によって不純物を注入して第1素子分離不純物埋込層を形成する第1素子分離不純物注入工程S2と、前記第1素子分離不純物注入工程S2を経たシリコン基板にエピタキシャル層を形成させるエピタキシャル層形成工程S3と、を備え、第1素子分離不純物注入工程S2におけるイオン注入時のエネルギーが100〜200keVであり、かつ第1素子分離不純物注入工程S2とエピタキシャル層形成工程S3との間に実質的に熱処理を行なわないことを特徴とする。

(もっと読む)

構造化被覆部を基板上に形成する方法、被覆済み基板、および、被覆済み基板を備えた半完成品

本発明は、構造化被覆部を基板上に形成する方法であって、被覆される表面を有する基板を準備するステップと、少なくとも1種類の蒸着被覆物質、具体的には、酸化アルミニウム、二酸化ケイ素、窒化ケイ素、または、二酸化チタンを、熱蒸着法および加法的構造化法によって上記被覆される基板表面上に積層することによって、該表面上に構造化被覆部を形成するステップとを含む、方法に関する。本発明は、さらに、被覆済み基板および被覆済み基板を備えた半完成品にも関する。  (もっと読む)

(もっと読む)

被覆工具

【課題】高速度加工、高送り加工、難削材の加工など加工条件が厳しい切削加工において、長寿命を実現する被覆工具の提供を目的とする。

【解決手段】

基材とその表面に被覆された被膜とからなり、Cr−Kα線を用いたX線応力測定により得られた基材の圧縮残留応力σbCrは、Co−Kα線を用いたX線応力測定により得られた基材の圧縮残留応力σbCoよりも大きい被覆工具。

(もっと読む)

透明電極の製造方法

【課題】透明導電膜を結晶化させることにより透明電極の耐薬品性を高めることができると共に、透明導電膜の結晶化時に高分子材料基板を変形・劣化させることがない透明電極の製造方法を提供する。

【解決手段】高分子材料基板上に、Snを含有する非晶質透明導電膜を形成する工程と、非晶質透明導電膜を110℃以上130℃未満の温度で熱処理して結晶質透明電極とする工程とを含むことを特徴とする、透明電極の製造方法である。ここで、非晶質透明導電膜のSn濃度は、SnO2換算で1〜5質量%であることが好ましい。

(もっと読む)

101 - 120 / 294

[ Back to top ]