Fターム[4K029FA01]の内容

Fターム[4K029FA01]の下位に属するFターム

粗面化 (43)

平滑化 (18)

清浄化、クリーニング (462)

放電処理、プラズマ処理 (656)

加熱処理 (104)

樹脂下地層、アンダコート層の形成 (224)

Fターム[4K029FA01]に分類される特許

141 - 160 / 294

半導体装置及びその製造方法

【課題】エレクトロマイグレーションの抑制が図られた半導体装置を提供する。

【解決手段】半導体装置は、半導体素子の形成された半導体基板と、半導体基板の上方に、水分を含み、凹部が形成された層間絶縁膜と、凹部の内面上に形成され、非晶質及び多結晶の一方の結晶性を有する第1のバリアメタル層と、第1のバリアメタル層上に形成され、非晶質及び多結晶の他方の結晶性を有する第2のバリアメタル層と、第2のバリアメタル層上に形成された銅配線と、銅配線を覆って前記層間絶縁膜上に形成された銅拡散防止絶縁膜と、銅配線と銅拡散防止絶縁膜との界面に形成された金属酸化物層とを有する。

(もっと読む)

スパッタ成膜装置

【課題】装置全体の小型化を図れ、また効率的な処理を行えるマルチチャンバ式のスパッタ成膜装置を提供する。

【解決手段】本発明のスパッタ成膜装置は、基板保持具に対して基板Wの脱着が行われる脱着機構16と、基板Wに対して前処理が行われる前処理室34と、基板Wに対してスパッタ成膜処理が行われる複数の成膜室35a〜35dとを備え、それぞれの成膜室35a〜35d内には基板Wを静電吸着した状態で回転可能な静電チャックテーブル62が設けられ、一つの成膜室につき複数のスパッタ源51が設けられ、それぞれのスパッタ源51には静電吸着面62aに対して傾斜した状態で対向するターゲット50が装着され、それぞれの成膜室35a〜35d内には複数のスパッタ源51のうちの少なくとも1つを成膜室内の放電空間に対して遮蔽可能なシャッター65が設けられている。

(もっと読む)

PVD法のための基材前処理方法

本発明は、ターゲットとして実施され、アーク蒸発ソースの一部である第1の電極を有する真空処理システム内でワークピースを表面処理する方法であって、第1の電極によって、アーク電流を用いてアークを動作させ、ターゲットから、ワークピース上に少なくとも部分的に、かつ断続的に堆積させる材料を蒸発させ、ワークピースホルダとして実施され、ワークピースと共にバイアス電極を構成する第2の電極を有し、電圧供給部によって、バイアス電極にアーク電流と整合するようにバイアス電圧を印加し、したがって本質的に、表面上に材料が正味で蓄積されない方法に関する。  (もっと読む)

(もっと読む)

蒸着装置及び有機EL表示装置の製造方法

【課題】蒸着マスクよりサイズの大きい基板への高精細の蒸着マスク蒸着を容易に行うことができる蒸着装置及び有機EL表示装置の製造方法を提供する。

【解決手段】蒸着装置は、蒸着チャンバ1と、基板の被成膜領域よりサイズの小さい蒸着マスク2と、蒸着マスクを介して被成膜領域に蒸着材料を蒸着させる蒸着源3と、基板と、蒸着マスク及び蒸着源と、の相対位置を移動させる移動機構と、制御部5と、を備えている。制御部5は、移動機構を稼動させ、基板と、蒸着マスク及び蒸着源との相対位置をステップ状に移動させ、被成膜領域を複数に分割して蒸着させる。

(もっと読む)

タッチパネルディスプレイとともに使用するためのITO被覆品の製造方法、および/または前記ITO被覆品の製造方法

この発明のある種の実施具体例は、熱処理されたガラス基板によって支持される透明導電性インジウムスズ酸化物(ITO)膜を有する被覆品の製造技術に関する。実質的に亜酸化のITOまたは金属インジウムスズ(InSn)膜をガラス基板上に室温でスパッタリング蒸着する。上に蒸着された状態の膜を有するガラス基板を昇温する。熱による焼き戻し、または熱強化は、蒸着された状態の膜を結晶透明導電性ITO膜に変換する。有利なことに、このことは、例えば、金属モードにおけるITO蒸着の一層高い速度のため、タッチパネル組立品のコストが減少する可能性がある。フロートガラスの使用によってタッチパネル組立品のコストが一層減少する可能性がある。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】アンダーバンプメタルのCuの膜質のバラツキを抑制してサイドエッチ量のバラツキを低減する半導体装置の製造方法及び半導体製造装置を提供することを目的とする。

【解決手段】本発明は、半導体ウエハに形成された半導体チップにアンダーバンプメタルを蒸着するスパッタ装置内の温度を判定する判定ステップと、前記スパッタ装置内の温度がアンダーバンプメタルの蒸着に適した所定温度以上でないと判定したときに、前記スパッタ装置にダミーウエハを投入するダミーウエハ投入ステップと、前記スパッタ装置にダミーウエハを投入して前記スパッタ装置内の温度が前記所定温度以上となったと判定したときに、前記半導体ウエハを前記スパッタ装置に投入する半導体ウエハ投入ステップと、を有する半導体装置の製造方法とした。

(もっと読む)

圧電体膜の製造方法

【課題】圧電性能と耐久性とがいずれも良好なPZT系の圧電体膜を提供する。

【解決手段】圧電体膜の製造方法は、式(P)で表されるペロブスカイト酸化物からなる圧電体膜の製造方法において、a/b≧1.07の条件で成膜を行う工程(A)と、a/b<1.07の条件で成膜を行う工程(B)とを順次実施して、パイロクロア相を含まないペロブスカイト単相構造であり、a/b≦1.06である圧電体膜を製造する。Pba(Zrx,Tiy,Mb−x−y)bOc・・・(P)(式中、Mは1種又は2種以上のBサイト元素を示す。0<x<b、0<y<b、0≦b−x−y。a:b:c=1:1:3が標準であるが、これらのモル比はペロブスカイト構造を取り得る範囲内で基準モル比からずれてもよい。)

(もっと読む)

反転型感光性デバイス

本発明は、反転して増大する有機感光性光電子デバイスに関する。本発明の反転型有機感光性光電子デバイスは、反射電極、前記反射電極の上の有機ドナー−アクセプターヘテロ接合、および前記ドナー−アクセプターヘテロ接合上の透明電極を含む。 (もっと読む)

成膜方法

【課題】 実用に耐えうる耐摩耗性を備えた撥油性膜を持つ撥油性基材を製造することができる成膜方法を提供する。

【解決手段】 成膜方法は、基板101の表面にエネルギーを持つ粒子を照射する第1の照射工程と、前記第1の照射工程後の基板101の表面に乾式法を用いて第1の膜103を成膜する第1の成膜工程と、第1の膜103の表面に撥油性を有する第2の膜105を成膜する第2の成膜工程とを、有する。

(もっと読む)

マスクブランク用基板セットおよびマスクブランクセット

【課題】高いフォトマスクの重ね合わせ精度を要求されるフォトマスクに好適な基板セットを提供すること。

【解決手段】本発明の基板セットは、露光装置のマスクステージにチャックされるフォトマスクを作製するためのマスクブランクで使用される基板を複数枚セットとしたマスクブランク用基板セットであって、複数枚セットで用いられる基板は、転写パターンを形成する薄膜を設ける側の主表面の形状が中央で相対的に高く、周縁部で相対的に低くなるような凸形状であり、前記主表面の中央部を含む142mm角の領域における平坦度が0.3μm以下であり、基準基板の基準主表面に対してフィティングを行ったときの差が40nm以下であることを特徴とする。

(もっと読む)

ダメージフリー被覆刻設堆積法

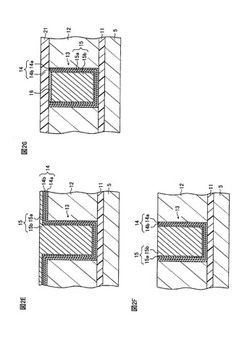

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

BiTe系薄膜、その作製方法、および赤外線センサ

【課題】 結晶性に優れ、パターン化されたBiTe系薄膜、その作製方法、および赤外線センサを提供する。

【解決手段】 本発明のBiTe系薄膜は、基板と、基板上に位置するBiTe系薄膜とを備える。そのBiTe系薄膜は、パターニングされており、かつ、X線回折における(001)面のピーク値と(015)面のピーク値との比であるc軸配向度が、1.0以上であることを特徴とする。

(もっと読む)

薄膜付きガラス基板の製造方法

【課題】反りの少ない薄膜付きガラス基板を容易に製造することができる薄膜付きガラス基板の製造方法を提供する。

【解決手段】薄膜形成後の最終状態においてガラス基板10の主面10aが平坦となるように、ガラス基板10を塑性変形させることによりガラス基板10の主面10aを湾曲した形状とする変形工程と、塑性変形させたガラス基板10の主面10a上に薄膜11を形成する薄膜形成工程とを行う。

(もっと読む)

成膜方法及び成膜装置

【課題】 両面積層基板の生産効率を低下させることなく、第1の金属膜の表面と第2の金属膜の表面とがくっつく不具合や、しわが生じる不具合等を防ぐことができる成膜方法を提案する。

【解決手段】 減圧雰囲気下においてロール・ツー・ロールで搬送される有機樹脂フィルムFの両面に金属膜を成膜する両面積層基板の成膜方法であって、有機樹脂フィルムFの一方の面に乾式めっき法である成膜手段13a、13bにより第1の金属膜を成膜し、この第1の金属膜の表面に乾式表面処理手段11により酸化膜を形成した後、有機樹脂フィルムFの他方の面に乾式めっき法である成膜手段13a、13bにより第2の金属膜を成膜する。

(もっと読む)

線形的誘電特性を示す誘電体薄膜組成物

【課題】電子トンネリングを防止するのに十分な厚さにおいても、要求されるキャパシタンス値を満たすことができる高誘電率の誘電定数を有し、誘電損失が非常に低く、常誘電特性を示す線形的なBSTO誘電体薄膜組成物を提供する。

【解決手段】(Ba、Sr)TiO3(BSTO)誘電体薄膜に錫酸化物(SnO2)が連続組成拡散法によって添加され、一般式Ba(1−x)SrxTi(1−y)SnyO3(式中、モル分率xは0.06≦x≦0.82の範囲であり、モル分率yは0.05≦y≦0.28の範囲である)(BSTSO)である誘電体薄膜組成物とする。これにより、電界によるキャパシタンスの変化がほとんどなく、要求されるキャパシタンス値を示し誘電損失は非常に低く、既存の誘電体素材であるSiO2のような常誘電(paraelectric)特性を示す。

(もっと読む)

高品質化合物半導体材料を製造するためのナノ構造適応層及びHVPEを使用する成長法

【課題】品質に優れ、平坦で厚い化合物半導体を成長させるための方法を提供する。

【解決手段】HVPEを利用し、ナノ構造層を使用して高品質の平坦かつ厚い化合物半導体(15)を異種基板(10)上に成長させる。半導体材料のナノ構造(12)は、分子線エピタキシャル成長(MBE)、化学気相成長(CVD)、有機金属化学気相成長(MOCVD)又はハイドライド気相エピタキシャル成長(HVPE)によって基板(10)上に成長させることができる。化合物半導体の厚膜(15)又はウェハは、HVPEを使用したエピタキシャル横方向成長によってナノ構造(12)上に成長させることができる。

(もっと読む)

成膜方法及び処理システム

【課題】例えばCu膜に対するバリヤ性及び密着性を高く維持することができる層構造を形成する成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器132内で、表面に凹部2を有する被処理体Wの表面に成膜処理を施す成膜方法において、遷移金属含有原料ガスを用いて熱処理により遷移金属含有膜210を形成する遷移金属含有膜形成工程と、元素周期表のVIII族の元素を含む金属膜212を形成する金属膜形成工程とを有するようにする。これにより、例えばCu膜に対するバリヤ性及び密着性を高く維持する。

(もっと読む)

化合物半導体発光素子およびそれを用いる照明装置ならびに化合物半導体発光素子の製造方法

【課題】ナノコラムを複数有して成る化合物半導体発光素子において、蛍光体を用いることなく、高い発光効率で、色味を高精度に調整可能とする。

【解決手段】Si基板4の一部領域にトレンチ11を形成し、そのトレンチ11内にさらにナノコラム2の化合物種結晶膜であるAlN層12を形成した後にナノコラム2を成長させることで、前記AlN層12の有る領域は、それが無い壁13上の領域に比べて、成長が速く、所定の時間成長させると、前記トレンチ11と壁13との段差を吸収して、p型層14の表面が略同じ高さとなる。これによって、同一基板でかつ単一の成長工程で簡単に、したがって低コストに、白色光などの所望の色味を実現できる。また、蛍光体を用いずに所望の色味を実現できるので、高い信頼性および長寿命化を図ることができるとともに、トレンチ11の面積を任意に調整し、色味を細かく高精度に調整できる。

(もっと読む)

表面処理装置および表面処理方法

【課題】処理むらを防止して、良好な被膜を安定的に形成できるようにした表面処理装置および表面処理方法を提供する。

【解決装置】本発明の表面処理方法は、大気圧よりも低い圧力下でシランカップリング剤Y1を気化させ、気化したシランカップリング剤Y2の雰囲気に無機膜10を有する基板Wを晒すことで無機膜10上にシランカップリング剤の被膜を形成する表面処理工程を有する。また、本発明の表面処理装置1は、上記表面処理方法に用いられる装置であって、シランカップリング剤Y1を気化させる処理剤気化装置21と、処理剤気化装置21に対してキャリアガスを供給するガス供給装置22と、無機膜10を有した基板10を配置するとともに気化したシランカップリング剤Y2が供給される成膜室3と、成膜室3内を減圧するポンプ5とを有する。

(もっと読む)

薄膜形成方法

【課題】薄膜と半導体基板の熱膨張係数の違いに起因する半導体基板の反りを、生産性や信頼性を低下させることなく抑制する薄膜形成方法を提供する。

【解決手段】ウェハ2(半導体基板)の裏面2b(表面)に、ウェハ2とNi膜を形成する方法が、真空引き可能なロードロックチャンバ20内にウェハ2を配置する工程と、ロードロックチャンバ20内に配置したウェハ2を予め冷却する冷却工程と、ロードロックチャンバ20内を真空引きする真空引き工程と、冷却工程と真空引き工程を実施した後にウェハ2の裏面2bにNi膜を形成する工程を備えている。

(もっと読む)

141 - 160 / 294

[ Back to top ]