Fターム[4K030DA04]の内容

CVD (106,390) | 前処理、後処理 (3,120) | 前処理を行うもの (2,181) | 基体の前処理を行うもの (1,282) | エッチング (186)

Fターム[4K030DA04]に分類される特許

1 - 20 / 186

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

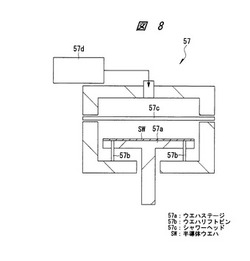

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

ダイヤモンド複合体

【課題】単結晶ダイヤモンドと多結晶ダイヤモンドの双方の利点を活かしながら、更に板状の構造を可能にするために、多結晶ダイヤモンドの研磨の困難性も回避し、研磨が容易なダイヤモンド複合体を提供すること。

【解決手段】少なくとも2種類の結晶性の異なる結晶からなる構造の複合体であり、その内の第一の結晶は高圧合成法により合成した単結晶ダイヤモンドか、あるいは気相合成法により合成した単結晶ダイヤモンドであり、第二の結晶は欠陥を面内に周期的なパターン形状で含む気相合成法により合成したダイヤモンドであり、該第一の結晶及び第二の結晶はいずれも、主面が平行になるように層状に形成されていることを特徴とするダイヤモンド複合体。

(もっと読む)

窒化物半導体積層構造体の製造方法

【課題】基板の両面に窒化物半導体層を形成するに際し、基板に被着した堆積物の除去が容易な窒化物半導体積層構造体の製造方法を提供する。

【解決手段】窒化物半導体積層構造体の製造方法では、第1および第2の面11a、11bと第1熱膨張係数α1を有する基板11の第2の面11bに、第1保護膜31を形成する。第1保護膜31が形成された基板11の第1の面11aに、第1熱膨張係数α1と異なる第2熱膨張係数α2を有する第1窒化物半導体層12を形成する。第1窒化物半導体層12に、第2保護膜34を形成する。第1保護膜31を除去し、基板11の第2の面11bを露出させる。露出した基板11の第2の面11bに、第2熱膨張係数α2に略等しい第3熱膨張係数α3を有する第2窒化物半導体層13を形成する。第2保護膜34を除去し、第1窒化物半導体層12を露出させる。

(もっと読む)

ダイヤモンド複合体およびそれから分離した単結晶ダイヤモンド

【課題】ダイヤモンド基板上に単結晶ダイヤモンドをエピタキシャル成長させるに際し、エピタキシャル成長した単結晶ダイヤモンドにおいて基板のダイヤモンドの欠陥に由来する欠陥を極力低減すること。

【解決手段】単結晶ダイヤモンド基板上の欠陥の位置に、幅と深さのアスペクト比(深さ/幅)2以上の溝又は穴を形成した単結晶ダイヤモンド基板上に、気相エピタキシャル成長法によって単結晶ダイヤモンド膜を形成してなり、前記溝又は穴の部分が空孔として結晶内部に残っていることを特徴とするダイヤモンド複合体。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】 本発明は、エピタキシャル成長工程前のエッチング工程においてエッチング量の面内均一性を改善することのできるエピタキシャルウェーハの製造方法を提供することを目的とする。

【解決手段】 シリコン単結晶基板の表面をエッチングするエッチング工程後、前記シリコン単結晶基板の表面に原料ガスを用いてエピタキシャル層を気相成長させるエピタキシャル成長工程を行うエピタキシャルウェーハの製造方法であって、前記エッチング工程において、エッチングガスとキャリアガスに前記原料ガスを含めたガスで前記シリコン単結晶基板の表面をエッチングすることを特徴とするエピタキシャルウェーハの製造方法。

(もっと読む)

SiCエピタキシャルウェハ及びその製造方法

【課題】ウェハの全面にステップバンチングがない、ステップバンチングフリーのSiCエピタキシャルウェハ及びその製造方法を提供する。

【解決手段】本発明のSiCエピタキシャルウェハは、0.4°〜5°のオフ角で傾斜させた4H−SiC単結晶基板上にSiCのエピタキシャル層を形成したSiCエピタキシャルウェハであって、短いステップバンチングがないことを特徴とする。

(もっと読む)

エピタキシコーティングされたシリコンウェーハ及びエピタキシコーティングされたシリコンウェーハの製造法

【課題】従来技術と比較して改善された全体的平坦度を有するエピタキシコーティングされたシリコンウェーハの製造法を提供する。

【解決手段】エピタキシコーティングされたシリコンウェーハの製造法において、少なくとも前面が研磨された複数のシリコンウェーハを用意し、かつ引き続き、用意したシリコンウェーハのそれぞれ1つをエピタキシリアクタ中のサセプタに載置し、第一の工程では水素雰囲気下でのみ前処理し、かつ第二の工程では水素雰囲気に1.5〜5slmの流量でエッチング剤を添加して前処理し、その際、水素流量は双方の工程において1〜100slmであり、引き続きその研磨された前面上でエピタキシコーティングし、かつエピタキシリアクタから取り出すという手法により個々にそれぞれエピタキシリアクタ中でコーティングすることを特徴とする方法。

(もっと読む)

半導体基板を処理する方法

【課題】クリーンかつダメージのない表面を半導体基板上に形成するための装置および方法を提供する。

【解決手段】エピタキシャル層を形成する前にプラズマ洗浄プロセスに基板の表面を暴露するように適合された洗浄チャンバを含有するシステム。洗浄プロセスを基板に実施する前に、該洗浄チャンバの内部表面にゲッタリング材料を堆積することによって、該洗浄チャンバで処理された基板の汚染物を減少するための方法が用いられる。酸化およびエッチングステップが洗浄チャンバにおいて基板に繰り返し実施されて、エピタキシャルを配置可能な基板にクリーンな表面を暴露および生成する。一実施形態において、低エネルギプラズマが該洗浄ステップ時に使用される。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体ウエハの表面に膜を成長させる技術であって、半導体装置を効率よく製造することが可能な技術を提供する。

【解決手段】 半導体装置の製造方法であって、チャンバ内に配置された半導体ウエハの表面に膜を成長させる動作と、チャンバ内に配置された半導体ウエハと前記膜とをエッチング可能なエッチングガスをチャンバ内に導入する動作とを実行可能な半導体製造装置のチャンバ内に半導体ウエハを搬入する搬入工程と、チャンバ内に前記エッチングガスを導入する第1エッチング工程と、チャンバ内の半導体ウエハの表面に膜を成長させる第1成膜工程と、チャンバから半導体ウエハを搬出するとともに、チャンバに別の半導体ウエハを搬入する入れ換え工程と、チャンバ内に前記エッチングガスを導入する第2エッチング工程と、チャンバ内の半導体ウエハの表面に膜を成長させる第2成膜工程を有する。

(もっと読む)

表面処理装置および表面処理方法

【課題】 自己放電型の表面処理装置および表面処理方法において、自己バイアス電圧の変化に関係なく安定した表面処理を実現し、ひいては安定した表面処理結果を得る。

【解決手段】 本発明に係るプラズマCVD装置10によれば、真空槽10と被処理物としての各基板18,18,…とを一対の電極として、これらに放電用電力としての正弦波電力Wpが供給される。このとき、各基板18,18,…の表面に負の直流電圧である自己バイアス電圧が現れる。併せて、真空槽10を陽極とし、各基板18,18,…を陰極として、これらに直流電力Waが供給される。これによって、各基板18,18,…には、自己バイアス電圧を含む直流電圧Vaが印加された状態となる。ゆえに、自己バイアス電圧が変化したとしても、この自己バイアス電圧を含む直流電圧Vaは一定であるので、安定した表面処理が実現され、ひいては安定した表面処理結果を得ることができる。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】平坦度や膜厚均一性が向上した不純物ドープトシリコン膜を成膜できる基板処理技術を提供する。

【解決手段】金属膜と該金属膜の表面の少なくとも一部に金属酸化膜が形成された基板を処理室内へ搬入する工程と、前記基板を収容した処理室内へ不純物含有ガスを供給し、前記金属酸化膜を除去する酸化膜除去工程と、前記処理室内に前記不純物含有ガスおよびシリコン含有ガスを供給し、前記金属膜上に不純物が添加されたシリコン含有膜を形成するシリコン含有膜形成工程と、前記シリコン含有膜が形成された基板を処理室内から搬出する工程とから、半導体装置の製造方法を構成する。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

【課題】CMOSトランジスタのソース−ドレイン置換技術に関し、装置一式を利用して基板材料に窪みをエッチングして、その後、応力を有する異なる材料を堆積することに関し、大気に曝すことなく、エッチングとその後の堆積とを行う方法の提供。

【解決手段】エッチングおよびデポジションによりCMOSトランジスタの接合領域を形成する方法であって、

第1接合領域270を形成すべくゲート電極190の隣の基板120の第1箇所と、前記基板120に第2接合領域280を形成すべく前記ゲート電極190を介して前記第1箇所とは反対側に位置する前記基板120の第2箇所とを除去する工程と、前記第1接合領域270と前記第2接合領域280とに結晶質材料のエピタキシャル厚みを有する層を形成する工程とを含み、前記除去する工程と前記形成する工程は同一のチャンバ内で前記チャンバの封止を破ることなく行う。

(もっと読む)

基板処理装置及び基板の製造方法

【課題】基板表面のダメージを取り除くためのエッチング工程における表面の荒れを抑制する。

【解決手段】反応室を昇温すると共に、反応室が第1温度となった後に複数の基板に第1エッチングガスを供給する第1エッチング工程と、反応室が第1温度より高い第2温度となった後に、第1エッチングガスと共にシリコン原子含有ガスを複数の基板に向けて供給する第2エッチング工程と、反応室が第2温度より高い第3温度となった後に、シリコン原子含有ガス、及び、炭素原子含有ガスを複数の基板に向けて供給し、複数の基板に炭化珪素膜を形成する第1成膜工程を有する。

(もっと読む)

ダイヤモンドライクカーボン薄膜の製造方法及び該薄膜が金属基板上に形成された電極材料

【課題】極めて電気抵抗の低いホウ素ドープ導電性ダイヤモンドライクカーボン薄膜の製造方法及び金属基板上に薄膜を一体構成した電極材料を提供する。

【解決手段】炭素源として炭化水素を、ホウ素源として有機ホウ素化合物を用い、反応調整ガスとしてアルゴンガスを混在させ、高周波プラズマCVDにより基板上にホウ素ドープダイヤモンドライクカーボンを形成させる。

(もっと読む)

サセプタ及びこれを用いたエピタキシャルウェーハの製造方法

【課題】 半導体基板外周部であって、サセプタの裏面側の上段座ぐり部に対応する位置の温度を下げ、基板裏面における外周部と内周部との熱的条件を一定にし、基板裏面における裏面デポの発生を抑制できるサセプタ及びそのサセプタを用いたエピタキシャルウェーハの製造方法を提供することで問題の解決を試みた。

【解決手段】 エピタキシャル層の気相成長を行う際に半導体基板を支持するサセプタであって、サセプタの上面には、内部に半導体基板が配置される座ぐりが形成され、該座ぐりは、半導体基板の外周縁部を支持する上段座ぐり部と、該上段座ぐり部よりも下段でかつ中心側に形成された下段座ぐり部とを有する二段構造を成し、下段座ぐり部には、前記サセプタの裏面まで貫通し、気相成長を行う際にも開放状態となる貫通孔が形成されており、サセプタの裏面側には、上段座ぐり部に対応する位置に溝が設けられたものであることを特徴とするサセプタ。

(もっと読む)

ロールコーター装置

【課題】非晶質炭素膜の強度を高めることができるとともに、小型化を図ることができるようにする。

【解決手段】本発明は、連続して搬送される被成膜基材Pに非晶質炭素膜を形成する非晶質炭素膜形成部Eを有するロールコーター装置において、その非晶質炭素膜形成部Eに至る上記搬送経路αの上流側に、上記被成膜基材Pを加熱するための加熱機能部C,D,E,G,Hを配設したものである。

(もっと読む)

ノズル

【課題】メンテナンス作業の手間を低減させ、プラズマCVD装置の稼動率を向上させながらも、被処理体の膜厚のばらつきを抑制できるノズルを提供する。

【解決手段】被処理体1の表面に成膜処理を施すプラズマCVD装置に取り付けられ、被処理体1が配置された放電空間に放電ガスおよび成膜ガスを供給し、放電ガスを供給する放電ガス流路14と成膜ガスを供給する成膜ガス流路16とを各別に設け、放電ガス流路14の下流側の端部に、放電ガスを吐出する放電ガス吐出口15を設けるとともに、成膜ガス流路16の下流側の端部に、放電ガス吐出口15から吐出される放電ガスを挟み込み又は包囲する領域に成膜ガスを吐出する成膜ガス吐出口17を設けてある。

(もっと読む)

1 - 20 / 186

[ Back to top ]