Fターム[4M104AA03]の内容

Fターム[4M104AA03]の下位に属するFターム

Fターム[4M104AA03]に分類される特許

201 - 220 / 1,500

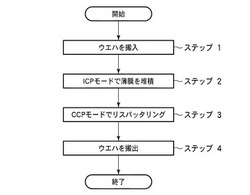

成膜方法およびリスパッタ方法、ならびに成膜装置

【課題】トレンチおよび/またはホールの間口のオーバーハングを抑制することができる成膜方法およびリスパッタリング方法を提供すること。

【解決手段】処理容器内にプラズマ生成ガスを導入しつつ誘導結合プラズマ生成機構により処理容器内に誘導結合プラズマを生成し、直流電源から金属ターゲットに直流電力を供給し、バイアス電源により載置台に高周波バイアスを印加して、載置台上の被処理基板に金属薄膜を堆積させる工程と、誘導結合プラズマ生成機構によるプラズマの生成と直流電源への給電を停止し、処理容器内にプラズマ生成ガスを導入しつつ載置台に高周波バイアスを印加して、処理容器内に容量結合プラズマを形成するとともにプラズマ生成ガスのイオンを被処理基板に引き込んで堆積された金属薄膜をリスパッタリングする工程とを有する。

(もっと読む)

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

電界効果トランジスタの製造方法及びそれに用いる製造装置

【課題】生産性が高く微細な電界効果トランジスタとその製造方法ならびに製造装置を提供すること。

【解決手段】以下の工程(1)から(3)よりなる印刷工程により前記基板上へラインもしくはスペース最小幅が1から50μmであり、印刷位置精度が100ppm以下の機能性膜の形成を行うことを特徴とする電界効果トランジスタの製造方法としたもの。

工程(1) 版の画線部に相当する溝構造部にドクターブレードを用いたインキング法で、機能性材料が溶媒へ溶解もしくは分散した薬液を充填する工程。

工程(2) 転写シリンダーと前記版を接触させ、前記溝構造部の薬液を前記転写シリンダーへ転移させる工程。

工程(3) 前記転写シリンダー上の薬液を前記基板の所定の位置へ転写し、機能性膜の形成を行う工程。

(もっと読む)

半導体装置及びその製造方法

【課題】素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、CMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置を提供する。

【解決手段】n−型ドリフト層114と、n−型ドリフト層114における活性領域R1に形成したp型半導体材料からなる複数の柱状埋込層118と、周辺耐圧領域R2に形成したリング状の第2トレンチ122、第2トレンチ122の内面に形成した絶縁膜124及び第2トレンチ122の内部に絶縁膜124を介して形成した導電性材料層126を有し、逆バイアス時には導電性材料層126及び柱状埋込層118に挟まれた部分のn−型ドリフト層114を空乏化させる周辺耐圧構造120と、周辺領域R3に形成したp型半導体材料からなる1又は2以上の第2柱状埋込層130とを備える半導体装置100。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の実施形態は、トレンチ構造におけるゲート・ソース間容量を低減できる半導体装置およびその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1導電形の半導体層と、前記半導体層の第1の主面側に設けられた第1主電極と、前記半導体層の第2の主面側に設けられた第2主電極と、前記半導体層の前記第1の主面側から前記第2の主面の方向に形成されたトレンチの内部に設けられ、前記第1主電極と前記第2主電極との間に流れる電流を制御する2つの第1制御電極と、前記トレンチの内部において、前記2つの第1制御電極と、前記第2の主面側の底面と、の間に設けられた第2制御電極と、を備える。前記2つの第1制御電極は、前記第1の主面に平行な方向に離間して設けられ、それぞれ第1の絶縁膜を介して前記トレンチの内面に対向し、前記第2制御電極は、第2の絶縁膜を介して前記トレンチの内面と対向する。

(もっと読む)

半導体装置及びその製造方法

【課題】素子面積を増加させずに順電圧降下を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域と、第1電極と、第2半導体領域と、絶縁領域と、第2電極と、を備える。第1半導体領域は、第1部分と、第1主面上において第1主面に直交する第1方向に延在した第2部分と、を有する第1導電形の半導体領域である。第1電極は、第2部分と対向して設けられた金属領域である第3部分と、第3部分と、第2部分と、をむすぶ第2方向に延在し、かつ第1方向に延在する第4部分と、を有する。第2半導体領域は、第2部分と、第3部分と、のあいだに設けられ、第1半導体領域よりも不純物濃度の低い第1濃度領域を有し、第3部分とショットキー接合した第1導電形の半導体領域である。絶縁領域は、第4部分と、第2半導体領域と、のあいだに設けられる。第2電極は、第1部分と導通する。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】樹脂基板上に設けたボトムゲート型薄膜トランジスタにおいて、製造プロセスを簡略化することにより、高品質で低コストの薄膜トランジスタとその製造方法及び画像表示装置を提供することを目的とする。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

半導体装置

【課題】本発明の実施形態は、サージ耐量が高く、順方向の電流密度を向上させることが可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、第1導電形の半導体層と、前記半導体層の第1の主面に選択的に設けられた第2導電形の第1の領域と、前記第1の領域に接続して前記第1の主面に選択的に設けられた第2導電形の第2の領域と、を備える。そして、前記半導体層と前記第1の領域とに接して設けられた第1の電極と、前記第2の領域に接して設けられた第2の電極と、前記半導体層の前記第1の主面とは反対の第2の主面側に電気的に接続された第3の電極とを備える。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

ショットキーバリアダイオード

【課題】ジャンクションバリアショットキー構造をもつダイオードにおいて、ショットキー接合部の逆サージ耐量を改善することが可能なショットキーバリアダイオードを提供する。

【解決手段】ガードリング層15に隣接した第二半導体層161と、この第二半導体層161に隣接する第二半導体層162との間に跨るように、基板11の中心領域Acにおいて第三絶縁層23が形成されている。即ち、第二半導体層161と第二半導体層162との間で、基板11の一面(一方の主面)11aに露呈された第一半導体層13を覆うように第三絶縁層23が形成される。これによって、第三絶縁層23は、第二半導体層161と第二半導体層162との間で基板11の一面11aに露呈された第一半導体層13と、金属層14との間を電気的に絶縁する。

(もっと読む)

ダイオードの製造方法

【課題】製造過程でエピタキシャル層の表面部に形成されるエッチピットに起因するリーク電流を抑えること。

【解決手段】ダイオードの製造方法は、エピタキシャル層の表面にキャップ層を形成するキャップ層形成工程(S3)と、キャップ層が形成されている状態でドーパントを活性化させるアニール工程(S4)と、キャップ層を除去するキャップ層除去工程(S5)と、エッチング技術を利用してエピタキシャル層の表面を洗浄する洗浄工程(S6)と、エピタキシャル層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程(S7)と、を備えている。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】SiC半導体装置において、不純物添加工程や表面保護膜形成におけるプロセス条件のばらつきがあっても、簡便に逆方向耐圧に大きな影響を与えないターミネーション構造(接合終端構造)を提供する。

【解決手段】素子の外周端部に、第1導電型の耐圧維持層および有限長さの前記第1導電型とは異なる第2導電型の領域からなる接合終端構造を備えたSiC半導体素子であって、前記接合終端構造の一部において、第1の方向である層方向に対して均一ではなく、前記接合終端領域の内側端であって前記素子の外周端から前記接合終端領域の外側端に向かって、前記第1導電型領域の不純物濃度が空間的に変調され、不純物濃度が徐々に減少する傾向を持って形成された接合終端構造を有することを特徴とするSiC半導体素子。

(もっと読む)

半導体装置及び電子機器

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導

体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作

製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって

形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチ

ング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを

用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

高耐圧半導体装置

【課題】高耐圧半導体装置の大型化を招くことなく、従来の高耐圧半導体装置900の場合よりも「気中放電による逆耐圧の低下」を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタルからなる第1電極層層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118と、半導体層110の表面上において第1電極層128を取り囲む領域に形成された絶縁層124とを備え、第2ガードリング層118が絶縁層124の外周近傍まで形成されている高耐圧半導体装置100。

(もっと読む)

厚膜金属電極の形成方法、及び厚膜レジストの形成方法

【課題】炭化珪素基板に形成された回路素子層上に、厚さが7μm以上で、かつ面内均一性に優れたポジ−ネガ反転型レジストが形成可能な厚膜金属電極の形成方法、及び厚膜レジストの形成方法を提供する。

【解決手段】HMDS処理された回路素子層の上面に、第1の粘性値を有した第1のポジ−ネガ反転型レジストを形成し、次いで、第1のポジ−ネガ反転型レジスト上に、第1及び第2のポジ−ネガ反転型レジスト(厚膜レジスト)の合計の厚さが7μm以上となるように、第1の粘性値よりも大きい第2の粘性値を有した第2のポジ−ネガ反転型レジストを形成する。

(もっと読む)

電界効果トランジスタとその製造方法

【課題】電界効果トランジスタとその製造方法において、電界効果トランジスタの耐圧を高めつつそのオン抵抗を低減すること。

【解決手段】基板1と、基板1の上に形成され、複数の第1の半導体層3と複数の層間絶縁層4とが交互に積層された積層体10と、積層体10の側面10aに形成されると共に、該側面10aにおいて複数の第1の半導体層3の各々に接続された第2の半導体層12と、第2の半導体層12の上に形成されたゲート絶縁層17と、ゲート絶縁層17の上に形成され、ゲート絶縁層17を介して側面10aに対向するゲート電極19と、第2の半導体層12に電気的に接続されたソース電極14と、複数の第1の半導体層3の各々に電気的に接続されたドレイン電極15とを有する電界効果トランジスタによる。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧な半導体素子を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、第一と第二の主面を有する炭化珪素基板と、炭化珪素基板の第一の主面に設けられた第一導電型の第一の炭化珪素層と、第一の炭化珪素層の表面に形成された第二導電型の第一の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第一導電型の第二の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第二導電型の第三の炭化珪素領域と、第一の炭化珪素層、第一の炭化珪素領域および第三の炭化珪素領域の表面に連続的に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された炭化珪素からなる第一の電極と、第一の電極上に形成された第二の電極と、第一と第二の電極を被覆する層間絶縁膜と、第二の炭化珪素領域と第三の炭化珪素領域と電気的に接続される第三の電極と、炭化珪素基板の第二の主面に形成された第4の電極と、を具備することを特徴とする。

(もっと読む)

201 - 220 / 1,500

[ Back to top ]