Fターム[4M104AA03]の内容

Fターム[4M104AA03]の下位に属するFターム

Fターム[4M104AA03]に分類される特許

61 - 80 / 1,500

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層とオーミック電極とのコンタクト抵抗を低減できる窒化物半導体装置を提供する。

【解決手段】Si基板10上に形成されたアンドープGaN層1,アンドープAlGaN層2と、アンドープGaN層1,アンドープAlGaN層2上に形成されたTi/Al/TiNからなるオーミック電極(ソース電極11,ドレイン電極12)とを備える。上記オーミック電極中の窒素濃度を1×1016cm−3以上かつ1×1020cm−3以下とする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、電界集中を緩和することで十分なサージ電流耐性を有した半導体装置およびその製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置は、炭化珪素からなる第1導電型の半導体層としてのn型半導体層1と、n型半導体層1表層において、ショットキーダイオードの素子領域を平面視上囲んで形成された、第2導電型の第1不純物層としてのp++型半導体層5aと、n型半導体層1表層において、素子領域を、少なくともp++型半導体層5aの平面視上外側から囲んで形成された、第2導電型の第2不純物層としてのp++型半導体層5bと、p++型半導体層5a表層まで延設して素子領域上に形成されたアノード電極3とを備え、p++型半導体層5aの不純物濃度が1×1020cm-3以上である。

(もっと読む)

SiC半導体素子の製造方法

【課題】電極金属がSiC単結晶基板内に拡散するのを防止してオーミック電極を形成することができるSiC半導体素子の製造方法を提供する。

【解決手段】SiC基板上にオーミック電極を形成する工程を含むSiC半導体素子の製造方法において、

上記SiC基板にそれよりも欠陥密度の高いゲッタリング層を基板面に並行して形成した後に、該ゲッタリング層よりも該基板の外寄りに上記オーミック電極を形成することを特徴とするSiC半導体素子の製造方法。

(もっと読む)

Cu−Mn合金スパッタリングターゲット材、それを用いた薄膜トランジスタ配線及び薄膜トランジスタ

【課題】高いバリア性を有するCu−Mn合金膜を形成する。

【解決手段】半導体素子の配線の形成に用いられるCu−Mn合金スパッタリングターゲット材10であって、濃度が8原子%以上30原子%以下のMnと、不可避的不純物とを含むCu−Mn合金からなり、Cu−Mn合金の平均結晶粒径が10μm以上50μm以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】薄型化された炭化シリコン基板による低抵抗化が可能な半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、炭化シリコン基板と、半導体層と、絶縁膜と、補強基板と、第1の電極と、第2の電極とを備えている。半導体層は、炭化シリコン基板の第2の面上に設けられ、素子領域と素子領域よりも端部側の周辺領域とを有する。絶縁膜は、半導体層の周辺領域の表面上に設けられている。補強基板は、周辺領域における絶縁膜上に設けられている。第1の電極は、炭化シリコン基板の第1の面に接して設けられている。第2の電極は、素子領域の表面に接して設けられている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

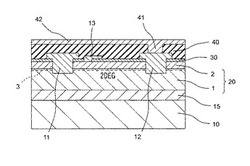

窒化物半導体装置およびその製造方法

【課題】ノーマリオフ型のHEMT構造を有し、かつ優れたデバイス特性を有する窒化物半導体装置およびその製造方法を提供する。

【解決手段】窒化物半導体装置は、窒化物半導体からなる電子走行層3と、電子走行層3に積層され、電子走行層3とはAl組成が異なり、Alを含む窒化物半導体からなる電子供給層4と、電子供給層4と電子走行層3との界面に連続する界面を有し、電子走行層3上に形成された酸化膜11と、酸化膜11を挟んで電子走行層3に対向するゲート電極8とを含む。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】第1の面と、第1の面と反対の第2の面とを有する炭化珪素半導体層110が準備される。炭化珪素半導体層110の第2の面を部分的に覆う金属層と、炭化珪素半導体層110の第2の面を部分的に覆う熱酸化膜130とが形成される。金属層を熱処理することにより電極150が形成される。金属層を形成する工程は、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い材料を用いて行われる。電極150を形成する工程において電極150の表面上に炭素が偏析する。電極150の表面および熱酸化膜130の表面の両方において、炭素を除去可能なエッチングが行われる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

半導体素子

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半

導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを

課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレ

イン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート

絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は

側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

炭化ケイ素デバイス用のエッジ終端構造およびエッジ終端構造を含む炭化ケイ素デバイスの製造方法

【課題】炭化ケイ素デバイスの改善されたエッジ終端構造を提供する。

【解決手段】炭化ケイ素半導体デバイス用のエッジ終端構造は、少なくとも炭化ケイ素ベース接合を部分的に取り囲んで、炭化ケイ素層中において、所定間隔で配置された複数の同心円のフローティングガードリング34を有すると共に、フローティングガードリング上に設けられた絶縁層、及びフローティングガードリング同士の間でかつ炭化ケイ素層の表面の近くに設けられた炭化ケイ素表面電荷補償領域38を有する。炭化ケイ素層上に窒化ケイ素層56が設けられ、窒化ケイ素層上に有機保護層66が設けられる。酸化膜層が窒化ケイ素層と炭化ケイ素層の表面との間に存在してもよい。エッジ終端構造の形成・製造方法を開示されている。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

酸化物半導体層、半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】 実施形態は、低損失な炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】 実施形態の炭化珪素半導体装置の製造方法は、炭化珪素基板にイオン注入する工程と、前記イオン注入がされた炭化珪素基板に第1の熱処理を行う工程と、前記第1の熱処理がされた炭化珪素基板に前記第1の熱処理より低温の第2の熱処理を行う工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】SiC基板上に形成されたデバイスに対して、低温の熱工程にて良好なオーミック特性を備える電極を実現する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、炭化珪素(SiC)で形成されるn型不純物領域上およびp型不純物領域上に金属シリサイド膜を形成し、n型不純物領域上の金属シリサイド膜中にリン(P)をイオン注入し、第1の熱処理を行い、p型不純物領域上の金属シリサイド膜中にアルミニウム(Al)をイオン注入し、第1の熱処理よりも低温の第2の熱処理を行う

(もっと読む)

半導体素子の製造方法

【課題】炭化シリコン基板に接するように、オーミック電極となるシリサイド層を形成するに際して、炭化シリコン基板由来の炭素が、オーミック電極内に拡散して表面に析出するのが抑えられ、オーミック電極の上に電極層を密着性良く形成することができる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明の半導体素子の製造方法は、炭化シリコン基板2のオーミック電極形成領域2aにシリコン層を形成する第1工程と、シリコン層2上に金属層8を形成する第2工程と、熱処理を行うことによって、シリコン層2に含まれるSiと金属層8の構成元素とを反応させ炭化シリコン基板2と接するシリサイド層41を形成する第3工程と、Siと反応せずに残存した金属層8を除去することによって、シリサイド層41を露出させる第4工程とによってオーミック電極4を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】 この実施の形態は、SiC半導体基板上に形成されたn型半導体領域とp型半導体領域を形成した半導体装置において、n型半導体領域とp型半導体領域の両領域にまたがって、単一の金属電極用いて同時コンタクトを形成することを目的としている。

【解決手段】 この実施の形態の半導体装置は、導電性材料を用いた第1の電極240に、導電型がp型の第1の炭化珪素(SiC)半導体部220と、導電型がn型の第2のSiC半導体部230とが接続され、前記第1の電極と前記第1の界面部において炭素(C)の面密度がピークになるようしている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SiC基板を用いて形成され、金属シリサイド膜と金属電極との密着性の向上する半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、炭化珪素と、炭化珪素上に形成され、第1の層、第1の層よりも低い炭素比率を有する第2の層を備える金属シリサイドと、金属シリサイド上に形成される金属電極を備え、第2の層が第1の層上に形成され、第2の層が金属電極に接し、第2の層中の金属シリサイドの平均粒径が、第1の層中の金属シリサイドの平均粒径よりも大きい。

(もっと読む)

61 - 80 / 1,500

[ Back to top ]