Fターム[4M104AA03]の内容

Fターム[4M104AA03]の下位に属するFターム

Fターム[4M104AA03]に分類される特許

1,481 - 1,500 / 1,500

炭化ケイ素上に耐久性接触を有するデバイスおよびその製造方法

ショットキーバリア炭化ケイ素デバイスは、レニウムショットキー金属接触を有している。レニウム接触(27)は250Åよりも厚く、2000Åから4000Åまでの間であり得る。ターミネーション構造は、ショットキー接触の周囲の環状領域をイオンミリングすることによって与えられる。  (もっと読む)

(もっと読む)

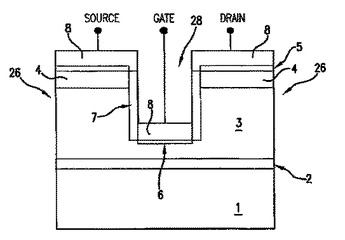

自己整列型炭化ケイ素半導体デバイスおよびそのデバイスの作成方法

電流安定性の改善された自己整列型炭化ケイ素パワーMESFETおよびそのデバイスの作成方法を記載する。このデバイスは、ゲート凹部により分離されたレイズドソースおよびドレイン領域を含み、低ゲートバイアスにおいてでさえ表面トラップ効果が低減されるため、電流安定性が改善される。このデバイスは自己整列型プロセスを用いて作成され得る。このプロセスでは、金属エッチマスクを用いて、nドープのSiCチャネル層上のn+ドープのSiC層を備えた基板がエッチングされてレイズドソースおよびドレイン領域が規定される。この金属エッチマスクがアニールされ、ソースおよびドレイン・オームコンタクトが形成される。単層または多層の誘電性フィルムが成長または堆積され異方性エッチングされる。蒸着または別の異方性堆積技術を用いて、ショットキーコンタクト層および最終金属層が堆積され、オプションとして、誘電性層の等方エッチングされる。  (もっと読む)

(もっと読む)

CMOSシリサイド金属ゲート集積化

本発明は、ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。本発明の集積化方式を用いて形成される各シリサイド金属ゲートは、シリサイド金属ゲートの寸法に関わりなく、同じシリサイド金属相および実質的に同じ高さを有する。本発明は、半導体構造物の表面全体にわたってポリSiゲート高さが実質的に同じであるシリサイド接点を有するCMOS構造物を形成するさまざまな方法も提供する。

(もっと読む)

(もっと読む)

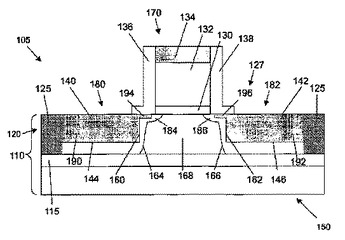

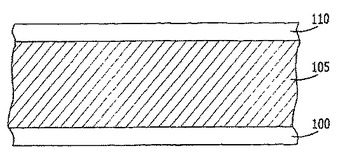

半導体装置及び半導体装置の製造方法

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

ショットキ・コンタクトを形成するために半導体上に導電性炭素材料を堆積するための方法、及び半導体コンタクト・デバイス

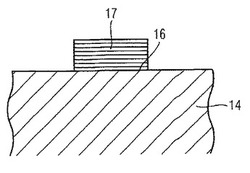

【課題】 本発明は、ショットキ・コンタクト(16)を形成するために半導体(14)上に導電性炭素材料(17)を堆積する方法に関する。

【解決手段】 本発明の方法は、半導体(14)をプロセス・チャンバ(10)内に導入するステップと、プロセス・チャンバ(10)の内部(10')を所定温度に加熱するス

テップと、プロセス・チャンバ(10)を第1所定圧力以下に減圧するステップと、プロセス・チャンバ(10)の内部(10')を第2所定温度に加熱するステップと、少なく

とも炭素を含むガス(12)を、第1所定圧力よりも高い第2所定圧力に達するまで導入するステップと、少なくとも炭素を含むガス(12)から、半導体(14)上に導電性炭素材料(17)を堆積することにより、半導体(14)上に堆積した炭素材料(17)がショットキ・コンタクト(16)を形成するステップを備えている。

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

炭化珪素半導体素子及びその製造方法

半導体素子の製造方法は、炭化珪素基板1上に形成された炭化珪素薄膜2内にイオンを注入する工程と、炭化珪素基板を減圧雰囲気で加熱することで炭化珪素基板の表面にカーボン層5を形成する工程と、カーボン層5を形成する工程より高い圧力で、且つ高い温度の雰囲気中で炭化珪素基板を活性化アニールする工程とを含んでいる。 (もっと読む)

バイポーラ接合トランジスタジオメトリ

【課題】

【解決手段】 バイポーラ接合トランジスタ(100)に関連する方法、装置、デバイスの実施例が記載されている。

(もっと読む)

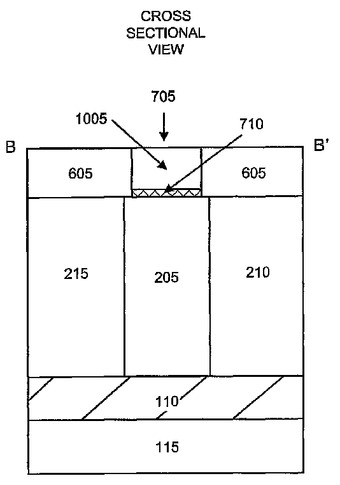

細型化されたボディを有する、狭いボディのダマシン・トライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の一端上にソース領域(210)、このフィン(205)の他端上にドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上に、第1パターンで、第1半導体材料のダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、第1パターンに対応する絶縁層(605)中にトレンチ(705)を残すように、第1半導体材料を除去するステップと、トレンチ(705)内に露出したフィン(205)の部分を細型化するするステップと、トレンチ(705)内に金属ゲート(1005)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

電極、その製造方法およびそれを用いた半導体素子

低接触抵抗を実現しつつ表面荒れの少ない電極が得られる技術を提供する。

半導体膜101の上部に設けられる電極であって、この半導体膜101の上部にこの半導体膜の側から順に積層された第一金属層102と第二金属層103とを有し、この第一金属膜102が、Alからなり、この第二金属膜103が、Nb、W、Fe、Hf、Re、TaおよびZrからなる群より選ばれる1種以上の金属からなることを特徴とする電極。

(もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

CMOS電界効果トランジスタを製造するための方法及び装置

【課題】 集積回路の製造におけるCMOS電界効果トランジスタを製造するための改善された方法、及び、トランジスタの金属ゲートの仕事関数を制御するための改善された方法を提供すること。

【解決手段】 トランジスタのゲート電極を含むポリシリコン材料を選択的にドープするステップと、完全にシリサイド化するステップとを含む、相補型金属酸化膜半導体(CMOS)電界効果トランジスタを製造する方法である。一実施形態において、シリサイド化する前に、ポリシリコンがアモルファス化される。更に別の実施形態において、シリサイド化が、低い基板温度で実行される。

(もっと読む)

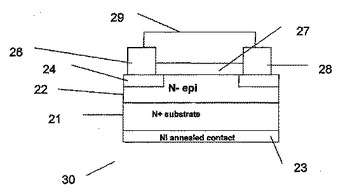

金属−炭化珪素オーミックコンタクトの局所的アニーリングおよびそのようにして形成された素子

炭化珪素(SiC)基板上に金属を形成し、この金属とSiC基板との界面部をアニーリングして、そこに金属−SiC材を形成し、SiC基板上のある箇所ではアニーリングされないようにして、そこには金属−SiC材が形成されないようにすることによって半導体素子のコンタクトを形成することができる。

(もっと読む)

(もっと読む)

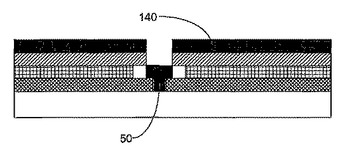

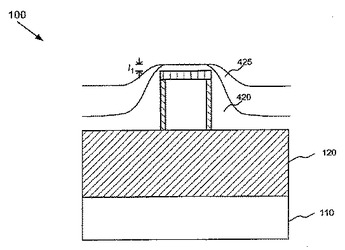

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

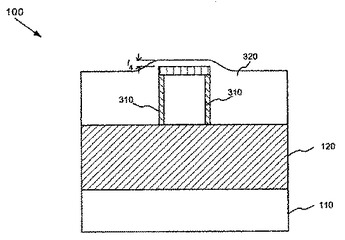

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

多端子カルコゲニドスイッチングデバイス

抵抗状態および導電状態間で切替可能なカルコゲニド材料を含む多端子電子スイッチングデバイスである。このデバイスは、第1の端子と、第2の端子と、制御端子を備える。制御端子に制御信号を印加することによって第1の端子および第2の端子間の前記カルコゲニド材料の導電性および/または第1の端子および第2の端子間の前記カルコゲニド材料を抵抗状態から導電状態へスイッチするのに必要な閾値電圧を変調する。このデバイスは回路またはネットワーク内で相互接続デバイスまたは信号付与デバイスとして用いることもできる。 (もっと読む)

半導体装置およびその製造方法

【課題】SiC基板を用い、オン抵抗のさらなる低減が図られた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、研磨等により厚さが200μm以下にされ、( 0 0 0−1)C面を上面とするSiC基板11aと、SiC基板11aの上面上に順に設けられた半導体からなるエピタキシャル成長層12,ショットキー電極14及び上部電極16と、Si面であるSiC基板11aの裏面上に順に設けられたオーミック電極15及び下部電極17とを備えている。SiC基板11aが従来の基板よりも薄いため、動作時のオン抵抗が大きく低減されている。

(もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

1,481 - 1,500 / 1,500

[ Back to top ]