Fターム[4M104AA04]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000)

Fターム[4M104AA04]の下位に属するFターム

GaAs (523)

Fターム[4M104AA04]に分類される特許

201 - 220 / 1,477

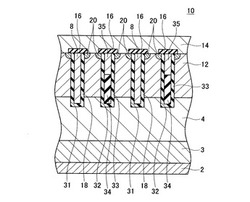

半導体装置

【課題】半導体装置の寄生容量成分を好適に調整する。

【解決手段】半導体装置10は、複数個のエミッタ領域20を備える。半導体層の表面から所定の深さまでの領域に形成されているボディ領域12を備える。ボディ領域12の下部に形成されているドリフト領域4を備える。ドリフト領域4の下部に形成されているコレクタ領域3を備える。各エミッタ領域20の表面からボディ領域12を貫通して伸びている第1トレンチ31を備える。第1トレンチ31の内面を覆っているゲート絶縁膜18を備える。第1トレンチ31内に収容されているゲート電極8を備える。隣接している第1トレンチ31間に形成され、ボディ領域12を貫通して伸びている第2トレンチ32を備える。第2トレンチ32の内面を覆っているトレンチ絶縁膜33を備える。第2トレンチ32内に収容されている導電層35を備える。導電層35がゲート電極8に電気的に接続されている。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

III族窒化物半導体素子及び窒化ガリウムエピタキシャル基板

【課題】有機金属気相成長炉において変動する成長条件の下で成長されるエピタキシャル膜の高純度化のための適切な指標を用いて、III族窒化物系化合物半導体を用いる電子デバイスを作製する方法を提供する。

【解決手段】工程S103において、n型GaN基板11上に窒化ガリウム系半導体層13を成長する。工程S104では、イエローバンド波長帯を含む波長領域および窒化ガリウム系半導体層のバンド端に対応するバンド端波長を含む波長領域のPLスペクトルを室温で測定する。工程S106では、イエローバンド波長帯およびバンド端波長のフォトルミネッセンススペクトル強度を基準値と比較することによってエピタキシャル基板を選別して、選別済みエピタキシャル基板E1を作製する。工程S107では、選別済みエピタキシャル基板13上に電子デバイスのための電極15を形成する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体デバイスおよび半導体デバイス製造方法

【課題】III族窒化物半導体では、p型不純物を高濃度にイオン注入すると、結晶品質が低下してしまう。結晶品質が低下するとオフ電流が増加して、電子デバイス特性が低下する可能性がある。このため、III族窒化物半導体では、p+層を形成することが困難であった。

【解決手段】III族窒化物半導体にドープされるとp型半導体になるp型不純物、および金属を有する合金からなる合金層と、合金層の下に接して形成され、III族窒化物半導体からなり、p型不純物が一部に拡散している半導体層と、合金層上に形成され、p型不純物の拡散係数が、半導体層より小さい拡散防止層と、を備える半導体デバイスを提供する。

(もっと読む)

パワー半導体素子

【課題】窒化物化合物半導体を用いたパワーダイオード、パワーMOSFET等のパワー

半導体素子について、クラックフリーで形成されて従来よりも厚い窒化物化合物半導体層

を使用して耐圧を向上することである。

【解決手段】シリコン基板1上に厚さ10μm以上の凸状に選択成長された窒化物化合物

半導体からなるキャリア移動層3と、キャリア移動層3上に形成された電極4とを有し、

1つのパワー半導体素子は1つのキャリア移動層3から構成されている。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

半導体発光素子及びその製造方法

【課題】電気的特性が良好で加工性が良好な電極を有する半導体発光素子及びその製造方法を提供する。

【解決手段】実施形態によれば、第1導電形の第1半導体層と、第2導電形の第2半導体層と、発光部と、第1導電層と、第2導電層と、を備えた半導体発光素子が提供される。前記発光部は、前記第1半導体層と前記第2半導体層との間に設けられる。前記第1導電層は、第1平均粒径を有する多結晶を含み、前記発光部から放出される光に対して透過性である。前記第2導電層は、前記第2半導体層と前記第1導電層との間において前記第2半導体層と前記第1導電層とに接し、前記第1平均粒径よりも小さく150ナノメートル以下の第2平均粒径を有する多結晶を含み、前記光に対して透過性である。

(もっと読む)

半導体装置の製造方法

【課題】半導体の表面の酸化物を含む不純物を、エッチングあるいは、他の層を積層する前に除去する。

【解決手段】第1の半導体層110の少なくとも一部に接し、第1の半導体層110に含まれる不純物の固溶度が、第1の半導体層110より高い第1の犠牲層を形成する第1犠牲層形成工程と、第1の犠牲層および第1の半導体層をアニールするアニール工程と、第1の犠牲層をウェットプロセスで除去する除去工程と、第1の半導体層の少なくとも一部を覆う絶縁層120を形成する工程および第1の半導体層の一部をエッチングする工程の少なくとも一の工程と、第1の半導体層に電気的に接続された電極層126を形成する電極形成工程とを備える。

(もっと読む)

半導体装置

【課題】 オン抵抗の増大を抑制しつつ、耐圧の低下を抑制する技術を提供する。

【解決手段】 ノーマリオフ型の半導体装置100は、ヘテロ接合を構成する半導体層16と、第1リセス部8と、第1リセス部8よりも浅い第2リセス部4と、ゲート部5を備えている。半導体層16は、第1半導体層12と、第1半導体層12上に設けられているとともに第1半導体層12よりもバンドギャップが広い第2半導体層14を有している。第2リセス部4は、第2半導体層14を貫通していない。第2リセス部4の下方に位置する第2チャネル部C2は、第1リセス部8の下方に位置する第1チャネル部C1よりも電流経路20の上流側に配置されている上流側第2チャネル部C2uを有する。

(もっと読む)

窒化物半導体装置、エピタキシャル基板および窒化ガリウム系エピタキシャル膜を形成する方法

【課題】ドナー濃度により該電子濃度を制御可能な高比抵抗の窒化ガリウム系半導体膜を含む窒化ガリウム系ショットキバリアダイオードを提供する。

【解決手段】ショットキーバリアダイオード41では、窒化ガリウム系エピタキシャル層45は、導電性を有するIII族窒化物基板45上に設けられている。窒化ガリウム系エピタキシャル層45には、ドナードーパント元素が添加されている。窒化ガリウム系エピタキシャル層45は2×1016cm−3未満の炭素濃度を有している。窒化ガリウム系エピタキシャル層45は1×108cm−2未満の転位密度を有する。窒化ガリウム系エピタキシャル層45は、5×1016cm−3未満の電子キャリア濃度を有する。電子キャリア濃度は、窒化ガリウム系エピタキシャル層45に添加されるドナードーパントによって変更可能である。

(もっと読む)

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

発光素子

【課題】 発光ムラを抑制し、より均一に発光することが可能な発光素子を提供することを課題とする。

【解決手段】 一実施形態に係る発光装置は、第1主面及び第2主面を有する半導体部と、第1主面側に設けられた第1電極と、第2主面側に設けられた第2電極と、を備える。第1電極は、第1主面の中心部を取り囲むように配置された3以上の外部接続部と、外部接続部から第1主面の中心部に向かって延伸する第1延伸部と、を備える。

(もっと読む)

半導体発光素子の製造方法

【課題】透明導電膜の被覆率を向上させた半導体発光素子の製造方法を提供する。

【解決手段】半導体発光素子10の製造方法では、発光部13を含む多層構造の半導体層11上に、発光部13から放射される光に対して透明な透明導電膜15を形成する。透明導電膜15の一部にマスク材20を形成する。マスク材20を用いて、透明導電膜15をウェットエッチングし、半導体層11を露出させる。マスク材20を用いて、露出した半導体層11を異方性エッチングし、発光部13を除去する。マスク材20を除去し、半導体層11であって活性層13が除去されて露出した部分上に第1電極16を形成し、透明導電膜15上に第2電極17を形成する。

(もっと読む)

p型GaN層に透光性接触部を形成する方法

【課題】p形GaN層に応用した場合に望ましい光学及び電気特性を呈する透光性接触部を形成する方法の提供。

【解決手段】オプトエレクトロニクス素子(10)のp形GaN層(20、30)の表面上に、金属酸化物からなる透光性接触部を成膜技術によって形成する。透光性接触部は、所望の金属を成膜前又は成膜中に酸化して形成する。金属酸化物は、NiO、II属金属酸化物、遷移金属酸化物等から選択されて成る。透光性接触部には、更に貴金属が添加され得る。

(もっと読む)

半導体装置およびその作製方法

【課題】バックゲート電極、しきい値電圧を制御するための回路、および不純物添加法を用いずにしきい値電圧が制御されたトランジスタを作製する。該トランジスタを用いて、電気特性が良好で、信頼性が高く、消費電力の小さい半導体装置を作製する。

【解決手段】組成の制御された酸化タングステン膜を有するゲート電極を用いる。酸化タングステン膜の成膜方法によって組成などを調整され、仕事関数を制御することができる。仕事関数の制御された酸化タングステン膜をゲート電極の一部に用いることでトランジスタのしきい値を制御できる。しきい値電圧が制御されたトランジスタを用いることで、電気特性が良好で、信頼性が高く、消費電力の小さい半導体装置を作製することができる。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

発光素子、発光素子ユニットおよび発光素子パッケージ

【課題】発光効率の向上を図ることができる発光素子、これを含む発光素子ユニットおよび発光素子ユニットを樹脂パッケージで覆った発光素子パッケージを提供すること。

【解決手段】発光素子1では、第1導電型半導体層3上に、発光層4、第2導電型半導体層5、透明電極層6、反射電極層7および絶縁層8が、この順で積層されていて、絶縁層8上には、第1電極層10と第2電極層12とが分離絶縁された状態で積層されている。発光素子1は、平面視において離散して配置されて絶縁層8から連続して反射電極層7、透明電極層6、第2導電型半導体層5および発光層4を貫通し、第1導電型半導体層3に到達する複数の絶縁管層9と、第1電極層10から連続し、絶縁層8および絶縁管層9を通って第1導電型半導体層3に接続された第1コンタクト11と、第2電極層12から連続し、絶縁層8を貫通して反射電極層7に接続された第2コンタクト13とを含む。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

201 - 220 / 1,477

[ Back to top ]