Fターム[4M104AA06]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | II−VI族 (146)

Fターム[4M104AA06]に分類される特許

1 - 20 / 146

化合物半導体装置及びその製造方法

パターン形成方法

【課題】微細なパターン、例えば、線幅が50μmよりも小さいパターンであっても高い精度でパターンを形成することができるパターン形成方法を提供する。

【解決手段】微細なパターンのパターン形成方法であって、基板上に形成された、親疎水性変換機能を有する第1の膜において、パターンが形成されるパターン形成領域を親疎水性に変化させる工程と、パターン形成領域に第2の膜を形成し、第2の膜が乾燥してパターンを形成する工程とを有する。第2の膜は、厚さが0.1μmになったときの粘度が3mPa・s以下である。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置の製造方法

【課題】X線検出用フォトダイオード等においては、初期結晶材料として、裏面側に高濃度の不純物がドープされた単結晶ウエハ等を使用する場合がある。このような場合、裏面側不純物の外方拡散によるクロスコンタミネーション等を防止するために、予め、ウエハの裏面に、酸化シリコン膜等の不純物外方拡散防止膜等を形成しておく等の対策が講じられる。しかし、裏面に不純物外方拡散防止膜を形成する際に、ウエハの表面を損傷する等の問題が有る。

【解決手段】本願発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

(もっと読む)

グラフェンを含む電極構造体及び電界効果トランジスタ

【課題】グラフェンを含む電極構造体及び電界効果トランジスタを提供する。

【解決手段】半導体層上のグラフェンと、グラフェン上の電極メタルと、を備え、該グラフェンは、半導体層と直接的に接触し、電極メタルは、グラフェンと直接的に接触する電極構造体である。半導体層は、シリコン、ゲルマニウム、シリコン・ゲルマニウム、III−V族半導体、及びII−VI族半導体を含むグループから選択された一つで形成される。グラフェンは、単層または二層のグラフェンで形成される。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

透明導電膜の形成方法

【課題】透明導電膜を低コストかつ高効率で作製することができ、基板の大面積化への対応も容易な透明導電膜の形成方法を提供する。

【解決手段】本発明の透明導電膜の形成方法は、酸化インジウム錫化合物からなるITO粒子を含有する導電性インク(Ink)を、その表面に所定のパターンのインク保持部が形成されたフレキソ印刷版11に保持させる工程と、このフレキソ印刷版11に、絶縁透光性基板10を密着させ、上記インク保持部に保持された導電性インクを基板10の所定位置に転写する工程と、この転写後に上記転写された導電性インクを加熱して、絶縁透光性基板10上に、所定パターンの透明導電膜を形成する工程と、を備える。

(もっと読む)

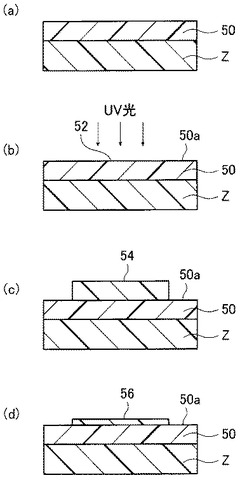

薄膜トランジスタの製造方法および薄膜トランジスタ

【課題】UV露光でも電気的絶縁性が損なわれず、表面濡れ性の変化を利用して印刷法でソース・ドレイン電極のパターニングが可能なゲート絶縁層を有する薄膜トランジスタの製造方法を提供する。

【解決手段】基板7上にゲート電極42およびゲート絶縁層2が順次形成され、該ゲート絶縁層が形成されたゲート電極上に適宜の間隔でソース電極5aおよびドレイン電極5bが対向配置され、該間隔を含む領域に半導体層6が形成された薄膜トランジスタを、活性水素基と反応可能なメラミン誘導体および活性水素基を有する樹脂を含有する溶液を塗布・焼成し、紫外線照射で表面濡れ性が可変のゲート絶縁層を形成し、紫外線照射で該ゲート絶縁層の露光部位を親水性域に変え、親水性域に電極材料含有溶液を印刷法で塗布・乾燥し、ソース電極及びドレイン電極を形成して薄膜トランジスタを形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】電圧−電流特性を改善した整流素子を用いたメモリセルを有する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1の配線と、前記第1の配線に交差する第2の配線と、前記第1及び第2の配線に設けられ、抵抗状態の変化に応じてデータを記憶するメモリ素子及び非オーミック素子を直列接続してなるメモリセルとを備え、前記非オーミック素子は、メタル層と、前記メタル層に接合された真性半導体層と、前記真性半導体層に接合された第1の不純物を含む不純物半導体層とを有することを特徴とする。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

半導体に直接電着する方法

【課題】 半導体の上に直接電着する方法を提供する。

【解決手段】 本開示は、半導体材料の少なくとも1つの表面上に金属又は金属合金を電着する方法を提供する。本発明の方法は、半導体材料の少なくとも1つの表面上の、電着された金属膜による完全な被覆を提供する。本開示の方法は、半導体材料を準備することを含む。半導体材料の少なくとも1つの表面上に、電着プロセスによって金属膜が付けられる。用いる電着プロセスには、最初に低電流密度を加え、所定の時間後に電流密度を高電流密度に変える電流波形が用いられる。

(もっと読む)

酸化物蒸着材と蒸着薄膜並びに太陽電池

【課題】酸化インジウムを主成分としセリウムを含むと共に表面から内部まで同一の組成を有する蒸着用酸化物タブレット(酸化物蒸着材)を提供し、かつこの酸化物蒸着材を用いて製造される蒸着薄膜とこの薄膜を電極に用いた太陽電池を提供すること。

【解決手段】この蒸着用酸化物タブレットは、酸化インジウムを主成分としセリウムを含み焼結後の表面研削加工がされていない焼結体により構成されており、焼結体表面から5μmの深さまでの表面層におけるセリウム含有量をCe/In原子数比(CompS)とし、焼結体全体におけるセリウム含有量の平均値をCe/In原子数比(CompA)とした場合、CompS/CompA=0.9〜1.1であることを特徴とする。また、蒸着薄膜は本発明の蒸着用酸化物タブレットを用いて成膜されていることを特徴とし、太陽電池は上記蒸着薄膜を電極に用いたことを特徴とする。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

1 - 20 / 146

[ Back to top ]