Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

761 - 766 / 766

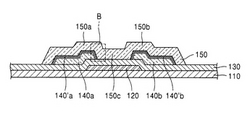

薄膜トランジスタ,その製造方法及び該薄膜トランジスタを備える平板ディスプレイ装置

【課題】 ソース/ドレイン電極間の電気的疎通を円滑にすることが可能な,薄膜トランジスタ,その製造方法及び該薄膜トランジスタを備える平板ディスプレイ装置を提供する。

【解決手段】 本発明に係る薄膜トランジスタは,基板110と,基板110上に形成されたゲート電極120と,ゲート電極120上に形成されるゲート絶縁層130と,ゲート電極120と絶縁されるようにゲート絶縁層130上に形成されるソース/ドレイン電極140a,140bと,ソース/ドレイン電極140a,140bと接するとともに,ゲート電極120と絶縁される有機半導体層150と,を含み,ソース/ドレイン電極140a,140bの少なくとも有機半導体層150と接する部分には酸化部140´a,140´bが設けられ,酸化部140´a,140´bを構成する物質は,有機半導体層150のHOMOエネルギー準位より大きい仕事関数を有する物質を含む。

(もっと読む)

半導体装置の作製方法

【課題】 より高精細なパターンの形成が可能な、液滴吐出法を用いた半導体装置の作製方法の提供を課題とする。

【解決手段】 パターンが形成されたモールドを絶縁膜に押し付けた状態で絶縁膜の硬化を行なった後、モールドを取り外すことで、絶縁膜に凹部を形成し、導電材料を有する液滴を吐出することにより、凹部に導電膜を形成し、導電膜を覆うようにゲート絶縁膜を形成し、ゲート絶縁膜上に島状の半導体膜を形成することを特徴とする半導体装置の作製方法。

(もっと読む)

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

本発明は、基板110、基板上に形成されているゲート電極124、基板及びゲート電極を覆っているゲート絶縁膜140、ゲート絶縁膜上に形成されているソース電極173及びドレイン電極175、ゲート絶縁膜、ソース電極、及びドレイン電極上に形成されている半導体層150、半導体層、ソース電極、ドレイン電極及びゲート絶縁膜を覆っている保護膜180を含み、ゲート絶縁膜及び保護膜はパリレンからなる薄膜トランジスタ表示板を提供する。  (もっと読む)

(もっと読む)

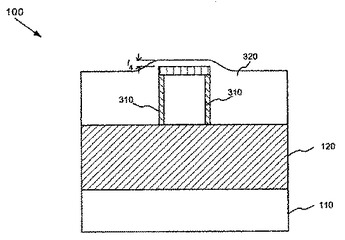

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

761 - 766 / 766

[ Back to top ]