Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

81 - 100 / 766

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】集積回路の動作速度の向上に有利な技術を提供する。

【解決手段】n型トランジスタおよびp型トランジスタがシリコンの(551)面に形成された半導体装置において、前記n型トランジスタの拡散領域に接触するシリサイド層の厚さが前記p型トランジスタの拡散領域に接触するシリサイド層の厚さよりも薄い。

(もっと読む)

スパッタリングターゲット、半導体装置および半導体装置の製造方法

【課題】Cu配線層に含まれるCuの周囲への拡散を抑制すると共に密着性および動作特性に優れた半導体装置およびその製造方法、並びに、その半導体装置の製造に用いるスパッタリングターゲットを提供する。

【解決手段】実施の形態に係るスパッタリングターゲットは、1.5原子%以上5.0原子%以下のMnと、(Mgの原子%)/(Mnの原子%)で示される比率が0.3以上2.1以下となるMgと、10wtppm以下のCと、2wtppm以下のO2と、を含むCu合金を用いて形成される。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

半導体装置

【課題】しきい値電圧の経時的な低下を抑制でき、またアルミ配線による絶縁膜の腐食やAlスパイクに起因するゲート・ソース間の短絡を防止できる半導体装置を提供する。

【解決手段】半導体装置のMOSFETセルは、ポリシリコンのゲート電極6およびn-ドリフト層2の上部に形成されたn+ソース領域4を備える。ゲート電極6上は層間絶縁膜7によって覆われており、Alのソース電極101は、層間絶縁膜7上に延在する。またゲート電極6にはAlのゲートパッド102が接続される。ソース電極101と層間絶縁膜7との間、並びにゲートパッド102とゲート電極6との間のそれぞれに、Alの拡散を抑制するバリアメタル層99が配設される。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

透明導電膜の形成方法

【課題】透明導電膜を低コストかつ高効率で作製することができ、基板の大面積化への対応も容易な透明導電膜の形成方法を提供する。

【解決手段】本発明の透明導電膜の形成方法は、酸化インジウム錫化合物からなるITO粒子を含有する導電性インク(Ink)を、その表面に所定のパターンのインク保持部が形成されたフレキソ印刷版11に保持させる工程と、このフレキソ印刷版11に、絶縁透光性基板10を密着させ、上記インク保持部に保持された導電性インクを基板10の所定位置に転写する工程と、この転写後に上記転写された導電性インクを加熱して、絶縁透光性基板10上に、所定パターンの透明導電膜を形成する工程と、を備える。

(もっと読む)

有機発光ディスプレイ装置及びその製造方法

【課題】製造工程が単純化され、パッド部での抵抗均一度が向上して輝度が向上した有機発光ディスプレイ装置及びその製造方法を提供する。

【解決手段】活性層212、ゲート下部電極214とゲート上部電極215とを含むゲート電極21、ソース電極217a及びドレイン電極217bを含む薄膜トランジスタ;薄膜トランジスタと電気的に連結され、ゲート下部電極と同一層に、同一物質で形成された画素電極414、発光層を含む中間層419、対向電極420からなる有機発光素子;ゲート下部電極と同一層に、同一物質で形成される第1パッド電極514;第1パッド電極の少なくとも一部上に形成され、ゲート上部電極と同一層に、同一物質で形成される第2パッド電極515;第2パッド電極の少なくとも一部とコンタクトするように形成され、ソース電極及びドレイン電極と同一層に、同一物質で形成される第3パッド電極517;を含む有機発光ディスプレイ装置。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】半導体層の側壁がデータ線の側壁に対して突出することを最小化する。

【解決手段】ゲート絶縁膜140上に第1、第2非晶質シリコン層150,160、データ金属層170形成段階と、上部データ金属層170r上に第1感光膜パターン50形成段階と、第1感光膜パターンをマスクとしてデータ金属層170をエッチングして、第1下部データ金属パターン及び側壁が突出した突出部を含む第1上部データ金属パターン形成段階と、第1感光膜パターンをマスクとして第1及び第2非晶質シリコン層をエッチングして、非晶質シリコン層パターン形成段階と、第2感光膜パターンをマスクとして第1上部データ金属パターンをエッチングして、第2上部データ金属パターン形成段階と、第2感光膜パターンをマスクとして第1下部データ金属パターン、非晶質シリコン層パターンをエッチングして、半導体、データ線等を形成する段階、とを含む。

(もっと読む)

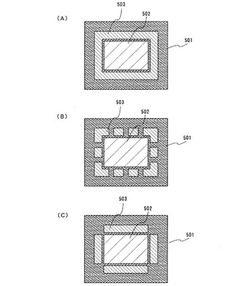

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置及び表示装置

【課題】高融点メタルバリア層を有していなくても、高温熱処理後の電気特性を良好にする技術を提供することを目的とする。

【解決手段】半導体装置は、透明絶縁性基板1上に形成されたゲート電極2と、ゲート電極2上にゲート絶縁膜6を介して順次に形成されたSi半導体能動膜7と、n型の導電型を有するオーミック低抵抗Si膜8とを含む半導体層51と、半導体層51と直接接合された、少なくともアルミニウム(Al)を含むソース・ドレイン電極9,10とを備える。半導体層51は、平面視においてゲート電極2の外周よりも内側に形成され、Si半導体能動膜7の側面とソース・ドレイン電極9,10との界面近傍である第1領域には、少なくとも窒素(N)が含まれる。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構造の半導体装置あるいはその作製方法を提供することを課題とする。例えば、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図ることを課題とする。

【解決手段】トランジスタの信頼性向上を図るため、電界集中を緩和するバッファ層をドレイン電極層(またはソース電極層)と、酸化物半導体層との間に設け、バッファ層の端部をドレイン電極層(またはソース電極層)の側面から突出させた断面形状とする。バッファ層は、単層又は複数の層からなる積層で構成し、例えば窒素を含むIn−Ga−Zn−O膜、窒素を含むIn−Sn−O膜、SiOxを含むIn−Sn−O膜などを用いる。

(もっと読む)

81 - 100 / 766

[ Back to top ]