Fターム[4M104AA08]の内容

Fターム[4M104AA08]に分類される特許

161 - 180 / 766

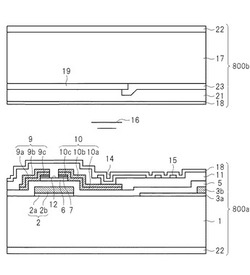

表示装置及びその製造方法

【課題】ソース・ドレイン電極に、剥離やストレスマイグレーションによるボイドが発生するのを抑制する。

【解決手段】複数の薄膜トランジスタが配列された基板を有する表示装置であって、薄膜トランジスタは、半導体層6と、半導体層6上に形成されるコンタクト層7と、コンタクト層7上に形成されるソース電極10及びドレイン電極9とを有し、ソース電極10およびドレイン電極9は、コンタクト層7の上側に形成される第1の導電層9a,10aと、第1の導電層9a,10aの上側に形成される第2の導電層9b,10bとを有し、第2導電層9b,10bは、第1添加元素と、銅とを含有する銅合金層であり、前記第1添加元素は、ジルコニウム、チタン、銀、インジウム、金、錫、クロム、ケイ素から選ばれた少なくとも1種類の元素である、ことを特徴とする表示装置。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるソース電極6i(5i)と不純物半導体膜6g(5g)の積層体の一部が、チャネル保護膜6d(5d)における膜厚の厚い一端側に重なる構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】活性層―電極間の寄生抵抗に起因する素子特性のばらつきの少ないIGZO系電界効果型トランジスタを製造する。

【解決手段】基板B上に、IGZO系アモルファス酸化物からなる半導体層11、ソース電極22、ドレイン電極23、ゲート電極21およびゲート絶縁膜31とを備えてなる電界効果型トランジスタ1の製造方法において、半導体層11上にIGZO系アモルファス酸化物層20をスパッタ成膜により成膜し、その後アニール処理を行って、ソース電極22およびドレイン電極23の少なくとも半導体層11に接触する面側を構成する導電層を形成する。スパッタ成膜における背圧は1×10−5Pa未満とし、アニール処理におけるアニール温度を100℃以上、300℃以下とする。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるチャネル保護膜6d(5d)に鋭角なエッジ部6p(5p)を設けて、そのエッジ部6d(5d)でソース電極6i(5i)と不純物半導体膜6g(5g)の積層体を破断するようにして、その積層体がチャネル保護膜6d(5d)の上面に重ならない構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

表示装置および表示装置の製造方法

【課題】Cu合金をソース・ドレイン電極に用いたTFTにおいて、コンタクト膜に対して酸化処理を施す場合であっても、良好なオン特性を維持する表示装置を提供することを目的とする。

【解決手段】半導体層4と、銅と1種類の添加元素とを含む銅合金層を有するソース電極10およびドレイン電極9と、ソース電極10及びドレイン電極9のそれぞれの電極と半導体層4との間に形成されるコンタクト膜5と、それぞれの電極とコンタクト膜5との間に形成される酸化物膜8と、を含む薄膜トランジスタ基板を有する表示装置であって、コンタクト膜5は、不純物とシリコンとを含み、酸化物膜8は、シリコン、不純物および酸素を含むとともに、酸化物膜8における不純物濃度がコンタクト膜5における不純物濃度よりも低い、ことを特徴とする表示装置。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含む半導体装置である。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】Cu系合金配線膜を半導体層と直接接続しても接触抵抗率が低く、かつ密着性に優れた薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタの半導体層33と、Cu合金層28b、29bとを有する薄膜トランジスタ基板において、前記半導体層33と前記Cu合金層28b、29bとの間に、酸素含有層28a、29aを含んでおり、前記酸素含有層28a、29aを構成する酸素の一部若しくは全部は、前記薄膜トランジスタの前記半導体層33のSiと結合しており、前記Cu合金層28b、29bは、合金元素としてX(Xは、Mn、Ni、Zn、およびMgよりなる群から選ばれる少なくとも1種)を合計で2原子%以上20原子%以下含有し、前記Cu合金層28b、29bは、前記酸素含有層28a、29aを介して前記薄膜トランジスタの前記半導体層33と接続していることを特徴とする薄膜トランジスタ基板である。

(もっと読む)

成膜装置及びメンテナンス方法

【課題】シリコン膜を成膜する際に生じるポリシランを含む副生成物を、非成膜時に迅速かつ簡便に処理することが可能な成膜装置を提供すること。

【解決手段】本発明の成膜装置は、CVD法を用いて、真空中で基板Wにシリコン膜を成膜する成膜室11と、前記成膜室内にオゾン含有ガスを導入可能な第一オゾン含有ガス供給手段180と、を少なくとも備え、シリコン膜の成膜を終了した状態にある前記成膜室内に前記オゾン含有ガスを導入することにより、前記シリコン膜の成膜中に生成したポリシランを含む副生成物を酸化させること、を特徴とする。

(もっと読む)

表示装置およびその製造方法

【課題】ゲート絶縁層内に拡散する汚染元素によってトランジスタ特性が低下するのを防止した薄膜トランジスタを有する表示装置、および、その製造方法を提供することを目的とする。

【解決手段】基板101の上側に積層された半導体層104と、半導体層104の上側に積層されるゲート電極106と半導体層104とゲート電極106との間に積層されるゲート絶縁層105と、ソース電極112およびドレイン電極111と、を含む薄膜トランジスタを有する表示装置であって、ソース電極112およびドレイン電極111の少なくとも一方は、ゲート絶縁層105の上側に形成されて、ゲート絶縁層105に形成されるコンタクトホール109を介して半導体層に接続され、コンタクトホール109の側壁には、窒素化合物を含む側壁膜110が形成される、ことを特徴とする表示装置。

(もっと読む)

太陽電池に全面裏面電界および銀バスバーを付与するための方法

背面接点銀バスバーを太陽電池のアルミニウム裏面電界(BSF)に付与するための方法が提供される。当該方法は、前面および裏面を有する太陽電池基板を準備する工程と;この太陽電池基板の裏面の上に全面アルミニウム裏打ち層を印刷する工程と;印刷されたアルミニウム裏打ち層を乾燥して、全面アルミニウム層を得る工程と;銀バスバーが所望される領域の全面アルミニウム層の上に剥離ペーストを印刷し乾燥する工程と;太陽電池基板の前面の上に前面接点銀ペーストを印刷し乾燥して、前面グリッド電極を生成する工程と;太陽電池の前面および裏面を同時焼成し冷却する工程であって、焼成の間に当該剥離ペーストは、アルミニウム層の中の過剰のアルミニウム粉末を濡らし、そして、太陽電池の冷却の間にこの剥離ペーストは、収縮し、固化し、過剰のアルミニウム粉末とともに剥離して、空いた領域を有する全面アルミニウムBSFを残す工程と;BSFの空いた領域に背面接点銀ペーストを印刷し、乾燥し、焼成して、銀バスバーを得る工程とを含む。 (もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】表示装置の形成方法は、基板上に下地絶縁層を設け、その層上に配線パターンに沿った第1の銅拡散防止層を設ける。次に、その第1の銅拡散防止層上面に第1の銅拡散防止層の幅より僅かに狭い銅配線層を積層し、銅配線層の全表面を覆うように、第2の金属拡散防止層を設ける方法である。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

酸化物蒸着材と蒸着薄膜並びに太陽電池

【課題】酸化インジウムを主成分としセリウムを含むと共に表面から内部まで同一の組成を有する蒸着用酸化物タブレット(酸化物蒸着材)を提供し、かつこの酸化物蒸着材を用いて製造される蒸着薄膜とこの薄膜を電極に用いた太陽電池を提供すること。

【解決手段】この蒸着用酸化物タブレットは、酸化インジウムを主成分としセリウムを含み焼結後の表面研削加工がされていない焼結体により構成されており、焼結体表面から5μmの深さまでの表面層におけるセリウム含有量をCe/In原子数比(CompS)とし、焼結体全体におけるセリウム含有量の平均値をCe/In原子数比(CompA)とした場合、CompS/CompA=0.9〜1.1であることを特徴とする。また、蒸着薄膜は本発明の蒸着用酸化物タブレットを用いて成膜されていることを特徴とし、太陽電池は上記蒸着薄膜を電極に用いたことを特徴とする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】

同一の材料の積層構造を有するゲート配線及びソース・ドレイン配線を備えた液晶表示装置をより低コストで製造可能な液晶表示装置及びその製造方法を提供すること。

【解決手段】

同一の材料の積層構造を有するゲート配線及びソース・ドレイン配線を備えた液晶表示装置の製造方法において、該ゲート配線と該ソース・ドレイン配線とをフッ酸と酸化剤とを含むエッチング液でウェットエッチング処理を行うと共に、該エッチング液のフッ酸の濃度が該ゲート配線と該ソース・ドレイン配線とでは異なることを特徴とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたpチャネル型トランジスタを提供することを目的の一とする。また、酸化物半導体を用いたnチャネル型トランジスタとpチャネル型トランジスタとのCMOS(相補型金属酸化物半導体)構造を提供することを目的の一とする。

【解決手段】ゲート電極層と、ゲート絶縁層と、酸化物半導体層と、前記酸化物半導体層と接するソース電極層及びドレイン電極層とを含み、前記酸化物半導体層に用いる酸化物半導体の電子親和力をχ(eV)、バンドギャップをEg(eV)とすると、前記ソース電極層及び前記ドレイン電極層に用いる導電体の仕事関数φmは、φm>χ+Eg/2を満たし、かつ、χ+Eg−φmで表される正孔に対する障壁φBPは0.25eV未満である、酸化物半導体を用いたpチャネル型トランジスタを提供する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

161 - 180 / 766

[ Back to top ]