Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

2,001 - 2,020 / 2,474

半導体装置およびその製造方法

【課題】 MISFETを有する半導体装置の性能を向上させる。

【解決手段】 半導体基板1のp型ウエル7上にゲート絶縁膜8を介してゲート電極15が形成され、p型ウエル7にはソース・ドレインとしてのn+型半導体領域35が形成されている。ゲート電極15の両側壁上にはオフセットスペーサ23を介してサイドウォールスペーサ33が形成され、サイドウォールスペーサ33の側面34aには凹部34bが形成されている。ゲート電極15上およびn+型半導体領域35上に金属シリサイド膜43a,43bが形成され、金属シリサイド膜43aはゲート電極15の上面上だけでなく、サイドウォールスペーサ33の側面34aうちの凹部34bよりも上部の領域上にも延在している。金属シリサイド膜43bは、n+型半導体領域35の上に形成されている。

(もっと読む)

ナノ・スケール・チャネルトランジスタのためのブロックコンタクトアーキテクチャ

ナノスケールチャネルデバイスのコンタクトアーキテクチャは、複数の並列半導体本体を有するデバイスのソースまたはドレイン領域に結合されかつその間に延びるコンタクト構造を有する。コンタクト構造は、サブリソグラフィックピッチを有する並列半導体本体と接触することができる。 (もっと読む)

コンタクト絶縁層および異なる特性を有するシリサイド領域を形成するための技法

NチャネルトランジスタおよびPチャネルトランジスタのための金属シリサイドを別個に形成できるようにする技法が提供され、同時に、トランジスタタイプ毎に歪み誘発機構も別個に設けられる。このようにして、NMOSトランジスタ(120、220)のチャネル領域まで短い距離を有するコバルトシリサイド(130、230)を設けることができ、その一方で、Pチャネルトランジスタ(140、240)は、Nチャネルトランジスタ(120、220)の特性に過度に影響を及ぼすか、またはその特性を劣化させることなく、高導電性のニッケルシリサイド(150、250)を収容することができる。  (もっと読む)

(もっと読む)

マイクロエンボス加工による電子装置の製造方法

【課題】マイクロエンボス加工による電子装置の製造方法を提供する。

【解決手段】電子装置の基板10上での形成方法であり、基板10をエンボス加工する工程と、基板をくぼみでない部分11が第1の材料60の溶液をはじくように表面処理する工程と、エンボス加工によって形成された基板10上のくぼみ12に第1の材料60の溶液を堆積する工程と、を含む。その後、第1の材料が基板の表面と同一平面となるよう、基板はアニール処理される。くぼみ中の第1の材料60はその後、たとえば後続のTFTの形成におけるソースおよびドレインとして使用できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、耐熱性に優れた半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 第1の発明の半導体装置は、第1導電型の半導体層と、第1導電型の半導体層上に形成された第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成され、Ruからなる第1の金属の結晶粒および第1の金属の結晶粒の粒界に偏析したW、Ni、Mo、Rh、Pd、Re、IrおよびPtからなる群から選ばれる第2の金属を有する第1のゲート電極と、第1のゲート絶縁膜をゲート長方向に挟む第1導電型の半導体層に形成された第1のソース・ドレイン領域と、を備えることを特徴とする。

(もっと読む)

膜パターンの形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 バンクに撥液化処理を行う際の、機能膜へのダメージを解消した膜パターンの形成方法と、これによって得られた膜パターンを備えた半導体装置、電気光学装置、及び電子機器を提供する。

【解決手段】 基板Pに設けられたゲート絶縁膜28(機能膜)上に機能液を配置して膜パターンを形成する方法である。基板Pにゲート絶縁膜28を設け、ゲート絶縁膜28上にポリシラザン液、ポリシラン液またはポリシロキサン液のいずれかを塗布し乾燥してバンク膜31を形成する。そして、マスクMを用いてバンク膜31を選択的に露光し、バンク膜31に撥液処理を施す。バンク膜31を現像処理することでゲート絶縁膜28を露出させ、パターン形成領域を区画するバンクを形成する。パターン形成領域に前記機能液を配置し、膜パターンを形成する。少なくとも、バンク膜31に撥液処理を施す工程は、バンク膜31を現像処理しバンクを形成する工程より前の工程で行う。

(もっと読む)

半導体装置、演算増幅器および半導体装置の製造方法

【課題】 ソース/ドレイン接合における接合リーク電流を抑制しつつ、バックゲートバイアスをトランジスタごとに個別に制御する。

【解決手段】 不純物のイオン注入を半導体基板11に局所的に行い、ウェル12a、12bを半導体基板11に形成してから、半導体基板11の表面に絶縁層13を形成し、単結晶半導体層23を介して半導体基板11上の絶縁層13上に半導体基板21を貼り合わせた後、多孔質層22をエッチング除去することにより、多孔質層22を境界として半導体基板21を単結晶半導体層23から剥離する。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネル形成領域に異なる応力を発声させる膜を互いに積層形成した半導体装置において、当該膜のエッジ部形状に起因するボイドが形成された場合であっても、隣り合うコンタクトがショートすることがない半導体装置及びその製造方法を提供する。

【解決手段】 コンタクト開口部を形成した後に絶縁材料を堆積して、コンタクト開口部に表出したボイド開口部を塞ぐ。これにより、当該ボイドに導電性材料が侵入することを防止し、隣り合うコンタクトがショートすることを防止する。

(もっと読む)

複数の熱処理によって自己整列されたシリサイド膜を形成する方法

【課題】複数の熱処理によって自己整列されたシリサイド膜を形成する方法を提供する。

【解決手段】基板上に金属膜を形成し、第1の温度で第1の熱処理を遂行して、金属膜上に金属シリサイド膜を形成し、第1の熱処理とインサイチュウとして第1の温度より低い第2の温度で第2の熱処理を遂行することを含む。これにより、欠陥がない金属シリサイド膜を形成でき、金属シリサイド膜を採用する半導体素子の電気的特性を安定的に改善させることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SWTを採用しつつ、リソグラフィのピッチ幅よりも狭いピッチ幅を有し、かつ均一な幅を有するFinを形成することができる半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、リソグラフィで形成可能な最小ピッチ幅よりも狭いピッチ幅で配列され半導体材料から成る複数のFin50を絶縁層4上に形成し、複数のFinの側壁にゲート絶縁膜60を形成し、Finの配列方向に延び、Finとは電気的に絶縁され、かつFinに共通のゲート電極709を、ゲート絶縁膜上に形成し、ゲート電極をマスクとして用いて該ゲート電極の両側に延在するFinの部分に不純物を注入することによりソース・ドレイン層100を形成し、Finのゲート電極を挟んだ両側に絶縁膜を介して導電体材料を堆積することにより、複数のFinを接続することを具備する。

(もっと読む)

有機薄膜トランジスタ及びアクティブマトリックス表示装置

【課題】インクジェット印刷あるいはディスペンサ印刷を用いた数μmの高精細なソース・ドレイン電極パターンが形成された有機薄膜トランジスタ及び有機薄膜トランジスタをアクティブ素子として用いるアクティブマトリックス表示装置を提供する。

【解決手段】基板、ゲート電極、ゲート絶縁膜、ソース電極、ドレイン電極、及び有機半導体層を有する有機薄膜トランジスタにおいて、エネルギー付与により表面エネルギーを変化させた前記ゲート絶縁膜の電極形成領域上に、少なくとも1つ以上の角部のいずれかに鈍角形状を有する電極形成領域を設定し、該電極形成領域に前記形状と略同一の鈍角形状を有するソース電極及び/又はドレイン電極を形成したことを特徴とする有機薄膜トランジスタを主たる構成にする。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上に形成されたフィン型構造のpチャネルおよびnチャネル電界効果トランジスタにおいてそれぞれ適する電流駆動力を得る。

【解決手段】pMIS形成領域の半導体層に第1間隔を有して隣接する複数の第1フィン4pを形成し、nMIS形成領域の半導体層に第1間隔よりも狭い第2間隔を有して隣接する複数の第2フィン4nを形成し、第1フィン4pおよび第2フィン4nの表面にそれぞれゲート絶縁膜5を形成し、第1フィン4pおよび第2フィン4nの両側にそれぞれゲート電極6を形成する。また、ゲート電極6でnMIS形成領域の隣接する第2フィン4n間を完全に埋め込み、ゲート電極6およびその上層に形成される絶縁膜でpMIS形成領域の隣接する第1フィン4p間を埋め込む。

(もっと読む)

電気光学表示装置およびその製造方法

【課題】TFT構造部の製造工程を簡略化するとともに、ソース・ドレイン電極の材質を限定せずとも、TFTチャネル部となる半導体層の膜厚を正確に制御することで、表示ムラを防止した電気光学表示装置を提供する。

【解決手段】活性領域層AR上から、画素電極30の下方の透明絶縁性基板1の上方にかけて延在するようにドレイン電極26が配設されている。ソース電極24およびソース配線25は、その端面が半導体膜6の何れの端面よりも後退した位置となるように配設され、活性領域層AR上のドレイン電極26の端面も、半導体膜6のほぼ平行な関係にある端面よりも後退した位置となるように配設されている。

(もっと読む)

完全空乏型SOI−MOSトランジスタの製造方法

【課題】スループットを向上させ、短チャネル効果を抑制しソースドレイン抵抗の低い完全空乏型SOI−MOSトランジスタの製造方法を提供する。

【解決手段】SOI層を形成し、酸化膜、窒化膜を形成した後、窒化膜をマスクとして酸化処理を施して窒化膜以外に酸化膜を形成し分離部を形成する工程と、ポリシリコン層(A)を形成し酸化膜を形成する工程と、ゲート部以外をエッチングしてゲートを作製する工程と、ポリシリコン層(A)側面にサイドウォールを形成し、ポリシリコン層(B)を形成する工程と、分離部のポリシリコン層(B)のポリシリコンを除去する工程と、ゲート上のポリシリコン層(B)の一部が露出するように、レジストを除去する工程と、露出したポリシリコン層(B)のポリシリコンを除去する工程と、レジストを除去し、ゲート上部の酸化膜を除去する工程と、を順次含む完全空乏型SOI−MOSトランジスタの製造方法。

(もっと読む)

短チャンネル半導体素子製造

蓄積モードのマルチゲート・トランジスタ素子(1100)の構成が開示される。本素子は、短チャンネル効果、特にhiが軽減され、チャンネル領域、拡張領域、及び/又は、ソース(1104)/ドレイン(1106)領域に更に1つのタイプのドーパント材料が埋め込まれて、不所望の漏れ電流をもたらすチャンネル領域内の、導電パスの設定、及び、電子の蓄積を緩和するように構成される。 (もっと読む)

薄膜トランジスタの製造方法および液晶表示装置の製造方法

【課題】ゲート電極およびレジストを精度良くエッチングできる薄膜トランジスタの製造方法を提供する。

【解決手段】レジスト後退法で金属層41を後退させる前に、レジスト42および金属層41をマスクとして活性層6のソース領域12およびドレイン領域13となる部分に不純物をドーピングする。レジスト42および金属層41をRIEにてエッチングして金属層41をゲート電極17とする際に、レジスト42中の不純物から放出されるプラズマ発光強度の変化を測定する。プラズマ発光強度が略一定となった時点を、レジスト42および金属層41のRIEによるエッチングの終点とする。金属層41およびレジスト42を精度良くエッチングできる。

(もっと読む)

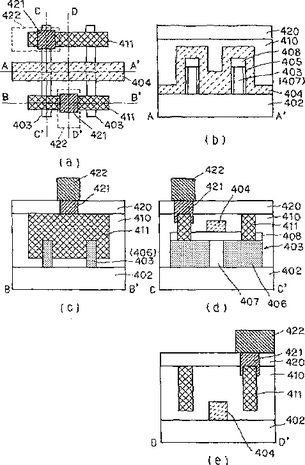

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

薄膜トランジスタ及び半導体デバイスの作製方法

【課題】液滴吐出法などのマスクレスプロセスを用いて円形薄膜トランジスタを作製することにより、工程の簡略化、作製時間の短縮、及び作製費用の低減を図ると共に、従来よりもその形状が制御された円形薄膜トランジスタの作製方法を提供することを目的とする。

【解決手段】液滴吐出法等のマスクレスプロセスを用いて、基板上に同心円状の薄膜を積層し、円形の電極を有する円形薄膜トランジスタを形成する。また、液滴吐出法等のマスクレスプロセスを用いて、基板上に同心円状の薄膜を積層し、円形の半導体層を有する円形薄膜トランジスタを形成してもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。

(もっと読む)

エッチング液、エッチング液及びその結果構造物を用いた導電性配線を含む薄膜トランジスタ基板の製造方法

【課題】銀(Ag)配線用エッチング液を提供すること。また、エッチング液を利用する銀(Ag)配線形成方法を提供すること。さらに、エッチング液を利用する薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】本発明により、エッチング液、これを用いた配線形成方法及び薄膜トランジスタ基板の製造方法が提供される。エッチング液は下記化学式1で表示される物質、酢酸アンモニウム及び超純水を含む。

(化学式1)

M(OH)XLY

(ただし、前記式でMはZn、Sn、Cr、Al、Ba、Fe、Ti、SiまたはBであり、Xは2または3であり、LはH2O、NH3、CN、COR、NH2Rであり、Yは0、1、2または3であり、Rはアルキル基である。)

(もっと読む)

2,001 - 2,020 / 2,474

[ Back to top ]