Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,961 - 2,965 / 2,965

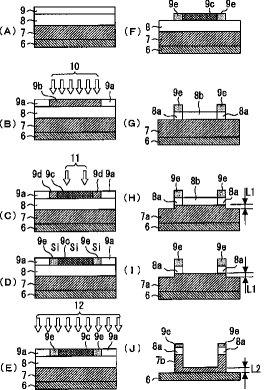

微細レジストパターン、微細パターンの形成方法及び半導体装置

【課題】 半導体装置の表面にさらに微細なパターンを形成することができる微細レジストパターン、微細パターンの形成方法及び半導体装置を提供する。

【解決手段】 基板6上に、特定の元素を含む特定のガスに接触して特定の元素と結合し所定のエッチングガスに対する耐性が強化される性質を有するレジスト層9を形成する工程と、レジスト層9に第一の露光10を行い、第一の露光領域9bと第一の非露光領域9aとを形成する工程と、第一の露光領域9bに対して第二の露光11を行い、第二の露光領域9cと第三の露光領域9dとを形成する工程と、レジスト層9を特定のガスにさらして第三の露光領域9dのみを特定の元素と結合させる工程と、第二の露光領域9cと第一の非露光領域9aとをエッチングにより除去し第三の露光領域9eからなるレジストパターンを形成する工程とを備えた。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

電極構造体の形成方法及び半導体装置の製造方法

【課題】 ポリメタル構造を有するゲート電極において、ポリシリコン膜と高融点金属膜との間の界面抵抗を低くする。

【解決手段】 半導体基板10上にゲート絶縁膜11を介してポリシリコン膜12を堆積した後、該ポリシリコン膜12の上に、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16からなるバリア膜を形成する。バリア膜の上にタングステン膜18を堆積して、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及びタングステン膜18からなる電極構造体を形成した後、該電極構造体に対して750℃以上の熱処理を施す。このようにすると、第1の窒化チタン膜14中の窒素がチタン膜15及びポリシリコン膜12に拡散して、ポリシリコン膜12とタングステン膜18との間に新たな窒化チタン膜19が形成されると共に、ポリシリコン膜12の表面に窒化シリコンからなり厚さの小さい反応層20が形成される。

(もっと読む)

2,961 - 2,965 / 2,965

[ Back to top ]