Fターム[4M104BB03]の内容

Fターム[4M104BB03]に分類される特許

1 - 20 / 270

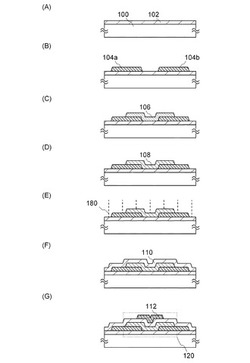

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル移動度の低下およびパンチスルーの発生が抑制され、かつ効率的に製造することができる半導体装置およびその製造方法を提供する。

【解決手段】MOSFET1は、{0001}面に対するオフ角が50°以上65°以下である側壁面20Aを有するトレンチ20が形成された基板10と、酸化膜30と、ゲート電極40とを備えている。基板10は、ソース領域14と、ボディ領域13と、ソース領域14との間にボディ領域13を挟むように形成されたドリフト領域12とを含む。ソース領域14およびボディ領域13はイオン注入により形成されている。ボディ領域13においてソース領域14とドリフト領域12との間に挟まれた内部領域13Aの主表面10Aに垂直な方向における厚みは、1μm以下である。ボディ領域13の不純物濃度は、3×1017cm−3以上である。

(もっと読む)

半導体装置の製造方法

【課題】電極と半導体基板が良好にオーミック接合している半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の電極形成面に、単原子の金属イオンを注入するイオン注入工程と、金属イオンが注入された半導体基板をアニール処理して半導体基板にシリサイド層を形成するアニール工程と、アニール工程の後に、半導体基板の電極形成面に電極を形成する電極形成工程とを備えている。

(もっと読む)

スーパージャンクション構造を有する半導体装置

【課題】高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供する。

【解決手段】n−型半導体層(第1導電型の半導体層)114と、活性領域R1に形成された複数の柱状埋込層118と、活性領域R1に形成されたショットキーバリアメタル層(第1電極層)132と、耐圧領域R2に形成された複数のガードリング層(環状柱状埋込層)124と、耐圧領域R2及び周辺領域R3に形成された絶縁層130とを備える、スーパージャンクション構造を有する半導体装置であって、周辺領域R3に形成された第2ガードリング層(第2環状柱状埋込層)136と、周辺領域R3に形成された環状導電層142とをさらに備える、スーパージャンクション構造を有する半導体装置100。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク不良の発生を抑制でき、かつ薄型基板を用いることができる半導体装置およびその製造方法を提供する。

【解決手段】半導体チップ30を、半導体基板35の表層部に形成された第1導電型層34と、第1導電型層34の表面に形成されたゲート絶縁膜37と、ゲート絶縁膜37上に形成されたゲート電極38と、半導体基板35の主表面35a上に配置され、主表面35aの一部を露出させるコンタクトホール42が形成された層間絶縁膜41と、層間絶縁膜41上に配置され、コンタクトホール42を介して半導体基板35と接続されるアルミニウムを有する材料で構成される上部電極43と、上部電極43上に形成されたニッケルを有する材料で構成されるメッキ膜44と、半導体基板35の裏面35bに形成された下部電極46とを有する構成とする。そして、上部電極43のうちコンタクトホール42に形成されている部分の膜厚tを2μm以上にする。

(もっと読む)

表示装置用配線構造

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、配線構造全体の電気抵抗(配線抵抗)も低く抑えられており、更にフッ酸耐性にも優れた表示装置用配線構造を提供する。

【解決手段】本発明の表示装置用配線構造は、基板側から順に、Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含むAl合金の第1層と;Ti、Mo、Al、Ta、Nb、Re、Zr、W、V、Hf、およびCrよりなる群(Y群)から選択される少なくとも一種の元素の窒化物、またはAl合金の窒化物の第2層と、が積層された表層構造を有する。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体素子

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半

導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを

課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレ

イン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート

絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は

側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供

する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トラ

ンジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体

に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ

<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン

電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができ

る。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

1 - 20 / 270

[ Back to top ]