Fターム[4M104BB04]の内容

Fターム[4M104BB04]の下位に属するFターム

Fターム[4M104BB04]に分類される特許

141 - 160 / 3,070

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

半導体装置の製造方法

【課題】電解めっき法によるCu膜の確実に析出させる。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

(もっと読む)

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

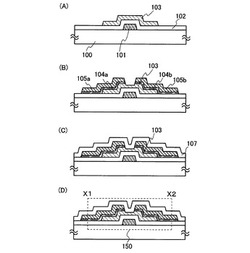

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

電極およびそれを含む電子素子

【課題】優秀な導電性及び大きい仕事関数を有する電極及びそれを含んだ電子素子を提供する。

【解決手段】グラフェン含有層と、前記グラフェン含有層上に形成される仕事関数傾斜層と、を含み、前記仕事関数傾斜層は、前記グラフェン含有層と接触する第1面、及び前記第1面に対向する第2面を有する単一層であり、前記仕事関数傾斜層の仕事関数は、前記第1面から前記第2面に向かう方向に沿って漸進的に増大する電極。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子

【課題】大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子を提供する。

【解決手段】0.1S/cm以上の電気伝導度を有する導電性物質および低表面エネルギー物質を含み、第1面と、前記第1面に対向する第2面と、を有し、前記第2面の低表面エネルギー物質の濃度が、前記第1面の低表面エネルギー物質の濃度より高く、前記第2面の仕事関数が5.0eV以上であり、かつ前記第2面の電気伝導度が1S/cm以上である大きい仕事関数および高い電気伝導度を有する電極、を具備した電子素子である。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体素子および電子機器

【課題】有機半導体層の上面の層の形状不良を抑えることが可能な半導体素子およびこれを備えた電子機器を提供する。

【解決手段】有機半導体層と、有機半導体層の上面に設けられた層とを有し、この層の外形線は、有機半導体層の外形線よりも内側にある半導体素子。この半導体素子を備えた電子機器。

(もっと読む)

Cu合金膜および表示装置

【課題】酸化物半導体層を用いた表示装置において、保護膜形成時のプラズマ処理におけるCu配線の酸化を有効に防止し得る技術を提供する。

【解決手段】基板1の上に、基板側から順に、薄膜トランジスタの半導体層4と、電極に用いられるCu合金膜5と、保護膜6と、を備えており、半導体層は酸化物半導体からなる。Cu合金膜5は、基板側から順に、第一層(X)5aと第二層(Z)5bを含む積層構造を有し、第一層(X)は、純Cu、またはCuを主成分とするCu合金であって第二層(Z)よりも電気抵抗率の低いCu合金からなり、第二層(Z)は、Zn、Ni、Ti、Al、Mg、Ca、W、Nb、希土類元素、Ge、およびMnよりなる群から選択される少なくとも1種の元素を合計で2〜20原子%含むCu−Z合金からなり、第二層(Z)の少なくとも一部は、前記保護膜と直接接続されている。

(もっと読む)

窒化物半導体発光素子の製造方法

【課題】工程数が少なく生産性を向上する窒化物半導体発光素子の製造方法を提供する。

【解決手段】まず、パッド電極層形成工程S11で、窒化物半導体発光素子構造上に、n側パッド電極およびp側パッド電極となるパッド電極層を形成し、レジストパターン形成工程S12で、パッド電極層上に、n側パッド電極およびp側パッド電極を形成する領域を被覆するレジストパターンを形成する。次に、パッド電極層エッチング工程S13で、このレジストパターンをマスクとして、パッド電極層をエッチングしてn側パッド電極およびp側パッド電極を形成する。続いて、このレジストパターンを除去せずに、保護層形成工程S14で、窒化物半導体発光素子構造の表面およびレジストパターン上に絶縁性の保護層を形成した後に、レジストパターン除去工程S15で、レジストパターンを除去する。

(もっと読む)

有機薄膜トランジスタ及び有機薄膜トランジスタの製造方法

【課題】有機半導体層の形成位置について、別途精密な制御を必要とすることなく、高精細なパターニングが行われた有機半導体層を有する有機薄膜トランジスタ及びその製造方法を提供することにある。

【解決手段】ソース電極1、ドレイン電極2、ゲート電極3、有機半導体層4及びゲート絶縁膜5を備え前記ソース電極1及び前記ドレイン電極2の表面エネルギーが、いずれも30mN/m以下であることを特徴とする。

(もっと読む)

半導体装置

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置を提供することを目的

の一とする。

【解決手段】13族元素および酸素を含む第1の絶縁膜と、第1の絶縁膜と一部が接する

酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と

、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜とゲート電極の間の、酸化物

半導体膜と一部が接する第2の絶縁膜と、を有する半導体装置である。また、13族元素

および酸素を含む第1の絶縁膜には、化学量論的組成比より酸素が多い領域が含まれる構

成とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】ゲート絶縁層と、ゲート絶縁層の一方の面に接する第1のゲート電極と、ゲート絶縁層の他方の面に接し、第1のゲート電極と重畳する領域に設けられた酸化物半導体層と、酸化物半導体層と接するソース電極、ドレイン電極、及び酸化物絶縁層と、の積層構造を有し、酸化物半導体層の窒素濃度は2×1019atoms/cm3以下であり、ソース電極及びドレイン電極は、タングステン、白金及びモリブデンのいずれか一又は複数を含む半導体装置を提供する。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

半導体上の銅のめっき

【課題】前面電流トラックを形成したドープ半導体ウェハの銅めっきに関する改善された銅めっき方法を提供する。

【解決手段】前面、裏面およびPN接合を含む半導体を提供し、下層を含む導電トラックのパターンを前記前面が含み、かつ前記裏面が金属接点を含んでおり;前記半導体を一価銅めっき組成物と接触させ;並びに導電トラックの下層上に銅をめっきする。

(もっと読む)

141 - 160 / 3,070

[ Back to top ]