Fターム[4M104BB13]の内容

Fターム[4M104BB13]の下位に属するFターム

Fターム[4M104BB13]に分類される特許

21 - 40 / 1,522

半導体装置

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良

を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設

けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い

表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度

が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギ

ャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キ

ャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノ

ーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】チャネル長方向の一方の側面においてソース電極層と接し、チャネル長方向の他方の側面においてドレイン電極層と接する酸化物半導体層を含むトランジスタとすることでソース電極層とドレイン電極層の間の電界を緩和して、短チャネル効果を抑制する。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、インジウムを含む酸化物半導体膜、ゲート電極層と重畳する酸化物半導体膜上に接する絶縁層が順に積層され、酸化物半導体膜及び絶縁層に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、絶縁層表面における塩素濃度を1×1019/cm3以下とし、かつインジウム濃度を2×1019/cm3以下とする。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

マグネトロンスパッタ装置及びマグネトロンスパッタ方法

【課題】成膜速度の面内均一性を確保しながら、成膜効率を向上させ、ターゲットの使用効率を向上させること。

【解決手段】真空容器2内に載置されたウエハ10に対向するようにターゲット31を配置し、このターゲット31の背面側にマグネット配列体5を設ける。このマグネット配列体5は、マグネット61,62がマトリックス状に配列された内側マグネット群54と、この内側マグネット群54の周囲に設けられ、電子の飛び出しを阻止するリターン用のマグネット53とを備えている。これによりターゲット31の直下にカスプ磁界による電子のドリフトに基づいて高密度のプラズマが発生し、またエロージョンの面内均一性が高くなる。このためターゲット31とウエハ10とを接近させてスパッタを行うことができ、成膜速度の面内均一性を確保しながら、成膜効率を向上させることができる上、ターゲットの使用効率が高くなる。

(もっと読む)

トップゲート型アクティブマトリックス基板、およびその製造方法

【課題】データ配線が銀や銀合金により形成されており、またデータ配線に、ゲート絶縁層によって被覆されておらずむき出しとなっている部分があった場合でも、当該むき出しとなっている部分でマイグレーション現象が生じることがないトップゲート型アクティブマトリックスを提供する。

【解決手段】基材と、前記基材上に直接または間接的に形成された、ソース電極、ドレイン電極、半導体層、ゲート絶縁層、ゲート電極、層間絶縁層、画素電極、および前記ソース電極と接続したデータ配線と、を有するトップゲート型アクティブマトリックス基板において、前記ソース電極と前記データ配線をともに銀または銀合金で形成し、前記ゲート電極を銀または銀合金以外で形成し、前記データ配線においてむき出しとなっている部分をゲート電極と同じ材質からなる被覆層によって被覆する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】バリア層(バリアメタル)13を覆うようにライナー層14が形成されている。ライナー層14は、Ni(ニッケル)から構成される。ライナー層14は、このライナー層14の内側に形成されるCu(銅)からなる導電体15に対する濡れ性を高め、かつ、溝部12の内側の平滑性を高める。

(もっと読む)

スイッチング素子

【課題】逆ピエゾ効果が効果的に抑制され、オフ時の高電界状態であっても、ゲート電極近傍でクラックの発生が抑止されたスイッチング素子を提供する。

【解決手段】スイッチング素子1は、電子走行層13と、電子走行層13の上面に形成され、バンドギャップが電子走行層13より大きく電子走行層13とヘテロ接合する電子供給層14と、ソース電極15とドレイン電極16と、ソース電極15とドレイン電極16の間に配置されたゲート電極17とを備え、ゲート電極の下方に、電子供給層14に替えて、逆ピエゾ抑制層20を配置してなる。逆ピエゾ抑制層20は、ヘテロ接合よりも格子不整合が緩和された状態で電子走行層13と接合するように、その組成等が調整されており、ゲート電極17との接触領域A2のドレイン電極16側境界B4を跨ぐように配置される。

(もっと読む)

半導体装置とその製造方法

【課題】信頼性の高いヘテロ接合を有するノーマリオフ型の半導体装置を提供すること。

【解決手段】半導体装置1は金属膜22を備えている。金属膜22は、ゲート部30とドレイン電極24及び/又はソース電極26の間の半導体積層体10の表面の少なくとも一部に設けられている。金属膜22は、半導体積層体10の表面部に窒素空孔を形成することが可能な材料である。

(もっと読む)

光透過型金属電極、電子装置及び光学素子

【課題】低い電気抵抗を維持しながら、広い波長範囲で十分な透明性を得ることができる金属電極、半導体発光素子及び光学素子を提供する。

【解決手段】実施形態に係る金属電極は、部材の主面上に設けられ、金属細線と、前記金属細線により形成される複数の開口部と、を有する金属層である。金属細線は、前記主面に対して平行な第1方向に沿う複数の第1直線部と、前記主面に対して平行で前記第1方向と交差する前記第1方向とは異なる方向に沿う複数の直線部と、を有する。前記複数の第1直線部の前記第1方向に沿う長さの最大値及び前記複数の第2直線部の前記第1方向とは異なる方向に沿う長さの最大値は、可視光の波長以下である。前記主面の法線方向にみた前記金属層の面積に対する前記法線方向にみた前記金属細線の面積の比は、20パーセントを超え80パーセント以下である。

(もっと読む)

光透過型金属電極、電子装置及び光学素子

【課題】シート抵抗が低く、広い波長範囲で高い透過率を有する光透過型金属電極、電子装置及び光学素子を提供する。

【解決手段】実施形態によれば、複数の第1金属線と、複数の第2金属線と、を含む光透過型金属電極が提供される。複数の第1金属線は、第1方向に沿って並ぶ。第1金属線は、第1方向と交差する第2方向に沿って延びる。複数の第2金属線は、第1方向と第2方向を含む平面に対して平行で第1方向と交差する第3方向に沿って並び、第1金属線と接触する。第2金属線は、その平面に対して平行で第3方向と交差する第4方向に沿って延びる。複数の第1金属線の第1方向における中心どうしの第1距離は、可視光を含む波長帯の最短の波長以下である。複数の第2金属線の第3方向における中心どうしの第2距離は、波長帯の最長の波長を超える。第1金属線と第2金属線の厚さは、最短の波長以下である。

(もっと読む)

窒化物系発光素子及びその製造方法

【課題】窒化物系発光素子及びその製造方法を提供する。

【解決手段】窒素物系発光素子は、基板110、n型クラッド層130、活性層140、

p型クラッド層150、格子セル層160及びオーミック接触層が順次に積層された構造

よりなっている。また格子セル層160は導電性を有する素材で30μm以下の大きさを

有する粒子型セルがオーミック接触層内に埋め込まれて、相互離隔されて形成されている

発光素子である。このような窒素物系発光素子とその製造方法は、p型クラッド層とのオ

ーミック接触特性が改善されているため発光効率及び素子寿命を向上させ、かつウェーハ

成長後の活性化工程を省略できて、製造工程を単純化させうる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

酸化物半導体層、半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

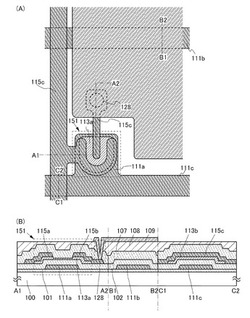

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

21 - 40 / 1,522

[ Back to top ]