Fターム[4M104BB28]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | WSi (591)

Fターム[4M104BB28]に分類される特許

1 - 20 / 591

Cu層形成方法及び半導体装置の製造方法

半導体装置

半導体装置の製造方法

【課題】SiC半導体基板の裏面電極は、低コンタクト抵抗を実現するために、ニッケル等のシリサイド形成用メタル膜を堆積後、PDAとして摂氏1000度程度の熱処理を必要とする。この熱処理を通常の熱処理やRTAで実行する場合には、ウエハの表面側がアルミニウム等の融点を超えるため、アルミニウム膜等の形成前に実施しなければならないという制約がある。また、既存の紫外線レーザを用いたレーザアニールでは、コンタクト抵抗を十分に下げられないという問題がある。

【解決手段】本願の一つの発明は、SiC基板の表面側にアルミニウム系メタル膜が形成された状態で、裏面にシリサイド形成用メタル膜を成膜し、この裏面に対してレーザビームによってシリサイド化処理を実行する半導体装置の製造方法であって、このレーザビームを、前記シリサイド形成用メタル膜を実質的に透過しない波長域に属する可視光とするものである。

(もっと読む)

半導体装置の製造方法

【課題】電極と半導体基板が良好にオーミック接合している半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の電極形成面に、単原子の金属イオンを注入するイオン注入工程と、金属イオンが注入された半導体基板をアニール処理して半導体基板にシリサイド層を形成するアニール工程と、アニール工程の後に、半導体基板の電極形成面に電極を形成する電極形成工程とを備えている。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

熱処理方法

【課題】シリサイドの横方向への異常成長を防止しつつ、シリサイド形成を行うことができる熱処理方法を提供する。

【解決手段】半導体ウェハーWのソース・ドレイン領域にシリコンなどのイオンを注入し、そのイオン注入領域150を非晶質化する。非晶質化されたイオン注入領域150にニッケル膜158を成膜する。ニッケル膜158が成膜された半導体ウェハーWにフラッシュランプから第1照射を行ってその表面温度を予備加熱温度T1から目標温度T2にまで1ミリ秒以上20ミリ秒以下にて昇温する。続いて、フラッシュランプから第2照射を行って半導体ウェハーWの表面温度を目標温度T2から±25℃以内の範囲内に1ミリ秒以上100ミリ秒以下維持する。これにより、ニッケルシリサイドが縦方向に優先的に成長する。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】ショットキー電極形成前に酸洗浄を行ってもp型オーミック電極がその酸に曝されることなく、p型オーミック電極とショットキー電極との電気的接続が良好な炭化珪素半導体装置及びその製造方法を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素基板1と、基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に形成された複数のp型不純物領域3と、p型不純物領域3上の一部に形成されたp型オーミック電極4と、p型不純物領域3上の一部に、p型オーミック電極4を覆うように形成された耐酸性のバリアメタル層5と、バリアメタル層5、p型不純物領域3、及びn型炭化珪素層2上に形成されたショットキー電極6と、ショットキー電極6上に形成された第1の電極と、炭化珪素基板1のn型炭化珪素層が形成されていない側に形成された第2の電極と、を備えたことを特徴とする。

(もっと読む)

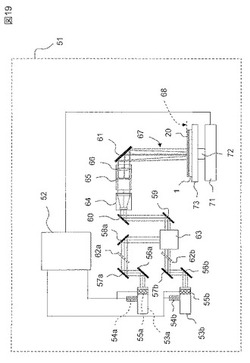

デバイスの製造方法および製造装置

【課題】スパッタリング法により、被処理基板の一面に形成されたチタンナイトライド膜上にタングステンシリサイド膜を形成する際に、タングステンシリサイド膜に含ませるシリコン原子の割合を微細制御することを可能にする、デバイスの製造方法を提供する。

【解決手段】被処理基板の一面103aに、チタンナイトライド膜109、タングステンシリサイド膜110、タングステン膜111の順に堆積してなるデバイスの製造方法であって、タングステンシリサイド膜110をスパッタリング法により形成する際に、タングステン原子からなるターゲット102と、シリコン原子を含むプロセスガスを少なくとも用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化が容易な半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、第1導電形の半導体基板の上面に複数本のトレンチを形成する工程と、前記トレンチの内面上にゲート絶縁膜を形成する工程と、前記トレンチ内の下部にゲート電極を埋め込む工程と、前記トレンチ内の上部に絶縁部材を埋め込む工程と、前記半導体基板の上層部を除去することにより、前記半導体基板の上面から前記絶縁部材を突出させる工程と、前記突出した絶縁部材を覆うように、マスク膜を形成する工程と、前記マスク膜における前記絶縁部材の側面上に形成された部分をマスクとして、前記半導体基板に不純物を注入することにより、第2導電形のキャリア排出層を形成する工程と、を備える。

(もっと読む)

半導体装置

【課題】RCATの電流駆動能力を向上させることが可能な半導体装置を提供する。

【解決手段】半導体基板11は、ゲート溝13を有している。拡散層12は、ゲート溝13の上部に対応する半導体基板11の表面領域に形成されている。ゲート絶縁膜14は、ゲート溝の壁面に形成されている。ゲート電極15は、ゲート溝13の内部及びゲート溝13の外部に形成されている。圧縮応力を有する膜16は、ゲート溝13の外部のゲート電極15の全面に形成されている。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

【課題】貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタを作製する。

【解決手段】ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートラストプロセスの工程数を削減しつつ、所望の信頼性及び特性が得られるメタルゲート電極を備えたMISFETを実現できるようにする。

【解決手段】各ゲート溝の少なくとも底面上にゲート絶縁膜112及び保護膜113が順次形成されている。一方のゲート溝内の保護膜113の上には第1の金属含有膜114a及び第2の金属含有膜114bが順次形成されており、他方のゲート溝内の保護膜113の上には第2の金属含有膜114bが形成されている。一方のゲート溝内の保護膜113の厚さと比べて、他方のゲート溝内の保護膜113の厚さは薄い。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

1 - 20 / 591

[ Back to top ]