Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

201 - 220 / 333

薄膜トランジスタ装置およびその製造方法、ならびに、該薄膜トランジスタ装置を備えた表示装置

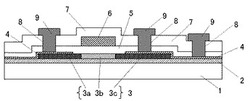

【課題】 TFTの層間絶縁膜の下層にあって膜厚が薄いポリシリコン膜からなるソース領域やドレイン領域に到達するコンタクトホールを開口する際に、ポリシリコン膜を突き抜けてしまうとコンタクトホール底部にポリシリコン膜が残存しないため、接続抵抗が増大してしまう。また、保持容量の下部電極がポリシリコン膜からなる場合、該膜を低抵抗化するために高ドーズのドーピングプロセスが必要であるため、生産性を著しく低下させていた。

【解決手段】 基板1上で島状に形成されたポリシリコン膜3におけるソース領域3aおよびドレイン領域3bの少なくとも一部を覆う金属膜4を形成してから、ゲート絶縁膜5、ゲート電極6、層間絶縁膜7を形成し、金属膜4の上部にコンタクトホール8を開口する。さらに、金属膜4を形成する際に、保持容量の位置まで延在させることにより、金属膜4を保持容量の下部電極となす。

(もっと読む)

二重金属ゲートを含む半導体構造及びその製造方法(二重金属ゲートの自己整合集積化)

【課題】二重金属ゲートを含む半導体構造及びその製造方法を提供する。

【解決手段】少なくとも1つのn型電界効果トランジスタ(nFET)および少なくとも1つのp型電界効果トランジスタ(pFET)を含み、その両方がそれぞれnFETの性質およびpFETの性質を有する金属ゲートを含み、上部多結晶シリコンゲート電極を含まない半導体構造を提供する。本発明は、このような半導体構造を製造する方法も提供する。

(もっと読む)

CMOS半導体素子とその製造方法

【課題】窒素含有量の異なる金属をゲート電極材として用いたCMOSトランジスタにおいて、ゲート電極の抵抗を低減しCMOSトランジスタの微細化を実現する。

【解決手段】半導体基板上のNMOS領域とPMOS領域にゲート絶縁膜を介してそれぞれ窒素含有量の異なる下層金属層とその上に積層された上層金属層から成る2層構成のゲート電極が形成されたCMOS半導体素子であって、前記下層金属層を前記上層金属層よりゲート長方向の長さを短くする。

(もっと読む)

金属含有化合物、その製造方法、金属含有薄膜及びその形成方法

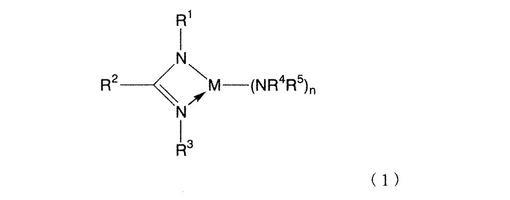

【課題】CVD法、ALD法の原料として熱安定性と気化特性を有する化合物、その製造方法、その化合物を用いた薄膜及び形成方法を提供する。

【解決手段】一般式(1)で表される化合物を原料とした金属含有薄膜を形成する。 (もっと読む)

(もっと読む)

チタン錯体、それらの製造方法、チタン含有薄膜及びそれらの形成方法

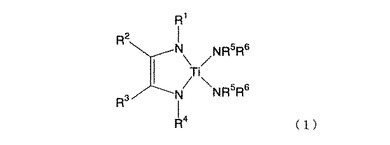

【課題】新規なチタン錯体の製法、それらを用いたチタン含有薄膜の形成方法の提供。

【解決手段】ジイミンと金属リチウムとを反応させ、次いでテトラキスアミド錯体を反応させることにより一般式(1)で表されるチタン錯体を製造し、そのチタン錯体を原料としてチタン含有薄膜を形成させる。 (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを用いた半導体装置の製造方法において、RPTの短縮、ゲート寸法の加工精度の向上を図る半導体装置の製造方法を提供する。

【解決手段】半導体基板上にダミーゲートを形成する工程、前記ダミーゲートをマスクとして前記半導体基板に不純物を導入して、ソース・ドレイン拡散領域を形成する工程、前記ダミーゲートの周囲に絶縁膜を形成する工程、前記ダミーゲートを除去して開口部を形成する工程、及び前記開口部にゲート絶縁膜を介してゲート電極を形成する工程を具備する方法である。前記ダミーゲートは、前記半導体基板上に、炭素と水素との原子比(C/H)が1以上であり、かつ炭素の絶対量が50%以上である炭素過剰の組成のポリマーを塗布してポリマー膜を形成する工程、前記ポリマー膜上にフォトレジストパターンを形成する工程、及び前記フォトレジストパターンを前記ポリマー膜に転写する工程により形成されることを特徴とする。

(もっと読む)

半導体装置のデュアルゲート構造物及びその形成方法

【課題】高誘電膜を含むCMOSトランジスタの形成に適合した構造を有するデュアルゲート構造物及びその形成方法を提供する。

【解決手段】デュアルゲート構造物は、第1及び第2領域が区分される基板と、前記第1領域の基板上に形成され、金属酸化膜、第1仕事関数を有する金属物質からなる第1金属パターン、シリコン拡散防止膜パターン、及びシリコンを含む導電膜パターンが積層された第1ゲート構造物と、前記第2領域の基板上に形成され、金属酸化膜、前記金属物質及びシリコン元素を含み前記第1仕事関数より低い第2仕事関数を有する第2金属パターン、及び前記シリコンを含む導電膜パターンが積層された第2ゲート構造物と、を含む。前記デュアルゲート構造物は各領域に形成されるゲート電極が同一の金属物質からなるので前記金属物質の一部を除去しなくてもよいので前記除去工程の際発生する金属酸化膜の損傷を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物拡散領域の侵食等を生ぜしめることなく接合リーク電流の増大を抑制して不純物拡散領域の抵抗値を十分に低減し、更なる微細化・高集積化を実現して、低消費電力で高速動作を可能とする。

【解決手段】STI素子分離構造5を形成する際に、これをその上部が基板1面から通常のSTI法の場合よりも突出するように形成し、ゲート電極の形成部位にダミー電極パターン7を形成する。空隙部11に整合してソース/ドレイン8を形成した後、Wで空隙部11を充填してなる導電層14を形成し、ダミー電極パターン7を除去してゲート絶縁膜21及びゲート電極22を形成する。

(もっと読む)

金属−窒化ケイ素、酸化ケイ素、又は酸窒化ケイ素のALD/CVD用のTi、Ta、Hf、Zr及び関連する金属のケイ素アミド

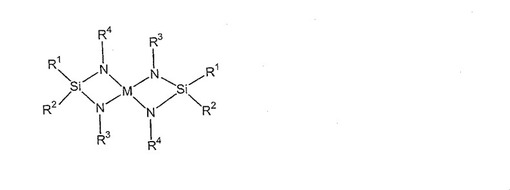

【課題】金属窒化ケイ素ベース膜、金属酸化ケイ素又は金属酸窒化ケイ素ベース膜を形成させるために好適な前駆体の提供。

【解決手段】次の構造により表される有機金属錯体。

(式中、Mは、元素周期表の4族から選択される金属であり、そしてR1〜4は、同一又は異なって、ジアルキルアミド、ジフルオロアルキルアミド、水素、アルキル、アルコキシ、フルオロアルキル及びアルコキシ、脂環式、並びにアリールから成る群から選択されることができるが、但しR1及びR2が、ジアルキルアミド、ジフルオロアルキルアミド、アルコキシ、フルオロアルキル及びアルコキシである場合には、それらは連結して環を形成することができる。)。関連化合物もまた、開示されている。上記錯体を用いるCVD及びALD堆積法がまた、含まれる。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲート電極をメタルの凝集なく仕事関数変調により形成する。

【解決手段】本発明の例に関わる半導体装置の製造方法は、半導体基板100上にゲート絶縁層102を形成する工程と、ゲート絶縁層102上に第1メタル層103を形成する工程と、第1メタル層103上に第2メタル層104を形成する工程と、第2メタル層104上に第2メタル層104よりも高い融点を持つ材料からなるキャップ層105を形成する工程と、熱処理により第2メタル層104内の元素をゲート絶縁層102と第1メタル層103との界面に析出させて析出層107を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】高精度なパターン形成を行なうことが可能となる半導体装置の製造方法を提供する。

【解決手段】基板1の主表面上に絶縁膜7を形成する。絶縁膜7上に導電膜8を形成し、該導電膜8上に下層レジスト膜9、中間層10、反射防止膜11および上層レジスト膜を形成する。この上層レジスト膜の高さを検出することで露光時の焦点位置を検出する。露光時の焦点位置を検出するに際し、焦点検出光を上層レジスト膜に照射する。焦点位置を検出した後、上層レジスト膜を露光、現像し、レジストパターン12aを形成する。レジストパターン12aをマスクとして中間層10と反射防止膜11をパターニングし、下層レジスト膜9を現像する。これらのパターンをマスクとして導電膜8をエッチングし、ゲート電極を形成する。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】仕事関数の調整された複数ゲート電極を形成するための製造方法を提供する。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイスは、第1のパラメータを有する少なくとも2つの第1のゲート電極120を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極120を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、たとえメタル膜を加工したとしても、当該メタル膜の下に形成されている絶縁膜の膜減りを抑制することができる、半導体装置の製造方法を提供する。

【解決手段】 本発明に係わる半導体装置の製造方法では、ゲート絶縁膜3上に、ゲート電極を構成するメタル膜4を形成する。その後、当該メタル膜4を加工する際に、所定の薬液を用いたウエットエッチング処理により、当該メタル膜4の一部を除去する。

(もっと読む)

方法および半導体構造(非酸素カルコゲン不活性化ステップを用いて製作されたGe系半導体構造)

【課題】FETおよびMOSコンデンサなどのGe系半導体デバイスを得ることができる方法および構造を提供すること。

【解決手段】具体的には、本発明は、その表面が非酸素カルコゲンに富んだGe含有材料(層またはウェーハ)の上部またはその内部あるいはその両方に誘電体層と導電材料を含むスタックを含む半導体デバイスを形成する方法を提供する。非酸素カルコゲンに富んだ界面を設けることによって、誘電体成長時およびその後の望ましくない界面化合物の形成が抑制され、界面トラップの密度が低下する。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】炭素濃度を十分に高くすることが可能な高融点金属の金属化合物膜よりなる薄膜を形成することが可能な成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器4内に、高融点金属有機材料ガスと窒素含有ガスとを供給して被処理体の表面に高融点金属の金属化合物膜よりなる薄膜を形成する成膜方法において、前記薄膜中に含まれる炭素濃度を高めるために前記窒素含有ガスの分圧を、全圧の10%以下となるように設定して成膜工程を行うようにする。これにより、炭素濃度を十分に高くし、トランジスタのゲート電極の閾値を低減させる。

(もっと読む)

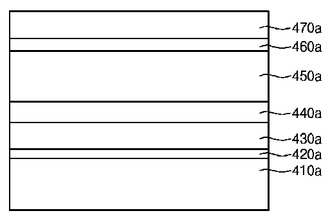

半導体装置及びその製造方法

【課題】高輝度の半導体装置およびその製造方法を提供することにある。【解決手段】絶縁性の成長基板上に形成された第1型の窒化物系クラッド層と、前記第1型の窒化物系クラッド層上に形成された多重量子井戸窒化物系活性層及び前記多重量子井戸窒化物系活性層上に形成された前記第1型と異なる第2型の窒化物系クラッド層と、を含む半導体装置が提供される。前記第1型の窒化物系クラッド層の下部及び前記第2型の窒化物系クラッド層の上部のうち、少なくとも一つには、トンネルジャンクション層が形成される。  (もっと読む)

(もっと読む)

ダイヤモンド素子及びその製造方法

【課題】通常の半導体材料に比べて、絶縁破壊電界が高く、熱伝導率が極めて良好で放熱性に優れ、化学的にも安定であり、またバンドギャップが大きいというダイヤモンド半導体の特性を最大限に活用するために、高温大気下、放射線下等の過酷な環境下でも動作ショットキー電極を備えたダイヤモンド素子及びその製造方法を提供する。

【解決手段】半導体ダイヤモンド表面上に、窒化物導電体からなるショットキー電極層を備えていることを特徴とするダイヤモンド素子。半導体ダイヤモンド表面上に、純金属、金属窒化物、金属珪化物、金属硼化物、金属炭化物から選択した一種以上の電極素子とその上に形成された窒化物導電体のキャップからなるショットキー電極層を備えていることを特徴とするダイヤモンド素子。

(もっと読む)

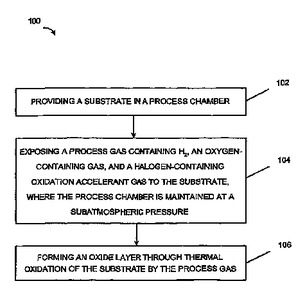

酸化膜の形成方法

基板上に酸化膜を形成する方法。当該方法は、H2、酸素含有ガス、ハロゲンを含有した酸化を促進するガスを含むプロセスガスを大気圧より低い圧力に維持して基板に曝露する工程、並びに、前記プロセスガスによる基板の熱酸化を介して酸化膜を形成する工程を有する。本発明の一の実施例によると、基板は約150℃から約900℃に維持されて良い。酸化膜を含む微細構造について記載されている。前記酸化膜は、高誘電率誘電体層と共に集積されたゲート誘電体酸化膜又は界面酸化膜であって良い。  (もっと読む)

(もっと読む)

電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス及びその製造方法

【課題】絶縁破壊電界が高く、熱伝導率が極めて良好で放熱性に優れ、化学的にも安定であり、またバンドギャップが大きいというダイヤモンド半導体の特性を最大限に活用するために、ダイヤモンドデバイスの電界集中による電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス及びその製造方法を提供する。

【解決手段】半導体ダイヤモンドの表面と電極の表面が同一面となるように、半導体ダイヤモンドに設けた溝に電極が埋め込まれた構造を有することを特徴とするダイヤモンドデバイスの電界集中による電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス。

(もっと読む)

半導体装置

【課題】本発明は、Fin型MISFETにおいて、Finの下部で生じるパンチスルーを抑制できるようにする。

【解決手段】たとえば、Si基板11の表面上には、素子領域となるFin12が設けられている。Fin12には、ソース・ドレイン拡散層23a,23bが形成されている。ソース・ドレイン拡散層23a,23bの相互間には、チャネル部が形成されている。このチャネル部に対応する、上記Fin12の一部を覆うようにしてゲート電極部21が設けられている。ゲート電極部21は、第1の仕事関数を有する第1のゲート電極21a上に、第1のゲート電極21aとは異なる、第2の仕事関数を有する第2のゲート電極21bを積層してなる構成とされている。

(もっと読む)

201 - 220 / 333

[ Back to top ]