Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

41 - 60 / 333

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含む半導体装置である。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

密着性を改良するための基板のプラズマアニーリング

【課題】許容可能な拡散バリア特性と基板への密着性を耐熱性金属窒化物が有するように、基板上への窒化チタンなどの耐熱性金属窒化物膜の形成を提供する。

【解決手段】材料の層が、ウェハ上に部分的に形成された集積回路内の基板上に形成される。基板はプラズマアニールを受け、その間に基板はイオンでボンバードされる(工程300)。プラズマアニールは、エネルギーを注入された窒素含有ガスから生成されたプラズマへ基板を曝すことにより実行できる。基板がプラズマアニールされた後、耐熱性金属窒化物の層が基板上に堆積される(工程301)。耐熱性金属窒化物の層は、次に、第1セットのイオンでボンバードされる。第1セットのイオンによる耐熱性金属のこのボンバードは、プラズマアニールを実行することにより達成できる。耐熱性金属窒化物は、更に、第2セットのイオンによりボンバードされる(工程302)。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体装置及びその作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】ゲート絶縁膜を間に挟んでゲート電極と重なっている酸化物半導体膜と、酸化物半導体膜に接するソース電極またはドレイン電極とを有しており、ソース電極またはドレイン電極は、チタン、マグネシウム、イットリウム、アルミニウム、タングステン、モリブデンなどの電気陰性度が低い金属のいずれか一つまたは複数を含む混合物、金属化合物または合金を含んでおり、ソース電極またはドレイン電極中の水素濃度は酸化物半導体膜中の水素濃度の1.2倍以上、好ましくは5倍以上である。

(もっと読む)

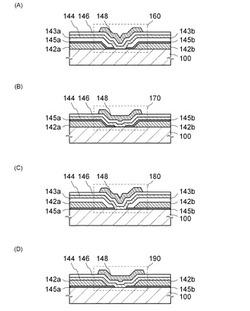

半導体装置及びその作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】p型MISトランジスタ及びn型MISトランジスタの特性を向上した相補型MISトランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、p型半導体領域10A及びn型半導体領域10Bを有する半導体基板101の上に、高誘電率膜106、アルミニウムからなる第1のキャップ膜107及びハードマスク108を順次形成する。次に、第1のキャップ膜107及びハードマスク108におけるn型半導体領域10Bの上に形成された部分を除去する。その後、半導体基板101の上に、実効仕事関数を低下させる効果を有する元素を含む第2のキャップ膜109を形成する。

(もっと読む)

PFETチャネルSiGeを有する金属ゲート及び高k誘電体デバイス

【課題】SiGeから成るチャネルを有し、金属ゲート及び高kゲート誘電体を有するPFETを提供する。

【解決手段】Si表面上にSiGe層10をエピタキシャル成長させ、SiGe層の上に、高k誘電体及び金属をブランケット配置し、ゲートスタックを形成した後、NFET側のゲート誘電体、及びSiGe層を除去し、第2の高k誘電体53及び第2の金属52を配置する。PFETは、SiGeチヤネル10の上の高k誘電体を有するゲート誘電体、金属を有するゲート及び、シリサイドを有するソース、ドレインから成る。NFETは、第2の高k誘電体53、第二の金属52を有するゲート及び、シリサイドを有するソース、ドレインからなる。基板表面上のエピタキシャルSiGe層は、PFETのチヤネルのみに形成される。PFET及びNFETデバイス・パラメータは、各ゲート誘電体及びゲートスタックの組成によって別個に最適化することができる。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】複数ゲートトランジスタの改良された構造、およびその製造プロセスの提供。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイス100は、第1のパラメータを有する少なくとも2つの第1のゲート電極を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料120の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素(SiC)半導体装置において、SiC基板との良好なオーミック特性が得られると共に、密着性および耐久性に優れた裏面電極を提供する。

【解決手段】SiC半導体装置は、SiC基板1の裏面に形成されたニッケル膜3を含む裏面電極11と、SiC基板1とニッケル膜3との間に介在し、開口部2aを有するバリア膜2とを備える。SiC基板1とニッケル膜3との間においては、バリア膜2の開口部2aの部分に、ニッケルシリサイドの反応層4が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体ゲート絶縁膜/メタルゲート電極のMOSトランジスタ構造において、メタルゲート電極側壁の酸化層を抑制し、トランジスタ駆動能力を改善する。

【解決手段】基板101上に、金属含有膜110を形成する工程(a)と、反応室内において金属含有膜にアンモニアラジカルを曝露する工程(b)と、反応室内に不活性ガスを供給し、工程(b)において生じたガスを排気する工程(c)と、工程(b)及び工程(c)を所定の回数繰り返した後に、大気曝露することなく、反応室内において金属含有膜110を覆うシリコン窒化膜100aを形成する工程(d)とを備える。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体発光素子、その製造方法、ランプ、電子機器及び機械装置

【課題】金属反射層の構成材料の拡散を防止することが可能な電極を備えた半導体発光素子、その製造方法、ランプ、電子機器及び機械装置を提供することを目的とする。

【解決手段】基板101と、基板101上にn型半導体層104と発光層105とp型半導体層106とがこの順序で積層されてなる積層半導体層20と、p型半導体層106に接合された一方の電極111と、n型半導体層104に接合された他方の電極108と、を具備する半導体発光素子であって、一方の電極111または他方の電極108のいずれか一方または両方が、第1の拡散防止層51と金属反射層52と第2の拡散防止層53がこの順序で積層されてなる構造を有し、かつ、第1の拡散防止層51がIn、Zn、Al、Ga、Ti、Bi、Mg、W、Ce、Sn、Niのいずれかの金属を含む酸化物からなる半導体発光素子1を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

高温でのIV族金属含有膜の堆積

IV族金属含有前駆体と、IV族金属含有膜{窒化物、酸化物および金属)の高い処理温度での堆積におけるその使用とを開示している。金属中心に結合したシクロペンタジエニル配位子およびイミド配位子の使用は熱安定性を確保し、広範な堆積温度ウィンドウおよび不純物の低い混入を可能にする。IV族金属(チタン、ジルコニウム、ハフニウム)含有膜の堆積は、熱および/またはプラズマ強化CVD、ALDおよびパルスCVDによって行うことができる。 (もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置の作製方法

【課題】特性の良い半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】基板上に、ゲート電極として機能する第1の導電層を形成する工程と、第1の導電層を覆うように第1の絶縁層を形成する工程と、第1の導電層と一部が重畳するように、第1の絶縁層上に半導体層を形成する工程と、半導体層と電気的に接続されるように第2の導電層を形成する工程と、半導体層および第2の導電層を覆う第2の絶縁層を形成する工程と、第2の導電層と電気的に接続される第3の導電層を形成する工程と、半導体層を形成する工程の後、第2の絶縁層を形成する工程の前の第1の熱処理工程と、第2の絶縁層を形成する工程の後の第2の熱処理工程と、を有する。

(もっと読む)

41 - 60 / 333

[ Back to top ]