Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

61 - 80 / 333

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

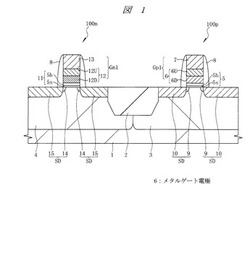

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

窒化物半導体装置および窒化物半導体装置製造方法

【課題】窒素不足に起因する移動度の低下を抑制し、窒素不足に起因するリーク電流を低減することができる窒化物半導体装置、その製造方法を提供する。

【解決手段】窒化物半導体装置1は、基板10と、バッファ層11と、窒化物半導体層(第1窒化物半導体層12、第2窒化物半導体層13、第3窒化物半導体層14)と、第1電極22と、第2電極23と、制御電極25とを備える。第1電極22と第2電極23との間で第3窒化物半導体層14の表面から第2窒化物半導体層13に渡って凹状に形成されたリセス部16を備え、リセス部16は、絶縁性窒化物で形成された窒化物絶縁膜17を備え、制御電極25は、導電性窒化物で形成され窒化物絶縁膜17(ゲート絶縁膜)に重ねて配置されている。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いた好適な構造のnチャネル型トランジスタおよびpチャネル型トランジスタを提供することを目的の一とする。

【解決手段】第1の酸化物半導体層と電気的に接続し、第1の材料を含む第1の導電層と第2の材料を含む第2の導電層の積層構造でなる第1のソース電極またはドレイン電極と、第2の酸化物半導体層と電気的に接続し、第1の材料を含む第3の導電層と第2の材料を含む第4の導電層の積層構造でなる第2のソース電極またはドレイン電極と、を有し、第1の酸化物半導体層には、第1のソース電極またはドレイン電極の第1の導電層が接触し、第2の酸化物半導体層には、第2のソース電極またはドレイン電極の第3の導電層および第4の導電層が接触する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置

【課題】メタル電極/high−kゲート絶縁膜からなるゲート構造において、半導体特性や信頼性の劣化をおこさせることなく、サイドウォールを形成したゲート構造を有する半導体装置の提供。

【解決手段】半導体基板1上に設けられた、high−k誘電体材料からなるゲート絶縁膜2と、ゲート絶縁膜2の上に設けられたメタル電極3と、メタル電極3の側壁を覆い、ゲート絶縁膜2を挟んで半導体基板1と対向配置された酸化防止膜4と、ゲート絶縁膜2と酸化防止膜4とを覆うように、半導体基板上に設けられたサイドウォール5とを含むゲート構造。

(もっと読む)

論理回路及び半導体装置

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置、その半導体装置の作製方法及びその半導体装置を有する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタにおいて、電界効果移動度を向上させることを課題の一とする。また、薄膜トランジスタの電界効果移動度を向上させても、オフ電流の増大を抑制することを課題の一とする。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とゲート絶縁層の間に、該酸化物半導体層より導電率が高い酸化物クラスターを形成することによって、該薄膜トランジスタの電界効果移動度を向上させ、且つオフ電流の増大を抑制することができる。

(もっと読む)

導電材料の誘電体層上へのプラズマ増強原子層堆積

プラズマ増強原子層堆積(PEALD)を使用して誘電体層上に導電性の金属層を形成する方法を、関連する組成物および構造と共に提供する。PEALDによって導電層を堆積する前に、非プラズマ原子層堆積(ALD)プロセスによって誘電体層上にプラズマバリア層を堆積する。プラズマバリア層は、誘電体層上のPEALDプロセスにおけるプラズマ反応物質の有害作用を減少させるか、または防止し、接着を増強することができる。非プラズマALDプロセスおよびPEALDプロセスの双方において、同じ金属反応物質を使用することができる。 (もっと読む)

半導体装置の製造方法

【課題】 ハフニウムシリケートからなるゲート絶縁膜に、アルミナ膜を重ねると、等価酸化膜厚を薄くすることが困難になる。また、ハフニウムシリケートからなるゲート絶縁膜内にAlが拡散すると、正孔の移動度が低下してしまう。

【解決手段】 半導体基板(10)の上に、HfとOとを含む絶縁膜(16)を形成する。この絶縁膜の上に、構成元素として酸素とチタンとを含むキャップ膜(17)を形成する。絶縁膜及びキャップ膜を、窒素ガスまたは希ガス雰囲気中で熱処理し、キャップ膜中のチタンを絶縁膜内に拡散させることにより、ゲート絶縁膜(18)を形成する。ゲート絶縁膜の上に、ゲート電極膜(19)を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】、配線層とその下層のプラグ層との配線抵抗を抑えながら下層のプラグの埋め込み性を向上させることが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Cu配線10と、Cu配線10の下層側でCu配線10と接触して接続されるCuプラグ20と、Cuプラグ20の底面側及び側面側に配置された、Cuに対してバリア性を有するBM膜240と、Cu配線10とCuプラグ20との内Cuプラグ20側に選択的に、かつCuプラグ20とBM膜240との間に介在するように配置された、BM膜240よりも前記導電性材料に対して濡れ性が高いRu膜242と、Cu配線10とCuプラグ20とが接触する箇所を少なくとも除くCu配線10の底面側と、Cu配線10の側面側とに配置された、Cuに対してバリア性を有するBM膜244と、を備えたことを特徴とする。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】III族窒化物半導体層と接続電極との接合性および電極の信頼性を向上させる。

【解決手段】半導体発光素子1は、基板110と、発光層150を含み基板110上に積層される積層半導体層100と、インジウム酸化物を含み積層半導体層100上に積層される透明電極170と、透明電極170上に積層される第1の接合層190と、第1の接合層190上に積層されて外部との電気的な接続に用いられる第1のボンディングパッド電極200とを備える。また、半導体発光素子1は、弁作用金属の一種であるタンタルを含むとともにnコンタクト層の半導体層露出面140cと接する側がタンタル酸化物あるいはタンタル窒化物層となるように積層される第2の接合層220と、第2の接合層220上に積層されて外部との電気的な接続に用いられる接続電極の一例としての第2のボンディングパッド電極230とを備えている。

(もっと読む)

駆動回路及び表示装置

【課題】酸化物半導体にチャネル形成領域を設ける薄膜トランジスタで構成された駆動回路を有する表示装置において、回路が占める面積を大きくすることなく、薄膜トランジスタのしきい値電圧のシフトを低減し、且つ薄膜トランジスタをオフにした際にソースとドレインの間を流れる電流を低減する。

【解決手段】複数のインバータ回路及び複数のスイッチを有し、インバータ回路は、第1の酸化物半導体膜を有する第1の薄膜トランジスタと、第2の酸化物半導体膜を有する第2のトランジスタと、を有し、第1の薄膜トランジスタ及び第2の薄膜トランジスタは、エンハンスメント型であり、第1の酸化物半導体膜及び第2の酸化物半導体膜上に接してOH基を有する酸化珪素膜が設けられ、酸化珪素膜上に接して窒化珪素膜が設ける。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】薄膜トランジスタを有する半導体装置において、薄膜トランジスタの半導体層を、金属元素が添加された酸化物半導体層とする。金属元素として鉄、ニッケル、コバルト、銅、金、モリブデン、タングステン、ニオブ、及びタンタルの少なくとも一種類以上の金属元素を用いる。また、酸化物半導体層はインジウム、ガリウム、及び亜鉛を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】nMOS及びpMOSの双方において低い閾値電圧を実現することができ、製造コストが低い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上の全面にシリコン酸窒化膜5を形成し、シリコン酸窒化膜5上にランタン酸化膜6を形成し、pMOS領域RpMOSからランタン酸化膜6を除去する。次に、全面に高誘電率膜である窒化ハフニウムシリケイト膜7を形成し、アルミニウム含有窒化チタン膜8を形成し、ポリシリコン膜9を形成し、これらの積層膜をゲート電極形状に加工する。次に、ソース・ドレイン領域12及び13に不純物を導入し、これらの不純物を活性化させるアニール処理を利用して、アルミニウム含有窒化チタン膜8中に含まれるアルミニウムを、pMOS領域RpMOSにおけるシリコン酸窒化膜5と窒化ハフニウムシリケイト膜7との界面まで拡散させる。

(もっと読む)

61 - 80 / 333

[ Back to top ]