Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

81 - 100 / 333

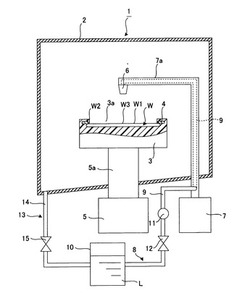

めっき装置、めっき方法および半導体装置の製造方法

【課題】めっき膜における膜厚の均一性を向上させることができるめっき装置およびめっき方法、ならびに配線不良を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、基板Wの被めっき面W1が上向きとなるように基板Wを保持しつつ基板Wを回転させるホルダ3と、ホルダ3で保持された基板Wの周縁部W2に接触するカソード4と、ホルダ3で保持された基板Wの中央部W3に向けてめっき液Lを吐出し、かつアノードとしても機能するノズル6とを具備することを特徴とする、めっき装置1が提供される。

(もっと読む)

半導体装置の作製方法

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチング工程は、エッチングガスによるドライエッチングを用いる。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備え、占有面積が小さい保護回路等が必要となる。

【解決手段】ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と端部が重畳する第1配線層及び第2配線層と、少なくともゲート電極と重畳しゲート絶縁膜及び該第1配線層及び該第2配線層における導電層の側面部及び上面部と接する酸化物半導体層とを有する非線形素子を用いて保護回路を構成する。非線形素子のゲート電極は走査線又は信号線と接続され、非線形素子の第1配線層又は第2配線層がゲート電極の電位が印加されるようにゲート電極層と直接接続されていることで、接続抵抗の低減による安定動作と接続部分の占有面積を縮小する。

(もっと読む)

表示装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一とする。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置において、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二種類の酸化物半導体層とを組み合わせて構成され、ゲート電極層と重なるチャネル形成領域となる半導体層上にチャネル保護層が設けられた逆スタガ型薄膜トランジスタが設けられた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続するパッド部が設けられている。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置の製造方法

【課題】凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

化学気相成長材料および化学気相成長方法

【課題】 残留不純物の少ない良質なルテニウム膜を得ることができる化学的気相成長材料及びその化学的気相成長材料を用いてルテニウム膜を形成する簡易な方法の提供。

【解決手段】

テトラ(μ−トリフルオロアセタト)ジ(アセトン)ジルテニウム、テトラ(μ−ペンタフルオロプロピオナト)ジ(アセトン)ジルテニウムの如きルテニウム化合物と、溶媒とを含む化学気相成長材料、および該化学気相成長材料を用いた化学気相成長方法。

(もっと読む)

窒化物半導体発光素子

【課題】p側電極として透明導電層膜材料からなる透光性の電極を用いた窒化物半導体発光素子における光取り出し効率を改善し、発光効率が向上された窒化物半導体発光素子を提供することを目的とする。

【解決手段】本発明に係る窒化物半導体発光素子は、第一の主面および第二の主面を有する窒化物半導体の積層体であって、n型窒化物半導体層とp型窒化物半導体層とで発光層を挟んだpn接合ダイオード構造を、上記p型窒化物半導体層が上記第一の主面側となるように含む積層体と、上記積層体の第一の主面を覆うように形成された透明導電膜材料からなる透光性の電極とを有し、上記透光性の電極の表面には上記発光層で発生される光を散乱または回折する凹凸が形成されることを特徴とする。

(もっと読む)

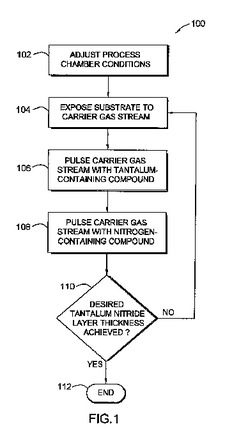

インサイチュチャンバ処理および堆積プロセス

本発明の実施形態は、原子層堆積(ALD)または化学気相堆積(CVD)などの気相堆積プロセス中に、プロセッシングチャンバの内面を処理し、材料を堆積させる方法を提供する。一実施形態では、前処理プロセス中に、プロセッシングチャンバの内面および基板を、水素化配位子化合物などの試薬にさらすことができる。この水素化配位子化合物は、次の堆積プロセス中に使用される有機金属前駆体から形成される遊離配位子と同じ配位子とすることができる。この遊離配位子は、堆積プロセス中に、通常、水素化または熱分解によって形成される。一例では、プロセッシングチャンバおよび基板は、ペンタキス(ジメチルアミノ)タンタル(PDMAT)などのアルキルアミノ配位子を有する有機金属化学前駆体を利用した気相堆積プロセスを行う前に、前処理プロセス中に、アルキルアミン化合物(例えば、ジメチルアミン)にさらされる。  (もっと読む)

(もっと読む)

化合物半導体装置およびその製造方法

【課題】耐湿性を向上することのできる化合物半導体装置およびその製造方法を提供する。

【解決手段】化合物半導体装置は、オーミック電極OMEa〜OMEdと、絶縁膜ILと、金を含む配線IC1a〜IC1dと、金を含む配線IC2a〜IC2dとを備えている。絶縁膜ILはオーミック電極OMEa〜OMEdの一部上に形成されている。配線IC1a〜IC1dは、オーミック電極OMEa〜OMEd上で絶縁膜ILが形成されていない部分であって、絶縁膜ILの側面に接触する位置に形成されている。配線IC2a〜IC2dは、絶縁膜IL上および配線IC1a〜IC1d上に形成されている。

(もっと読む)

半導体加工方法

【課題】high−k膜/メタルゲート構造を有する半導体素子のドライエッチングにおいて、メタルゲート部分を垂直にエッチングする。

【解決手段】減圧処理室204と、該減圧処理室に処理ガスを供給するガス供給手段と、前記減圧処理室内に、半導体基板を載置して保持する試料台205と、前記減圧処理室に供給された処理ガスに高周波エネルギを供給してプラズマを生成するプラズマ生成手段を備え、生成したプラズマにより前記半導体基板にプラズマエッチング処理を施す半導体加工方法において、前記試料台上に、HfあるいはZrを含む高誘電率絶縁膜、TiあるいはTaを含む仕事関数制御金属導体膜、およびレジストを順次形成した半導体基板206を載置し、前記レジストを用いて前記導体膜をエッチング加工するに際して、前記試料台にオンオフ変調された基板バイアス電圧を印加する。

(もっと読む)

半導体装置の製造方法

【課題】仕事関数金属膜と低抵抗膜とで構成されたゲート電極をプラズマエッチングする際に、膜質に応じたエッチングステップの切り替えの遅延を防ぐ。

【解決手段】低抵抗膜6中であって、仕事関数金属膜4との界面の近傍に、プラズマ発光モニタに感度のある、窒素を含む進捗モニタ層5を設けることで、エッチング中のプラズマ発光の変化を検知し、エッチングの進捗をモニタすることでエッチングステップ切り替えの遅延を防止することができる。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

バリア蒸着のための液相分子自己組織化および形成構造

マイクロ電子構造を形成する方法及びその形成構造について記載する。無水溶媒に金属前躯体を溶液槽にて溶解し、配線開口を有する基板を溶液槽に配置して、金属前躯体により配線開口内に単分子層を形成する。また、基板を共反応体の混合液中に配置して、共反応体と金属前躯体とを反応させて薄いバリア層を形成する。 (もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供する。

【解決手段】第1メタルキャップ膜MC1と第2メタルキャップ膜MC2とが成膜される際に、まず基板Sの表面に水素ラジカルが供給されて、表面処理である微粒子のエッチング処理や未結合手への末端処理、さらには酸化層の還元処理が実行される。そして、この表面処理が基板Sに施された後、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給されて、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2である硼窒化ジルコニウム膜が成膜される。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】多層配線構造における硼窒化ジルコニウム膜の耐酸化性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供する。

【解決手段】絶縁膜と前記絶縁膜に囲まれた金属膜とが露出する基板を加熱した状態で収容する成膜室31Sと、Zr(BH4)4と励起した窒素とを前記成膜室31Sへ供給して加熱下である基板Sの表面に硼窒化ジルコニウム膜を成膜する成膜部とを備えた半導体装置の製造装置であって、前記成膜部が、成膜時間が経過するに連れて前記励起した窒素の供給量を低くすることを要旨とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

81 - 100 / 333

[ Back to top ]